# APPLICATION HANDBOOK **PRODUCT** FEATURES & APPLICATION INSIGHTS

Design Engineer's Guide

nexperia

# Logic Application Handbook

Product Features and Application Insights

Design Engineer's Guide

## **Contributors**

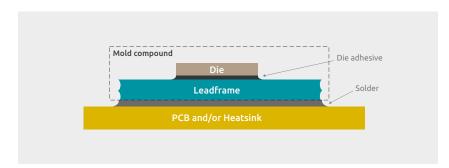

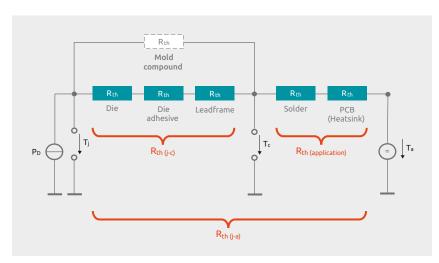

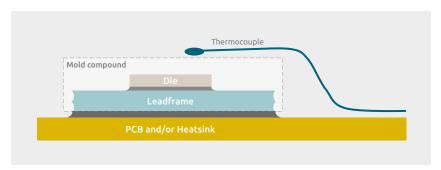

Christian Backhaus

Burkhard Laue

Michael Lyons

Thomas Wolf

Ashish Jha

Ghislaine Jilisen Janssen

Sven Walczyk

Vikram Singh Parihar

Robby Ferdinandus

Roland Peters

Olaf Vogt

Logic Application Handbook Product Features and Application Insights Design Engineer's Guide

Copyright © Nexperia October 2020

#### www.nexperia.com

ISBN 978-0-9934854-6-6

All rights reserved.

No part of this publication may be reproduced or distributed in any form or by any means without the prior written permission of the author.

| Introduction                                           |  |

|--------------------------------------------------------|--|

| Logic basics, Generic Logic product properties         |  |

| Power considerations for CMOS and BiCMOS logic devices |  |

| Timing aspects of discrete devices                     |  |

| Interfacing aspects of logic devices                   |  |

| Analog and Logic Product Segmentation                  |  |

| Packages                                               |  |

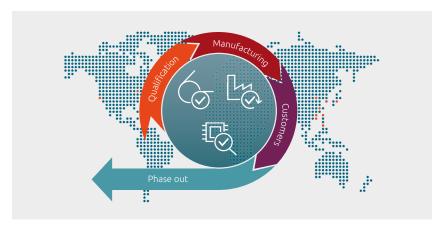

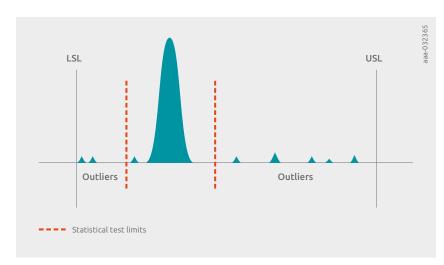

| Automotive Quality                                     |  |

| Logic Families                                         |  |

| FAQ                                                    |  |

|                                                        |  |

|                                                        |  |

|                                                        |  |

|                                                        |  |

|                                                        |  |

| Appendix                                               |  |

| Abbreviations                                          |  |

| Index                                                  |  |

| Legal information                                      |  |

|                                                        |  |

### **Preface**

Nexperia is a leading expert in diodes, bipolar transistors, ESD protection devices, MOSFETs, GaN FETs and analog & logic ICs.

With an absolute focus on efficiency, Nexperia consistently produces the essential semiconductors required by every electronic design in the world: more than 90 billion annually. Products that are benchmarks in efficiency—in process, size, power and performance—with industry-leading small packages that save valuable energy and space.

Our extensive portfolio of standard functions meets both the demands of today's state-of-the art applications and the stringent standards set by the Automotive Industry. Through our continued efforts in innovation, reliability and support, we maintain the leading position in all our key product segments: Diodes and Transistors, ESD protection, MOSFETs, and Analog and Logic ICs. We develop and deliver benchmark solutions for today's and tomorrow's market requirements, drawing on a heritage of over 60 years' expertise in Semiconductors as the former Standard Products divisions of NXP and Philips.

Our successful record in innovation is the result of varied yet streamlined R&D. We combine the latest technologies with efficient processes, helping us to serve the world's most demanding industries with world-class products.

#### Nexperia Design Engineer's Guides:

Our program of Design Engineer's Guides has one key goal: We want to share our Expertise with you and help you to optimize your electronic designs. It is a collection of technical and application insights "from Engineer to Engineer".

The first Nexperia Design Engineers Guide, released in 2017, is our *MOSFET Application Handbook*. In this handbook, our engineers focus on how to use MOSFETs in specific applications and what the key and critical MOSFET parameters are, considering aspects like thermal conditions etc.

The Second Technical Guide of this series was launched in 2018: Our ESD Application Handbook. This ESD Application Handbook is focusing on Protection Concepts, Testing and Simulation for Modern Interfaces. We got so far a lot of positive feedback by our Engineering Community from Customers representing all Industries word wide. In addition to this ESD Application Handbook, Nexperia is also offering on-site Technical ESD Seminars to share our insights with our customers, cross all relevant applications like Automotive, Mobile Communication, Consumer, Computing and Industrial. At the end we want to help minimize the risk of ESD

damage—supporting the design community in protecting applications and products against ESD issues. Both Design Engineer's Guides are also available in Chinese Version.

#### Introducing the Logic Application Handbook

"Why a Logic Handbook?" You may ask. Well, even though logic may have been around since the days when engineers still used slide rules, today logic is still an essential part of many embedded designs.

Of course, it is the go-to resource for I/O expansion and interfacing between analog and digital domains, but in many ways, today's designers need logic more than ever. Why? Because today's systems need to be smaller, more power efficient, and more portable than ever before. That means managing tight layouts, and dealing with looped traces, which can generate cross-talk and create signal-integrity issues. It also means working with multi-layer boards, implementing real-time responses to real-world events, and supporting multitasking operations. In many cases, the right logic device makes these things easier to manage, and helps optimize operation.

In fact, while Logic is great for making these kind of minor modifications and fine-tuning performance in the later design stages, that's not all it can do! Today's logic devices let developers add features and improve functionality, so they can meet their design requirements right from the start, even before they need to think about last-minute revisions.

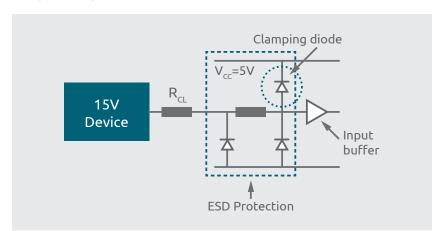

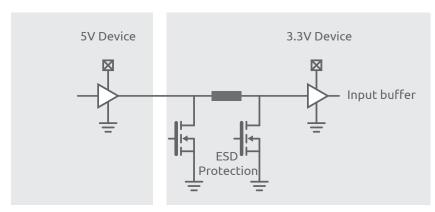

- In systems that use application-specific integrated circuits (ASICs), logic gates can be used to provide control or "glue" functions. Modern logic families include features, such as overvoltage tolerance, that enable them to be used as glue logic between ASICs that use different supply voltages. In some cases, this can extend the lifetime of legacy ASICs.

- In systems that use a microcontroller (MCU), logic products are used for low-cost I/O expansion. Shift registers are used for digital I/O expansion, and analog switches are used to multiplex analog sensor inputs. The combination of the two enables the selection of lower-pin count MCUs with fewer analog-to-digital converters. When used this way, standard logic enables true cost optimization of an application.

- In tablets and laptops, logic can be used for battery charging and discharging blocks, and to provide standby mode, power-down, and start-up control sequences. In docking stations and systems that support multiple displays, logic provides the bus switches, resets, and audio blocks that reduce the impact of noisy signals, and can be used to buffer the clock and data signals.

- In mobile devices such as smartphones, tablets, and cameras, logic provides multiplexing, buffering, and level-translation functions for the baseband, RF interfaces, memory, and other peripherals.

- In external speakers and other high-end audio equipment logic buffers are used to buffer the clock, sync, and data signals sent to the audio interface and docking station.

Over the last 60 years, Nexperia—starting as Philips Semiconductors and then incorporating the experience of Signetics—has supported growing global demand for logic. Today, as the No. 1 volume logic supplier in the world, Nexperia offers a broad variety of industry-leading solutions proudly serving customers across a variety of market segments. Our reputation as a trusted supplier of exceptionally high quality is reinforced by our No. 1 position in the automotive industry.

We proudly invite you to study our 3rd Nexperia Design Engineer's Guide, our *Logic Application Handbook*. The Table of Content makes it easy for you to navigate to the key chapters of interest. This book is another key milestone to build the Technical Nexperia Encyclopedia.

#### Olaf Vogt

Director Application Marketing, Nexperia

# **Robby Ferdinandus**Global Head of Marketing.

Global Head of Marki Nexperia

|       |  | <br> |  |

|-------|--|------|--|

| ogic. |  |      |  |

|       |  |      |  |

# **Table of Contents**

| Chapter<br>Introdu          | 1 ction                                             | 18       |

|-----------------------------|-----------------------------------------------------|----------|

| Chapter<br><b>Logic b</b> a | 2<br>asics, Generic Logic product properties        |          |

| 2.1                         | Basic logic gate functions                          | 25<br>26 |

| 2.2                         | Storage elements                                    | 32       |

| 2.4                         | Switches                                            | 33       |

| 2.5                         | Logic data sheet parameters                         | 34       |

| 2.6                         | Limiting values                                     | 35       |

| 2.7                         | Recommended operating conditions                    | 35       |

| 2.8                         | Static characteristics                              | 36       |

| 2.9                         | Dynamic characteristics                             | 38       |

|                             | 3<br>considerations for CMOS and<br>5 logic devices |          |

| 3.1                         | Static considerations                               | 42       |

| 3.2                         | Dynamic considerations                              | 44       |

| 3.2.1                       | Duty cycle considerations with unbalanced outputs   | 46       |

| 3.2.2                       | Power dissipation due to slow input rise/fall times | 46       |

| 3.2.3                       | Process family related dynamic power dissipation    | 47       |

| 3.3                         | Power dissipation capacitance                       | 48       |

| 3.4                         | Using CPD to calculate power dissipation            | 51       |

| 3.4.1                       | CMOS Device Calculation                             | 51       |

| 3.4.2                       | BiCMOS Device Calculation                           | 52       |

| 3.5                         | Results and conclusion                              | 53       |

#### Logic Application Handbook

| Chapte   |                                                   |    | 6.3       | Synchronous Logic                                                      |

|----------|---------------------------------------------------|----|-----------|------------------------------------------------------------------------|

| Timing   | aspects of discrete devices                       |    | 6.3.1     | Flip Flops                                                             |

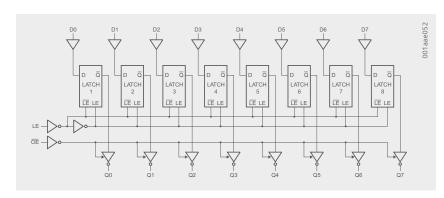

| 4.1      | Synchronous and asynchronous logic                | 58 | 6.3.2     | Latch or D-flipflop with level controlled enable                       |

| 4.2      | Propagation delay time of a device                |    | 6.3.3     | Edge triggered flipflops and registers                                 |

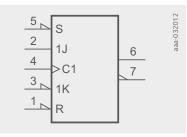

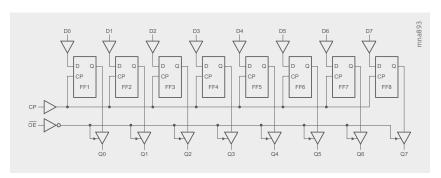

| 4.3      | Timing parameters of Flip Flops and Latches       |    | 6.3.4     | Edge-controlled D-Flipflop                                             |

| 4.4      | Skew definitions.                                 |    | 6.3.5     | JK-Flipflop                                                            |

| 4.4.1    | Output Skew tSK(o).                               |    | 6.3.6     | Parallel-Registers                                                     |

| 4.4.2    | Process Skew tSK(x)                               |    | 6.3.7     | FIFO Registers                                                         |

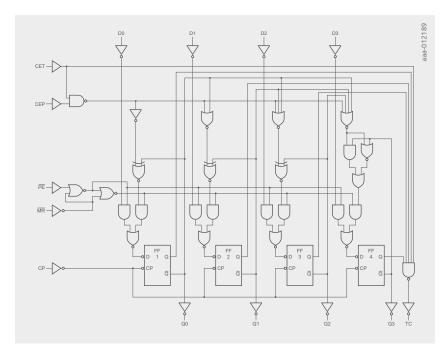

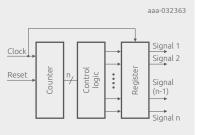

| 4.4.3    | Pulse Skew tSK(p)                                 |    | 6.3.8     | Counters                                                               |

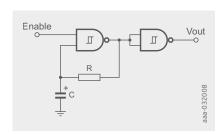

| 4.5      | Meta stability and its mitigation                 |    | 6.3.9     | Monostable Multivibrator                                               |

| 4.6      | Maximum frequency information                     |    | 6.4       | Where to use Synchronous Interface Logic                               |

| Chapte   | - 5                                               |    | Chapter   | 7                                                                      |

|          | cing aspects of logic devices                     |    | Package   | <b>S</b>                                                               |

| ilicerra | cing aspects of togic devices                     |    | 7.1       | Standard Logic Packages                                                |

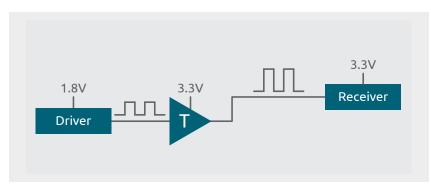

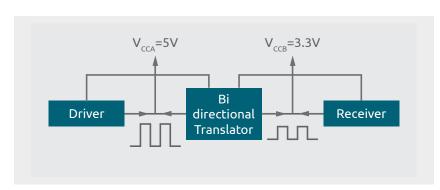

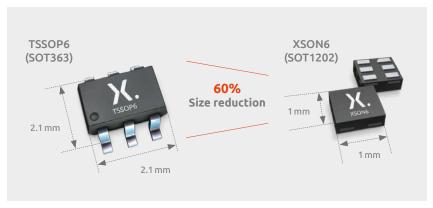

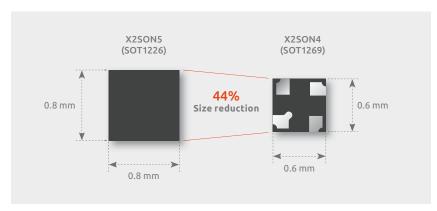

| 5.1      | Application requirements for interfacing          | 66 | 7.1       | Mini Logic Packages                                                    |

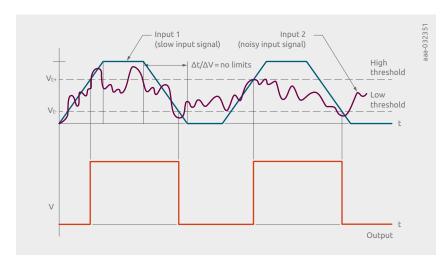

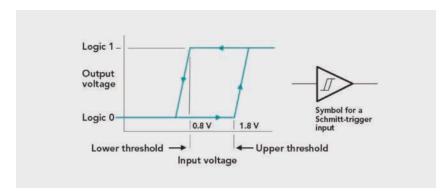

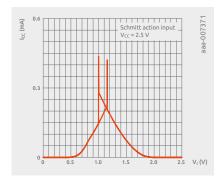

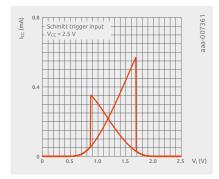

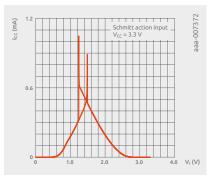

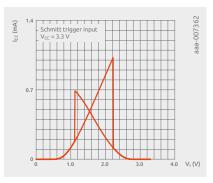

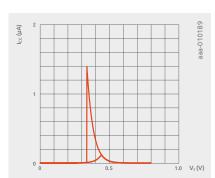

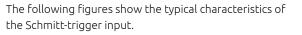

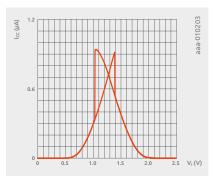

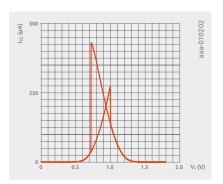

| 5.2      | Schmitt Trigger inputs                            | 77 | 7.2.1     | MicroPak (Extremely thin small outline no-leads)                       |

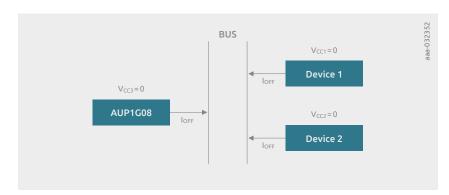

| 5.3      | I <sub>OFF</sub> mechanism and purpose            | 79 | 7.2.1     | PicoGate (Single, dual or triple gate functions in small packages) 137 |

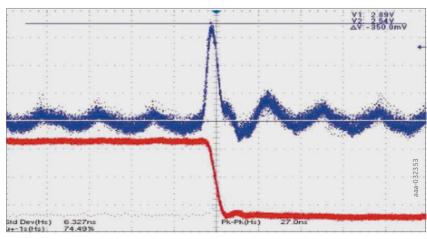

| 5.4      | Ground and VCC bounce                             | 80 | 7.2.3     |                                                                        |

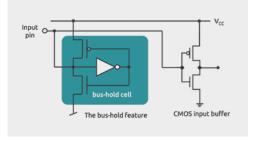

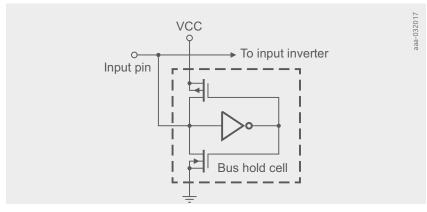

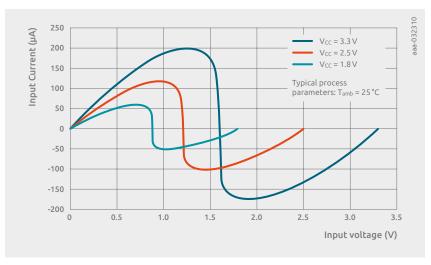

| 5.5      | Bus Hold                                          | 82 |           | Leads (PicoGate) or no leads (MicroPak)?                               |

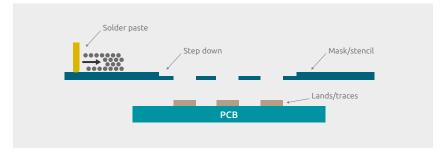

| 5.6      | Source Termination                                | 84 | 7.3       | Package soldering aspects                                              |

|          |                                                   |    | 7.4       | Thermal Resistance of packages                                         |

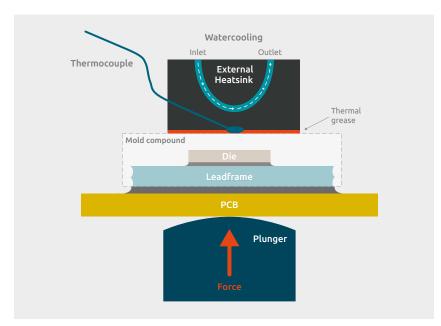

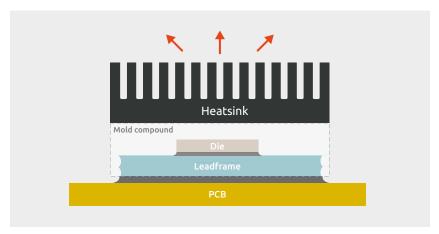

| Chapte   | r 6                                               |    | 7.5       | Thermal characterization of packages –                                 |

| Analog   | and Logic Product Segmentation                    |    |           | Explanation and possible setup                                         |

| 6.1      | Analog ICs                                        | 90 | Chapter 8 | 3                                                                      |

| 6.2      | Asynchronous Interface Logic                      | 93 | Automo    | tive Quality                                                           |

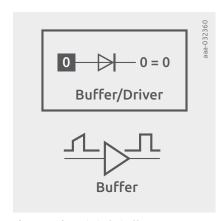

| 6.2.1    | Buffers, Drivers, Inverters                       | 93 |           |                                                                        |

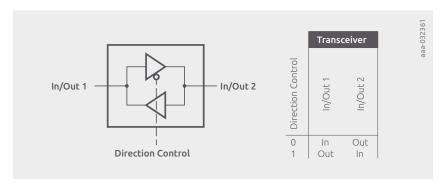

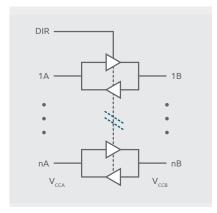

| 6.2.2    | Transceivers                                      | 94 | Cl. I     | 0                                                                      |

| 6.2.3    | Schmitt-Triggers                                  | 95 | Chapter ! |                                                                        |

| 6.2.4    | Voltage Translators                               | 96 | Logic Fa  | <b>milies</b>                                                          |

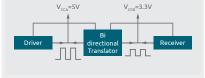

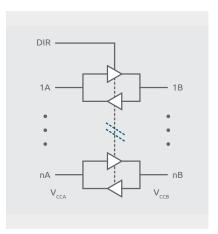

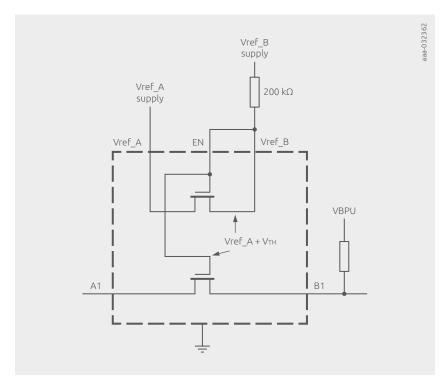

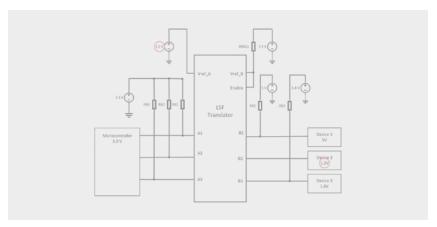

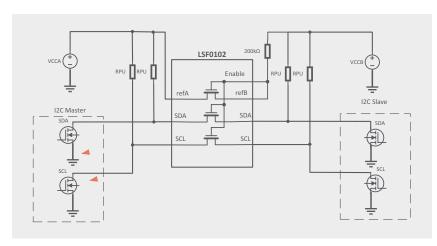

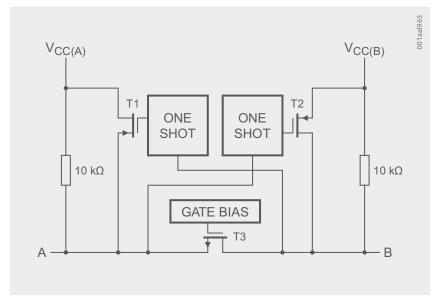

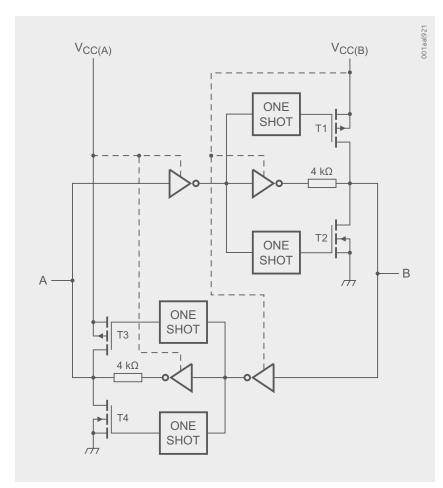

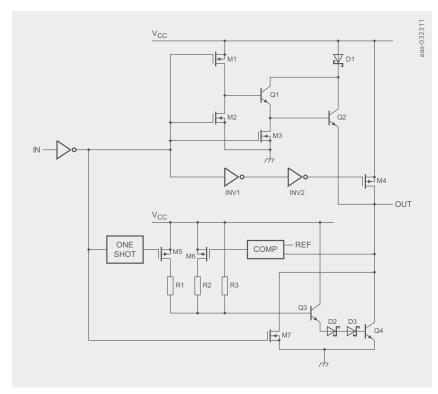

| 6.2.5    | Bi-directional translation with automatic sensing |    | 9.1       | The HC/HCT/HCU Logic Family                                            |

|          |                                                   |    | 9.2       | The AHC/AHCT Logic Family                                              |

|          |                                                   |    | 9.3       | The LVC Logic Family                                                   |

|          |                                                   |    | 9.4       | The AVC Logic Family                                                   |

|          |                                                   |    | 9.5       | The AUP Logic Family                                                   |

|          |                                                   |    | 9.6       | The AXP Logic Family                                                   |

9.7

#### nexperia | Design Engineer's Guide

#### Chapter 10

| FAQs              | 25 |

|-------------------|----|

| Appendix          | 27 |

| Abbreviations     | 30 |

| Index             | 30 |

| Legal information | 30 |

# Chapter 1 Introduction

Nexperia logic history begins with some of the very first integrated logic devices in the 1970's with the acquisition of Signetics. Nexperia technology is built upon decades of logic development and research over the years from Signetics, Philips, NXP and Nexperia.

Nexperia's logic portfolio is already very extended and will grow further. A general document for supporting the application of discrete logic devices, covering all important aspects of applications design, is very useful for engineers and helps to establish a common understanding for both Nexperia and the customers.

This handbook is dedicated to application and design engineers who are developing and using electronic circuits, often within embedded systems for all kind of applications. The demand for discrete logic devices is widespread. Many aspects of system and board design have to be addressed and the usage of logic devices is very often generating questions and support requirements which cannot be met just by data sheets. In order to provide a compact and handy document, condensed from application notes, customer support experience and general logic knowledge, this book is meant to support development engineers who are dealing with logic devices.

Digital systems are running at faster speeds, operating at lower voltages, and they are becoming more integrated. Many functions can be integrated into FPGAs or ASICs/SOCs, however, this does not mean that generic standard logic will disappear. Designers may choose to design with standard logic for the following reasons:

- The addition of features in next generation products with lower power consumption

- Space constraints requiring small packaging

- · Bus driving capability

- Interfacing between mixed voltage systems and voltage level translation

- Need for hot insertion capability

- · Need for bus switching.

- Need for I/O expansion of embedded systems

To create a content suitable for application engineers using Nexperia's logic devices, we are trying to take the designers point of view.

Each chapter of the book is addressing aspects of designing with logic devices and the systems they are used in. We start with basics of logic theory and circuit elements: logic equations, binary code and basic logic functions are introduced as well as circuit design aspects like CMOS gate implementations. The explanation of data sheet items is addressed and the associated properties of logic process families.

Another aspect is the power consumption of logic devices in embedded circuits, here we provide the calculation methods and explain the dependencies on process technology and topology.

As well as power, timing behavior needs to be calculated and must be understood for a circuit design. In the timing chapter, we deliver information and explanations for this.

Many behavioral aspects of logic devices need to be addressed when using them interfacing other devices. These effects are explained in the chapter Interfacing Aspects.

Background information about package types, soldering and footprints are provided in an extra chapter Package. For further system integration items like Simulation of PCB design we have created an extra chapter to enable users to successfully integrate Nexperia's logic devices into their embedded systems and verify the system before production.

The logic process families and their specific properties are addressed in another chapter with information about I/O characteristics and all technology specific information useful for selecting the suitable process family for a dedicated function.

Finally, frequently asked questions from customers are compiled in a chapter to address the most popular support issues.

# Chapter 2

Logic basics, Generic Logic product properties Logic basics, Generic Logic product properties

nexperia | Design Engineer's Guide

#### Binary code

The binary numeral system is a positional numeral system with a base or radix of 2. The single digits in a binary system are represented by  $2^n$  with  $n \ge 0 \rightarrow 2^0$ ,  $2^1$ ,  $2^2$ ,  $2^3$ , 2<sup>4</sup>..., in decimal = 1, 2, 4, 8, 16...

Below an example how a decimal number is converted to a binary number:

$$1317_{(10)} = 1 * 2^{10} + 0 * 2^9 + 1 * 2^8 + 0 * 2^7 + 0 * 2^6 + 1 * 2^5 + 0 * 2^4 + 0 * 2^3 + 1 * 2^2 + 0 * 2^1 + 1 * 2^0$$

$$1317_{(10)} = 10100100101_{(2)}$$

Each digit of a binary number is referred to as bit in logic nomenclature. Standard calculations like adding, subtraction, multiplication and division work identical to decimal system. For example adding two numbers the digits can be added sequentially while taking care of carry bits from the single operations.

Below the example of adding 1011 plus 0011 (decimal: 11+3). Starting from the lowest bit 1+1 is 0 plus a carry of 1 to the next digit. 1+1+1 is 1 plus a carry again. In the next digit there is the 1 of the carry plus 0, so 1 as result. For the highest digit 1 + 0 delivers 1.

Carry bits

$$\begin{array}{c}

1011 \\

+0011 \\

& \downarrow 11 \\

1110

\end{array}$$

#### Boolean Algebra

For elementary algebra expressions are noted down in numbers normally. In Boolean algebra the truth values false and true are used. These values can also be denoted with bits or binary digits, represented by logical 0 or 1.

Basic Operations in Boolean algebra are the AND and OR operation as depicted in Table 1. The AND operation delivers a true or 1 as result if all input values are equal 1. For the two input variable example both A and B need to be equal 1 for a result of 1, all other combinations deliver the result 0.

For the OR operation, all inputs need to be 0 to get a 0 as result. If at least one input variable is 1 or true, the OR operation delivers a 1.

Table 1: Basic Boolean operations AND and OR with 2 input values A and B

|   |   | AND | OR               |

|---|---|-----|------------------|

| Α | В | A^B | A <sup>∨</sup> B |

| 0 | 0 | 0   | 0                |

| 0 | 1 | 0   | 1                |

| 1 | 0 | 0   | 1                |

| 1 | 1 | 1   | 1                |

The AND and OR operation works in the same way if more than 2 variables are involved.

An additional very important Boolean operation is the inversion. It is quite simple as Table 2 shows. A zero input variable results in a result of 1 and vice versa for a 1 as input.

Table 2: Boolean operation of Inversion

| Α | Ā |

|---|---|

| 0 | 1 |

| 1 | 0 |

Boolean algebra is identical for many rules if the operation ' (OR operation) is replaced by an addition and the operation ' (AND operation) by a multiplication. The following laws known from normal algebra are common with Boolean algebra and called the monotone laws.

Associativity of  $^{\wedge}$  ... ...  $A^{\wedge}(B^{\wedge}C) = (A^{\wedge}B)^{\wedge}C$ Associativity of  $^{\vee}$  ... ...  $A^{\vee}(B^{\vee}C) = (A^{\vee}B)^{\vee}C$ Commutativity of  $^{\wedge}$  ... ...  $A^{\wedge}B = B^{\wedge}A$ Commutativity of  $^{\vee}$  ... ...  $A^{\wedge}B = B^{\vee}A$

Distributivity of  $^{\circ}$  over  $^{\vee}$  . . . . . . . . . .  $A^{\circ}(B^{\vee}C) = (A^{\circ}B)^{\vee}(A^{\circ}C)$

There are additional laws that are valid in Boolean algebra but do not exist in normal algebra:

The complementation rules are.

$$A \wedge \bar{A} = 0$$

$A \vee \bar{A} = 1$

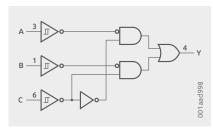

A very important rule is the so called de Morgan law. It can be used to optimize and restructure logic designs. If inverted inputs are processed with an AND operation this is identical to process these variables via an OR operation and to invert the result. The same law can be applied if you process inverted input variables with an OR operation. It is identical to have an AND operation for the variables and to invert the result.

De Morgan laws:

$$\overline{A} \wedge \overline{B} = \overline{(A \vee B)}$$

$\overline{A} \vee \overline{B} = \overline{(A \wedge B)}$

Where:

# 2.1 Basic logic gate functions

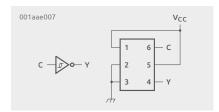

#### Inverter/ NOT Gate

The most simple gate function is the inverter. Below is the simple logic table of an inverter.

Table 3: Inverter or NOT Gate

| Input A | Output Y |

|---------|----------|

| 0       | 1        |

| 1       | 0        |

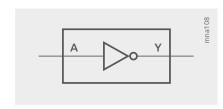

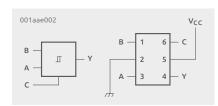

There are two styles of symbols commonly used for Gates. One is the ANSI/IEEE Std 91/91a-1991 type, the other one is according IEC 60617-12. In English and US publications the IEC symbols can be found seldomly only. So they do not reach the high international relevance of the IEEE style.

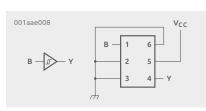

Figure 2.1a | IEEE symbol of an Inverter

Figure 2.1b | IEC symbol of an Inverter

<sup>^=</sup>logic AND, v=logic OR

# 2.2 Logic gates

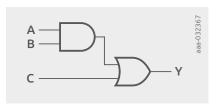

In the logic portfolio basic functions are provided to enable the direct application of Boolean algebra. For example, the logic component for the AND operation is called an AND gate. Within electrical systems these gates are often referred to as control logic

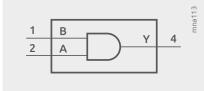

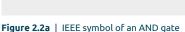

#### **AND Gate**

The 2-input AND function is depicted in Table 4. The output of an AND gate will only be high (1) if all inputs are high. All other input combinations will result in a low (0) at the output. In electronic systems with active high enable, an AND gate output can be used to prevent enabling the system until certain conditions (e.g. power and temperature status) monitored at the AND gate inputs are met. If either input is held high the output will have the same state as the other input. This enables either input to be used as an active high enable to gate data streamed on the other input.

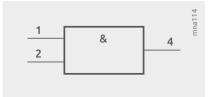

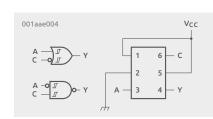

In Figure 2.2 the symbols for a 2-input AND gate are depicted.

Table 4: 2-Input AND gate function table

| Input A | Input B | Output Y |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 0        |

| 1       | 0       | 0        |

| 1       | 1       | 1        |

Figure 2.2b | IEC symbol of an AND gate

#### **NAND Gate**

If the output of an AND gate is inverted another basic function, a NAND gate is realized. The 2-input NAND function is depicted in Table 5. The output of a NAND gate will only be low if all inputs are high. All other input combinations will result in a high at the output. In electronic systems with active high enable, a NAND gate output can be used to disable the system if a combination of undesired conditions monitored at the NAND gate inputs have been met. If either input is held high the output will have the inverted state of the other input. This provides an active high gated inverter function.

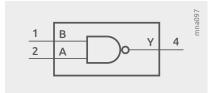

In Figure 2.3 the symbols for a 2-input NAND gate are depicted.

Table 5: 2-Input NAND gate function table

| Input A | Input B | Output Y |

|---------|---------|----------|

| 0       | 0       | 1        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 0        |

Figure 2.3a | IEEE symbol of a NAND gate

Figure 2.3b | IEC symbol of a NAND gate

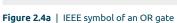

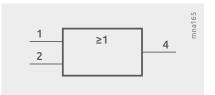

#### **OR Gate**

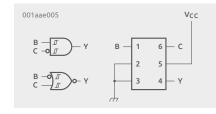

The 2-input OR function is depicted in Table 6. The output of an OR gate will only be low if all inputs are low. All other input combinations will result in a high at the output. In electronic systems with active high enable, an OR gate output can be used to enable the system if one or more conditions (e.g. automatic or manual start) monitored at the OR gate inputs is true. If either input is held low the output will have the same state as the other input. This enables either input to be used as an active low enable to gate data streamed on the other input.

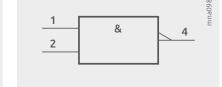

In Figure 2.4 the symbols for a 2-input OR gate are depicted.

Table 6: 2-Input OR gate function table

| Input A | Input B | Output Y |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 1        |

Figure 2.4b | IEC symbol of an OR gate

#### **NOR Gate**

If the output of an OR gate is inverted another basic function, a NOR gate is realized. The 2-input NOR function is depicted in Table 7. The output of a NOR gate will only be high if all inputs are low. All other input combinations will result in a low at the output. In electronic systems with active high enable, a NOR gate output can be used to disable the system if any undesired conditions monitored at the NOR gate inputs have been met. If either input is held low the output will have the inverted state of the other input. This provides an active low gated inverter function.

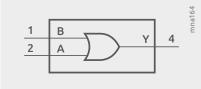

In Figure 2.5 the symbols for a 2-input NOR gate are depicted.

Table 7: 2-Input NOR gate function table

| Input A | Input B | Output Y |

|---------|---------|----------|

| 0       | 0       | 1        |

| 0       | 1       | 0        |

| 1       | 0       | 0        |

| 1       | 1       | 0        |

Figure 2.5b | IEC symbol of a NOR gate

#### Exclusive-OR (XOR) Gate

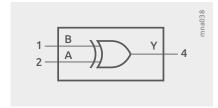

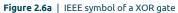

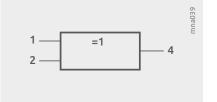

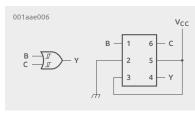

The 2-input Exclusive-OR (XOR) function is depicted in Table 8. The output of a XOR gate will only be high if only one of the inputs is high. All other input combinations will result in a low at the output. In electronic systems with active high enable, an XOR gate output can be used to enable the system if only one condition monitored at the XOR gate inputs has been met. If either input is held low the output will have the same state as the other input. If either input is held high the output will have the inverted state of the other input. This provides a dynamically controlled device that can stream data or inverted data.

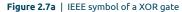

In Figure 2.6 the symbols for a 2-input XOR gate are depicted.

Table 8: 2-Input Exclusive-OR-Gate

| Input A | Input B | Output Y |

|---------|---------|----------|

| 0       | 0       | 0        |

| 0       | 1       | 1        |

| 1       | 0       | 1        |

| 1       | 1       | 0        |

Figure 2.6b | IEC symbol of a XOR gate

#### Exclusive-NOR (XNOR) Gate

If an inverter is added behind an exclusive OR the function of an XNOR is realized. The 2-input Exclusive-NOR (XNOR) function is depicted in Table 9. The output of a XNOR gate will only be high if both inputs are the same. All other input combinations will result in a low at the output. In electronic systems with active high enable, an XOR gate output can be used to enable the system if both conditions monitored at the XOR gate inputs are the same. If either input is held high the output will have the same state as the other input. If either input is held low the output will have the inverted state of the other input. This provides a dynamically controlled device that can stream data or inverted data.

In Figure 2.7 the symbols for a 2-input XNOR gate are depicted.

Table 9: 2-Input Exclusive NOR-Gate

| Input A | Input B | Output Y |

|---------|---------|----------|

| 0       | 0       | 1        |

| 0       | 1       | 0        |

| 1       | 0       | 0        |

| 1       | 1       | 1        |

Figure 2.7b | IEC symbol of a XOR gate

Logic basics, Generic Logic product properties

## 2.3 Storage elements

#### **Flipflops**

A flipflop is a circuit which has two stable conditions at the output. This logic condition of a low or high state at the output does not depend on the actual setting of control inputs only but also on the history. A flipflop can store a state for an infinite time as long as a supply voltage is present. So it can store the information of one bit.

There are several types of flipflops with different topologies.

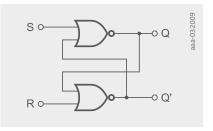

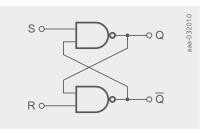

Most simple is a so-called RS-flipflop. It can be set and reset via two inputs that work level controlled.

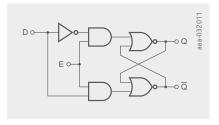

A more important category of flipflops are D-flipflops. They have a data input D and can store the state of this signal line. Storage can be controlled by an enable signal. These flipflops are transparent from input to output as long as the enable signal is set to high level. The last logical state is stored once the enable is turned off.

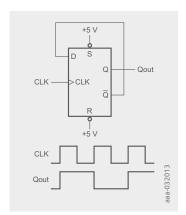

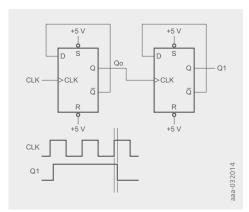

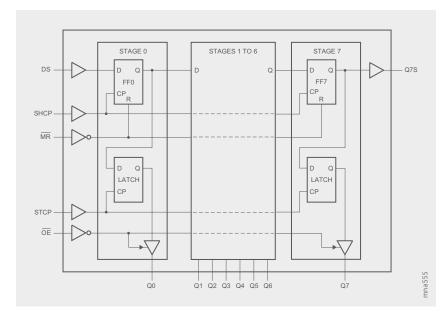

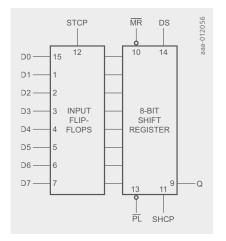

The most important category of flipflops work with a so-called clock signal CLK. The input signal is sampled and stored by the rising or falling edge of the clock. The clock-driven flipflops are the basic block for many important circuits in logic designs. These are multi-bit storage devices called registers as well as counters and shift registers.

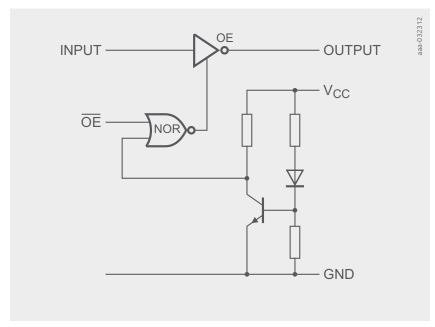

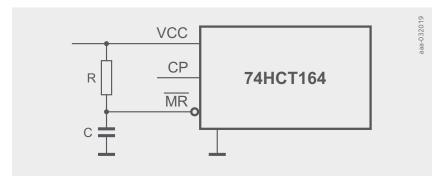

Logic devices from the standard families with storage stages have no internal power-on circuitry applying a reset to the flipflops in the IC. If a defined start condition for such devices is required, the application has to take care that after the supply voltage is ramped up into the recommended  $V_{CC}$  range, suitable controls are provided to the IC to bring it into the desired state.

If the product has a reset pin, this control can be used to clear flipflops contained in the design. This makes it easy to create a cleared state power-on condition. The timing requirements for the reset have to be obeyed. It does not work to connect a low active reset pin to the supply directly. Then  $V_{CC}$  and reset pin ramp up together and the device has no chance to perform a safe reset. In the FAQ section more advice can be found how to secure a reliable power up behavior if this is required by the target application.

A detailed explanation of flipflop types and more complex circuits designed with this basic function can be found in Chapter 6 of this handbook.

### 2.4 Switches

#### **Analog Switches**

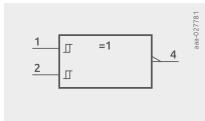

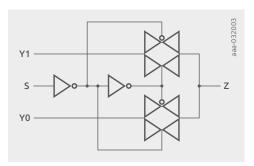

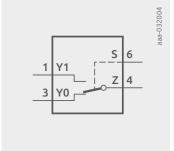

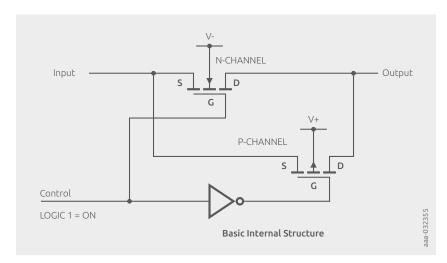

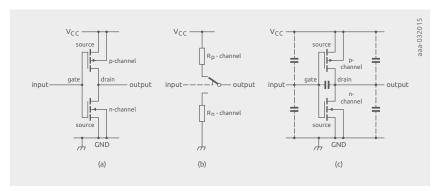

Analog switches are bi-directional transmission gates, consisting of a PMOS and a NMOS transistor in parallel. They are used for switching rail to rail analog and low frequency digital signals. There are many configurations of analog switch available. Single pole single throw (SPST) is used in isolation applications. A single digital control pin is used to turn the switch on or off connecting or isolating the signal path. In the SP8T configuration three digital control pins are used to connect one input/output to one of eight output/inputs. Due to the bi-directional feature of analog switches the SP8T configuration is also known as an 8:1 analog multiplexer/demultiplexer. In Figure 2.8 an SPDT configuration is shown. Two transmission gates have one common terminal, the pole and two independent throw terminals. This configuration uses a single digital control signal S to switch the pole terminal Z to either of the throw terminals Y1 or Y2.

Figure 2.8 | SPDT analog switch

Figure 2.9 | Logic diagram SPDT switch

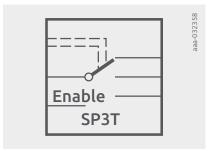

Many products include a control pin to allow the multiplexer to be enabled or disabled. When disabled all switches are non-conducting (off). This enables the poles of several devices to be connected to create larger multiplexer/demultiplexing solutions. Devices with this feature are identified with SPxT-Z, the -Z indicating they can be disabled.

Multiplexer configurations are used extensively in analog input expansion applications. Many microprocessors have a limited number of analog to digital converter (ADC) inputs. An analog multiplexer can be used to sequentially monitor many analog sensors using the same ADC input. On resistance (RON) and switching time (ten) specifications are provided in datasheets to enable an assessment to be made for application suitability.

Analog switches can also be used with digital signal isolation and multiplexing/demultiplexing. As they are transmission gates they will not behave as a repeater and regenerate the digital signals, care must be taken to ensure that the digital signal is not compromised by any bandwidth limitations of the analog switch. Analog switch datasheets include a –3 dB bandwidth specification to allow assessment on the effect on the digital signal to ensure signal integrity within the application.

#### **Bus switches**

If several SPxT-Z analog switches are used in parallel, data from several sources can be multiplexed onto a single data line. From a system standpoint connecting poles together does increase the effective load capacitance seen by the data signal. This will reduce the bandwidth of the solution. Bus switches have the same key parameters and are available in the same configurations as the above discussed analog switches. They can be used in isolation and multiplexing applications. To support the data rate increases in modern applications, bus switches have lower switch capacitance  $C_{S(ON)}$ , resulting in higher bandwidth. Additional features of bus switches include options of voltage level translation and switching signals higher than the bus switch supply voltage.

## 2.5 Logic data sheet parameters

Each logic device is supported by a datasheet as a result the data sheet parameters published will be explained in detail. The logic data sheets start with a general description of a device followed by a section about major features and benefits. Automotive qualified components can be identified easily via the Q100 at the end of the product name.

All logic parts exceed at least a 2 kV HBM (Human Body Model) and 1 kV CDM (Charged Device Model) ESD rating to ensure safe handling in assembly and production.

A section with ordering information follows addressing different package variants of the product. Marking code information is provided next, followed by functional diagrams as discussed above. Pinning information per package option can be found and a pin description.

A function table describes in detail how the device works exactly in dependence on all control inputs and/or a clock signal.

# 2.6 Limiting values

Liming values are provided in accordance with the Absolute Maximum Rating System (IEC 60134). The device is not guaranteed to function under these conditions, it is guaranteed not to be degraded if stresses are kept within the limiting values.

The limiting values start with the allowed supply voltage range from  $V_{CC}(min)$  up to  $V_{CC}(max)$ . If this range is obeyed, no damage can happen to the device, but it does not need to be functional.  $V_{CC}(min)$  is equal  $-0.5\,V$  in most cases. This is not a supply for operation of course. A range for the input and output voltages  $V_I$  and  $V_O$  is informed as next parameter. These values can be exceeded as long as the related clamping current limit  $I_{IK}$  and  $I_{OK}$  are obeyed.

A limiting value for the current of a single output is provided as well as an  $I_{CC}$  and  $I_{GND}$  limit which is reached for example if several outputs drive a comparably low-ohmic resistor load. If the output termination is applied towards ground, an  $I_{CC}$  current will be seen if the output state is high. If output termination is realized towards  $V_{CC}$ , additional ground current is created if the state of the output is the low-state.

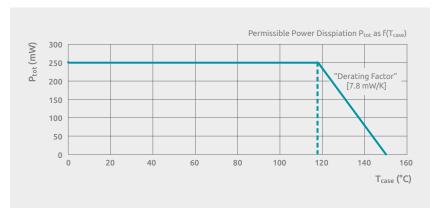

Logic components can be stored at temperatures from  $-65\,^{\circ}\text{C}$  up to  $150\,^{\circ}\text{C}$ . The power dissipation of a device is limited to the value  $P_{tot}$  for a defined temperature range. For some package options a linear derating is mentioned as a footnote with a power decrease factor of e.g.  $7.8\,\text{mW/K}$  to be applied starting for temperatures above  $118\,^{\circ}\text{C}$ .  $P_{tot}$  reaches  $0\,\text{mW}$  at  $T_{amb} = 150\,^{\circ}\text{C}$ . An electronic component with bond wires of gold shall not exceed a die temperature or  $T_i$  above  $150\,^{\circ}\text{C}$ .

## 2.7 Recommended operating conditions

In this section of a logic device data sheet, the ranges for  $V_{CC}$ ,  $V_I$  and  $V_O$  is informed. For  $V_O$  ranges can be found for products that support the  $I_{OFF}$  feature. These components have high-ohmic output stages if the supply voltage is removed ( $V_{CC}=0$  V). In power down or suspend mode, the maximum value for the recommended supply voltage range can be applied.

An important parameter in the recommended operating condition section is the maximum allowed input transition and fall rate  $\Delta t/\Delta V$ . If this condition is not fulfilled, current consumption can increase and malfunction could occur for clocked devices or in case of noise overlay to the signals.

Logic basics, Generic Logic product properties

### 2.8 Static characteristics

The static characteristics chapter inform the minimum voltage for a high-level input signal  $V_{IH}$ (min) and the maximum voltage for a low-level input signal  $V_{II}$  (max) for a specific supply voltage  $V_{CC}$ . These parameters tell which area of the input voltage range is undefined or forbidden.

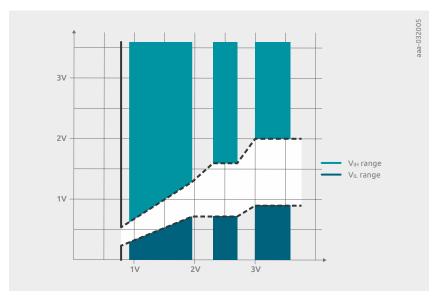

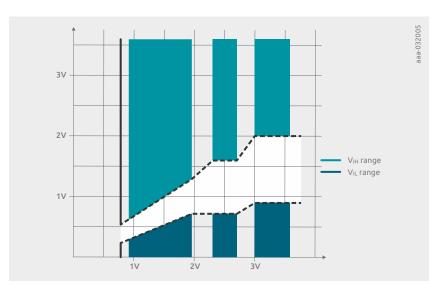

Figure 2.10 shows the resulting input voltage ranges dependent on  $V_{CC}$  for the logic family AUP. The signal has to stay in one of the blue areas to be processed as a low-level or high-level.

Figure 2.10 | Input voltage ranges of the logic family AUP dependent on V<sub>CC</sub>

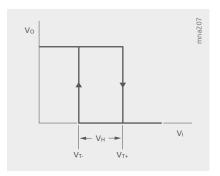

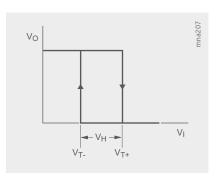

For Schmitt trigger inputs the positive going threshold voltage  $V_{T+}$  and the negative-going threshold voltage V<sub>T-</sub> is shown as transfer characteristic to define the behavior of a digital input. A Schmitt Trigger input provides a hysteresis characteristic as depicted in Figure 2.11. Schmitt Trigger inputs are tolerant to smooth transitions and quite immune against noise on the input signals. Many logic components feature a so-called Schmitt Trigger Action input. Such input does not have a wide hysteresis like a full performance Schmitt-Trigger input but performs more safely in case of noise overlay on transitions compared to a conventional input characteristic.

The static characteristics in a data sheet furthermore include the output voltages for a logic high-level V<sub>OH</sub> and low-level V<sub>OL</sub> for defined output currents and supply voltages. For a proper operation from a logic device output to a logic device input the relation between output and input voltage has to be in line with row 1 and 4 of Table 10.

Figure 2.11 | Schmitt Trigger Input Characteristic

#### Table 10: Voltage requirements from output to input for a proper operation

| Device 1              |   | Device 2              | Operation               |

|-----------------------|---|-----------------------|-------------------------|

| V <sub>OH</sub> (min) | > | V <sub>IH</sub> (min) | Function guaranteed     |

| V <sub>OH</sub> (min) | < | V <sub>IH</sub> (min) | Function not guaranteed |

| V <sub>OL</sub> (max) | > | V <sub>IL</sub> (max) | Function not guaranteed |

| V <sub>OL</sub> (max) | < | V <sub>IL</sub> (max) | Function guaranteed     |

Additional static parameters are the supply current maximum for open outputs  $I_{CC}(max)$  and the maximum input leakage current  $I_{I}(max)$ . For devices that support the  $I_{OFF}$  feature, the maximum power-off current  $I_{OFF}$  (max) is informed for  $V_{CC} = 0$  V and a maximum  $\Delta I_{OFF}$  for  $V_{CC}$  from 0 V to 0.2 V, means that a  $V_{CC}$  turn-off is not ideal.

As an additional supply current parameter for input voltage deviating from perfect 0V or  $V_{CC}$  low or high level condition, a maximum  $\Delta I_{CC}$  current value can be found.

The above described static characteristics are provided for different temperature ranges for many logic devices in separate tables.

Logic basics, Generic Logic product properties

# 2.9 Dynamic characteristics

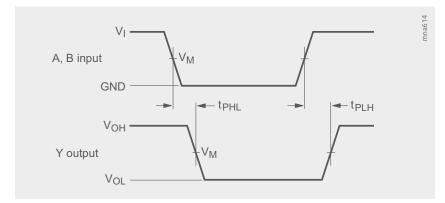

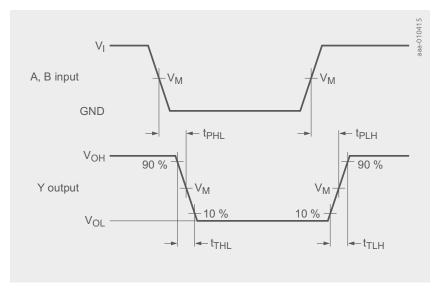

The propagation delay  $t_{PD}$  is a very important dynamic parameter of a logic device. For a gate or buffer it is the simple delay for a change at an input to a change of a logic state at the output. In Figure 2.12 an example is shown for a 2-input AND-Gate. The diagram depicts a propagation delay for the negative-going edge  $t_{PHL}$  and the opposite direction from low to high state  $t_{PLH}$ . Propagation delay is measured from a 50% level of the related transitions.

Figure 2.12 | Data input to output propagation delay

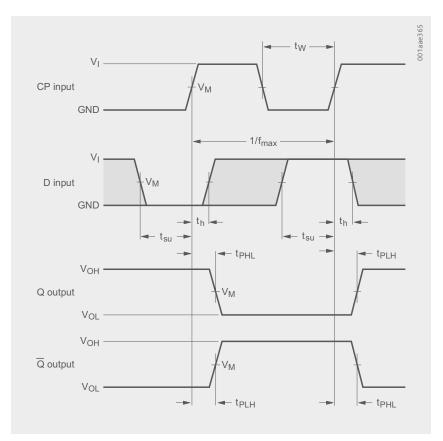

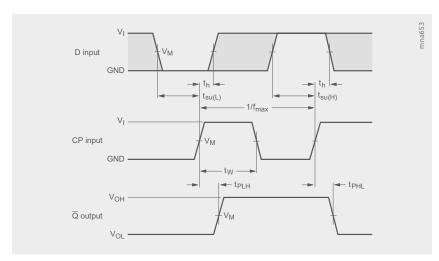

For edge-triggered devices propagation delay is defined as time between the active clock transition and the change of state at the output. Figure 2.13 is a timing diagram of a Flipflop. Propagation delay is measured from the rising edge to the change of the output signal. Beside propagation delay other important timing parameters are shown in the diagram. The data input D needs to be stable for at least the set-up time  $t_{su}$  before the active clock transition and needs to stay stable at least for the hold time  $t_{h}$ .  $t_{max}$  is the maximum clock frequency of a logic device. This value is a good indication for the maximum signal speed that gates can handle from a considered logic family. The parameter  $t_{w}$  defines the minimum pulse width for the clock input CP low state and the width of the set and reset signals. All these parameters can be found in the dynamic characteristics chapter of a data sheet.

Figure 2.13 | Timing diagram of a Flipflop

The dynamic parameters are listed for different supply voltages ( $V_{CC}$ ). The higher the voltage, the faster a CMOS logic device becomes. Lower temperature decreases  $t_{\rm pd}$ .

$\mathsf{C}_{\mathsf{PD}}$  is an equivalent power dissipation capacitance that supports the calculation of the dynamic power dissipation:

$$P_D = C_{PD} \times V_{CC}^2 \times f_i \times N + \sum [C_L \times V_{CC}^2 \times f_o]$$

f<sub>I</sub>=input frequency in MHz f<sub>O</sub>=output frequency in MHz C<sub>I</sub> = output load capacitance in pF  $V_{CC}$ =Supply voltage in V N= number of inputs  $Sum [C_L \times V_{CC}^2 \times f_O]$  = sum of all outputs

More details about timing aspects are discussed in the chapter Timing Considerations.

#### Other info

The logic data sheets inform with detailed waveform diagrams and test circuit schematics how data sheet values and parameters are derived and need to be tested. In a final section of data sheets the package outline of all the variants of a product are shown together with tolerance information.

# Chapter 3

# Power considerations for CMOS and BiCMOS logic devices

Power considerations for CMOS and BiCMOS logic devices

As general purpose components, logic devices are used at different frequencies and power supply voltages in many different varieties of applications. This large diversity has produced the need to express a single parameter that can be used in determining the power dissipation of a device in a given application. This chapter describes different components of power dissipation and how they may be calculated.

### 3.1 Static considerations

#### **CMOS**

When a CMOS device is not switching and the input levels are GND or  $V_{CC}$ , the p-channel and n-channel transistors do not conduct at the same time; no direct MOS transistor channel path exists between  $V_{CC}$  & GND. In practice however, thermally generated minority carriers, which are present in all reverse biased diode junctions, allow a very small leakage current to flow between  $V_{CC}$  and GND. As this leakage current is typically a few nA, quiescent CMOS power dissipation is extremely low. Maximum quiescent power dissipation for the above conditions is calculated as:

$$P_D = V_{CC} \times I_{CC} \tag{1}$$

Where:

I<sub>CC</sub> = specified in the device datasheet

#### **BICMOS**

In the case of BiCMOS (Bipolar CMOS) devices; the current in the output bipolar stage is different when the output is set high or low. This results in two datasheet specifications for quiescent current  $I_{CC(for\ output\ low)}$  &  $I_{CC(for\ output\ high)}$ . Quiescent power dissipation for input levels of GND or  $V_{CC}$  is calculated as:

$$P_D = V_{CC} \times (n_1 I_{CC(for\ output\ low)} + n_2 I_{CC(for\ output\ high)})/(n_1 + n_2)$$

(2)

Where:

$n_1$  = number of outputs LOW

n₂ = number of outputs HIGH

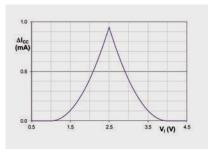

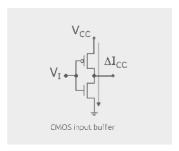

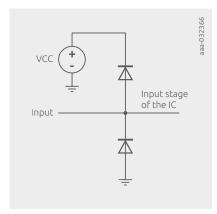

#### Input stage current due to GND < VI < VCC

In the case where the input levels of the device are not held at GND or  $V_{CC}$ , a direct MOS transistor current path can exist between  $V_{CC}$  and GND; this leads to additional supply current through the input buffer stage of CMOS devices, and additional power dissipation. In device datasheets this is represented as  $\Delta I_{CC}$ , the additional current due to an input level other than  $V_{CC}$  or GND. In the case of 5.5 V logic families this parameter is generally measured at an input voltage of  $V_{CC}$  –2.1; in the case of 3.3 V logic families it's measured at an input voltage of  $V_{CC}$  –0.6 V. Static power dissipation is then calculated as:

$$P_D = V_{CC} \times \left[ (n_1 I_{CC(for\ output\ low)} + n_2 I_{CC(for\ output\ high)}) / (n_1 + n_2) + n\Delta I_{CC} \right]$$

(3)

Where:

n = number of inputs at the intermediate level

Note:

For CMOS  $I_{CCL} = I_{CCH} = I_{CC}$ , simplifying Equation (3):  $P_D = V_{CC} \times [I_{CC} + n\Delta I_{CC}]$

Table 1 shows a comparison of  $I_{CC}$  and  $\Delta I_{CC}$  for the '244 (octal buffer) function of several logic families.

Table 1: Power consumption of logic process families

|           |         | CMOS families     |                         |                  |       |

|-----------|---------|-------------------|-------------------------|------------------|-------|

| Device    | Voltage | I <sub>cc</sub> Q | VI                      | ΔI <sub>CC</sub> | Units |

| 74HC244   | 6V      | 80                | V <sub>CC</sub> – 2.1 V | 450              | μΑ    |

| 74AHC244  | 5.5 V   | 40                | V <sub>CC</sub> -2.1 V  | 1500             | μΑ    |

| 74LV244   | 5.5 V   | 20                | V <sub>CC</sub> -0.6 V  | 500              | μA    |

| 74LVC244  | 3.6V    | 10                | V <sub>CC</sub> -0.6V   | 500              | μA    |

| 74ALVC244 | 3.6 V   | 10                | V <sub>CC</sub> -0.6 V  | 750              | μΑ    |

|           |         |                   |                         |                  |       |

| BICMOS families |         |                  |                  |                  |                        |                  |       |  |

|-----------------|---------|------------------|------------------|------------------|------------------------|------------------|-------|--|

| Device          | Voltage | I <sub>CCZ</sub> | I <sub>CCL</sub> | I <sub>CCH</sub> | VI                     | ΔI <sub>CC</sub> | Units |  |

| 74LVT244        | 3.6V    | 0,19             | 12               | 0,19             | V <sub>CC</sub> -0.6 V | 0,2              | mA    |  |

## 3.2 Dynamic considerations

When a device is clocked or changing state, power is dissipated through the charging and discharging of on-chip parasitic and load capacitances. Power is also dissipated at the moment the output switches when both the p-channel and the n-channel transistors are partially conducting. This transient energy loss is typically only 10% of that due to parasitic capacitance.

The total dynamic power dissipation per device is:

$$P_D = \Sigma (C_{PD}V_{CC}^2 f_I) + \Sigma (C_L V_{CC}^2 f_O)$$

(4)

Where:

C<sub>PD</sub> = power dissipation capacitance per buffer

$f_1$ =input frequency

$f_O$  = output frequency  $C_L$  = total external load capacitance per output

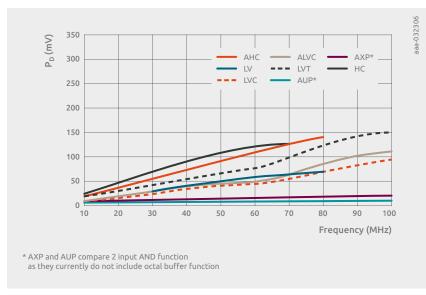

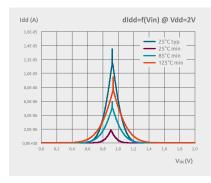

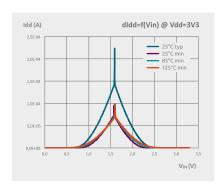

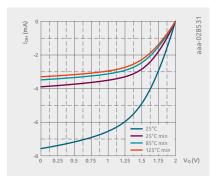

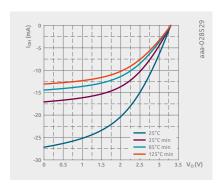

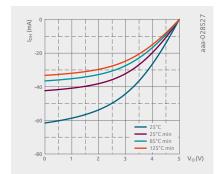

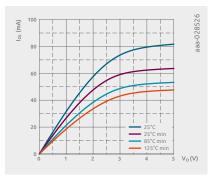

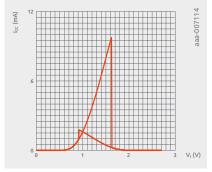

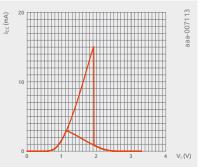

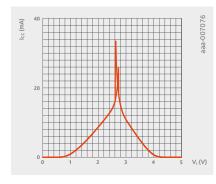

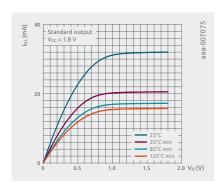

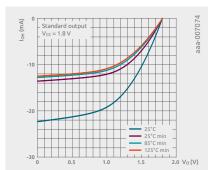

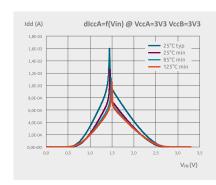

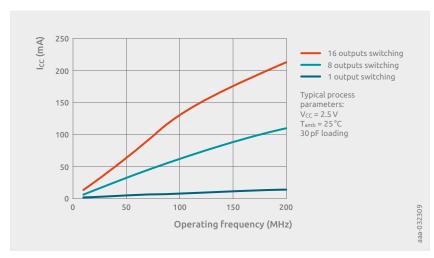

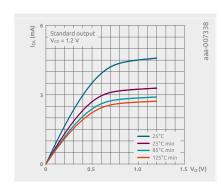

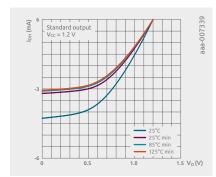

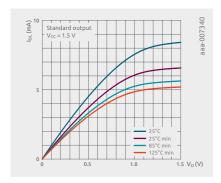

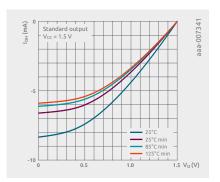

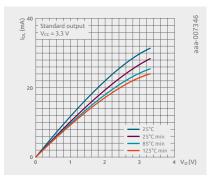

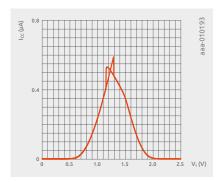

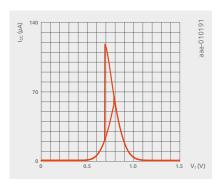

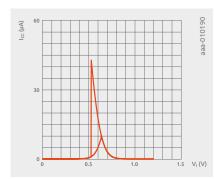

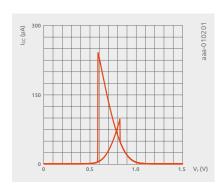

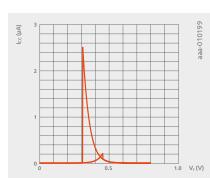

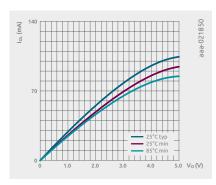

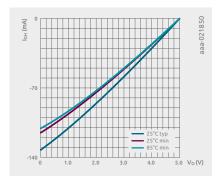

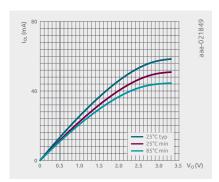

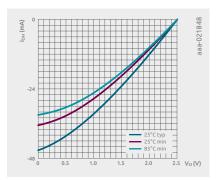

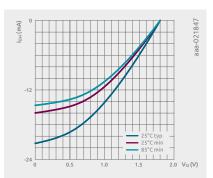

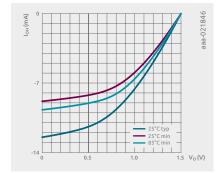

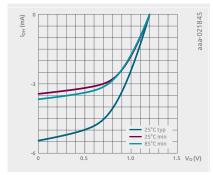

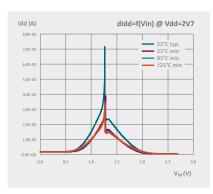

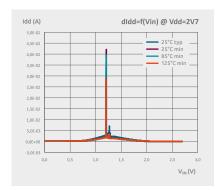

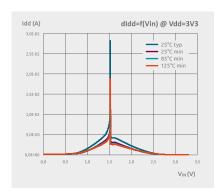

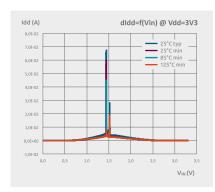

It should be noted from the Equation (4), that  $C_{PD}$  is a useful parameter for determining power dissipation in any device for which power dissipation is a linear function of frequency. Figure 3.1 shows  $I_{CC}$  as a function of frequency for the devices listed in Table 1. From this we can conclude that for all CMOS and BiCMOS logic families  $C_{PD}$  can be used in order to determine the worst case power consumption of a device in a given application.

Figure 3.1 | Power consumption over frequency for various logic process families

#### 3.2.1 Duty cycle considerations with unbalanced outputs

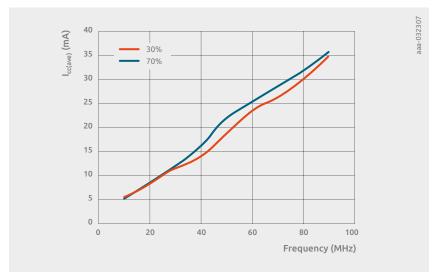

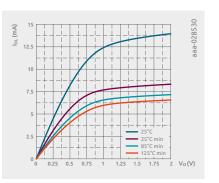

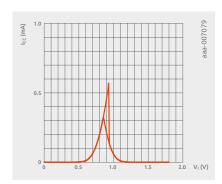

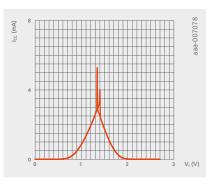

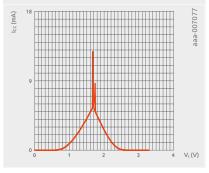

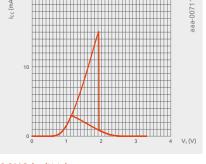

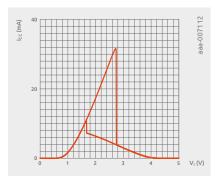

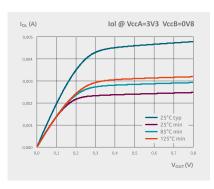

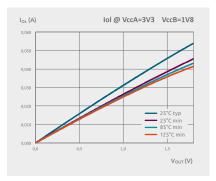

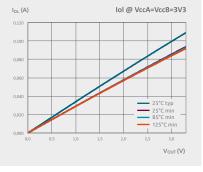

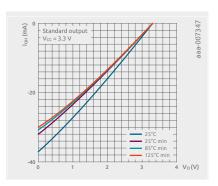

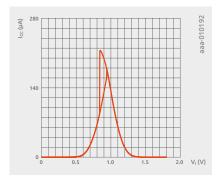

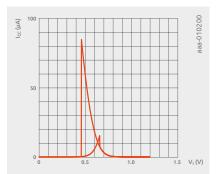

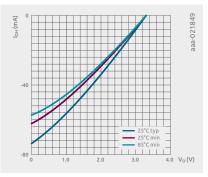

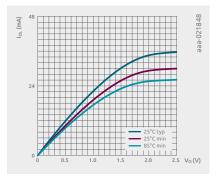

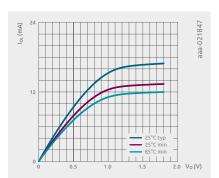

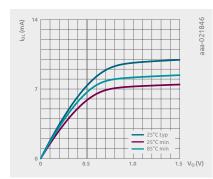

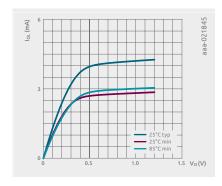

In the case of unbalanced output drive, such as found in BiCMOS, the output duty cycle could also be considered. Figure 3.2 shows the effect of duty cycle on the power dissipation of the 74LVT244. It can be concluded from these measurements that the duty cycle has little effect on the total power dissipation. This is due to the switching currents within BiCMOS products being more dominant than steady state currents.

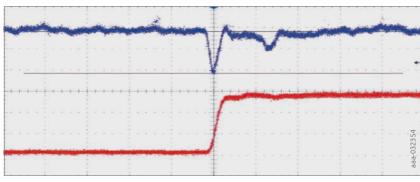

Figure 3.2 | Current consumption for different duty cycles

#### 3.2.2 Power dissipation due to slow input rise/fall times

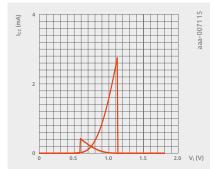

When an CMOS push pull stage switches, there is a brief period when both output transistors conduct. The resulting through-current is additional to the normal supply current and causes power dissipation to increase linearly with the input rise or fall time. As long as the input voltage is less than the n-channel transistor threshold voltage, or is higher than  $V_{CC}$  minus the p-channel transistor threshold voltage, one of the input transistors is always off and there is no through-current. When the input voltage equals the n-channel transistor threshold voltage (typ. 0.7 V), the n-channel transistor starts to conduct and through-current flows, reaching a maximum at  $V_1$ =0.5  $V_{CC}$ . For devices with CMOS inputs, the maximum current is determined by the geometry of the input transistors. When Schmitt triggers are used to square pulses with long rise/fall times, through-current at the Schmitt-trigger inputs will increase the power dissipation (see Schmitt-trigger data sheets).

#### 3.2.3 Process family related dynamic power dissipation

2.3 V to 2.5 V

Dynamic power dissipation can be reduced using more advanced process technology. The table below shows a comparison of propagation delay and dynamic power dissipation for various process family devices based on the 2 input AND function. In the comparison, AUP and AXP have the lowest power consumption, generally the trend towards low power consumption of newer process families can be clearly seen.

|        |     | 4.5                  | v to 5.5 | V                   | 3.0 V to 3.6 V |                      |      |                     |

|--------|-----|----------------------|----------|---------------------|----------------|----------------------|------|---------------------|

|        |     | typ                  | max      |                     | min            | typ                  | max  |                     |

|        |     | t <sub>PD</sub> (ns) |          | P <sub>D</sub> (mW) |                | t <sub>PD</sub> (ns) |      | P <sub>D</sub> (mW) |

| HC(T)  | -   | 9.0                  | 23.0     | 750                 | -              | -                    | -    | -                   |

| AHC(T) | 1.0 | 4.6                  | 9.0      | 550                 | 1.0            | 6.5                  | 14.0 | 240                 |

| LVC    | 0.5 | 1.7                  | 4.0      | 525                 | 0.5            | 2.1                  | 4.5  | 229                 |

| AUP    | -   | -                    | -        | -                   | 0.9            | 2.2                  | 4.3  | 98                  |

| AXP    | -   | -                    | -        | -                   | -              | -                    | -    | -                   |

|        |     |                      | 2.5 | •                   | 1105 1 105 1 |                      |     |                     |

|--------|-----|----------------------|-----|---------------------|--------------|----------------------|-----|---------------------|

|        |     | typ                  | max |                     | min          | typ                  | max |                     |

|        |     | t <sub>PD</sub> (ns) |     | P <sub>D</sub> (mW) |              | t <sub>PD</sub> (ns) |     | P <sub>D</sub> (mW) |

| HC(T)  | -   | -                    | -   | -                   | -            | -                    | -   | -                   |

| AHC(T) | -   | -                    | -   | -                   | -            | -                    | -   | -                   |

| LVC    | 0.5 | 2.2                  | 5.5 | 111                 | 1.0          | 3.4                  | 8.0 | 68                  |

| AUP    | 1.0 | 2.4                  | 4.8 | 45                  | 1.3          | 3.0                  | 6.1 | 26                  |

| AXP    | 0.9 | 2.0                  | 3.0 | 41                  | 1.2          | 2.6                  | 4.1 | 24                  |

1.65 V to 1.95 V

|        |     | 1.4 V               | to 1.6 | V    |     | 1.1 V               | to 1.3 | V    | (   | ).75 V            | to 0.8 | 5 V  |

|--------|-----|---------------------|--------|------|-----|---------------------|--------|------|-----|-------------------|--------|------|

|        |     | typ                 | max    | Pn   | min | typ                 | max    | PD   |     | typ               |        | PD   |

|        | t   | : <sub>PD</sub> (ns | )      | (mW) | t   | : <sub>PD</sub> (ns | s)     | (mW) | t   | <sub>PD</sub> (ns | s)     | (mW) |

| HC(T)  | -   | -                   | -      | -    | -   | -                   | -      | -    | -   | -                 | -      | -    |

| AHC(T) | -   | -                   | -      | -    | -   | -                   | -      | -    | -   | -                 | -      | -    |

| LVC    | -   | -                   | -      | -    | -   | -                   | -      | -    | -   | -                 | -      | -    |

| AUP    | 1.5 | 3.7                 | 7.5    | 17.6 | 2.1 | 5.1                 | 11.7   | 11.1 | -   | 17                | -      | 4.8  |

| AXP    | 1.5 | 3.2                 | 5.0    | 16.7 | 1.8 | 4.3                 | 7.3    | 10.7 | 1.8 | 11                | 122    | 4.7  |

|        |     |                     |        |      |     |                     |        |      |     |                   |        |      |

Power considerations for CMOS and BiCMOS logic devices

## 3.3 Power dissipation capacitance

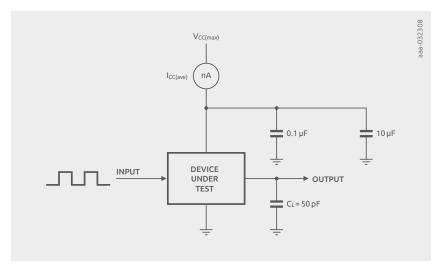

C<sub>PD</sub> is specified in the CMOS device data sheets, the published values being calculated from the results of tests described in this section. The test set-up is shown in Figure 3.3. The worst-case operating conditions for C<sub>PD</sub> are always chosen and the maximum number of internal and output circuits are toggled simultaneously, within the constraints listed in the data sheet. Devices that can be separated into independent sections are measured per section, the others are measured per device.

The recommended test frequency for determining C<sub>PD</sub> is 10 MHz, 50% duty cycle. Loading the switched outputs gives a more realistic value of CPD, because it prevents transient through-current in the output stages.

The values of C<sub>PD</sub> provided in datasheets have been calculated using:

$$C_{PD} = \frac{\left(I_{cc(ave)} \times V_{CC}\right) - \left[\left(C_L \times V_{CC}^2 \times f_o\right) + V_{CC} \times I_{STAT}\right]}{V_{CC}^2 \times f_I}$$

(5)

Where:

C<sub>PD</sub> = power dissipation capacitance (per buffer)

$I_{CC(ave)} =$ supply current V<sub>CC</sub> = supply voltage  $C_L$  = output load capacitance  $f_O =$ output frequency f<sub>i</sub>=input frequency I<sub>STAT</sub> = supply current at dc (approx. zero for CMOS)

Figure 3.3 | Test set-up for C<sub>PD</sub> determination

#### 3.3.1 Example CPD calculations

#### **CMOS**

In the case of 74LVC244, I<sub>STAT</sub> is negligible and can be considered as zero for the purpose of C<sub>PD</sub> calculation. The test set-up for the '244 as indicated in *Conditions for*  $C_{PD}$  tests was used, with the load shown in Figure 3.3. At  $V_{CC} = 3.6 \text{ V}$ ,  $f_1 = 10 \text{ MHz}$ ;  $I_{CC(ave)}$  was found to be 2.24 mA.

Using Equation (5):

$$C_{PD} = \frac{(2.24 \, mA \times 3.6 \, V) - [(50 \, pF \times 3.6 \, V^2 \times 10 \, MHz) + 0 \, mW]}{3.6 \, V^2 \times 10 \, MHz}$$

$$C_{PD} = 12.2 \, pF$$

Power considerations for CMOS and BiCMOS logic devices

In the case of 74LVT244, I<sub>STAT</sub> cannot be considered as negligible at low frequency. As a result, a higher frequency is recommended for modeling its C<sub>PD</sub>. The test setup depicted in Figure 3.3 has been used, however at a frequency of 30 MHz. I<sub>CC(ave)</sub> was found to be  $11.53 \,\mathrm{mA}$ . We then apply Equation (5) with the assumption that  $I_{STAT}$  is negligible.

Using Equation (5):

$$C_{PD} = \frac{(11.53 \ mA \times 3.6 \ V) - (50 \ pF \times 3.6 \ V^2 \times 30 \ MHz)}{3.6 \ V^2 \times 30 \ MHz}$$

$$C_{PD} = 56.8 \, pF$$

#### Note:

Performing the measurement and calculation at 20 MHz results in a CPD of 66 pF. Due to the uncertainty of  $I_{STAT}$  in a given configuration, it is recommended that a 5 to 10% quardband is used when approximating power dissipation for BiCMOS devices.

# 3.4 Using CPD to calculate power dissipation

#### 3.4.1 CMOS Device Calculation

Consider a 3.6 V application in which every 40 ms a 74LVC244A device is used to buffer four 40 MHz, 75% positive duty cycle signals and two 80 MHz, 75% positive duty cycle signals, for a duration of 25 ms. The unused inputs are tied to 3.6 V, the outputs drive 30 pF loads, and when not buffering, four inputs are held at 3.0 V and two inputs held at GND.

In calculating the average power dissipation we need to consider both the power dissipation for the 15 ms when the device is not buffering, and the power dissipation for the 25 ms when the buffers are active.

In the first 15 ms the device is static and power dissipation is calculated using simplified Equation (3). In this case we have four inputs that are connected to  $V_{CC} = 0.6 \text{ V}.$

$$P_{D1} = 3.6 \text{ V} \times 10 \mu A + 4 \times 3.6 \text{ V} \times 500 \mu A$$

= 7.24 mW

In the second 25 ms the total power dissipation can be estimated as the combination of static the dynamic dissipation due to the four buffers and outputs switching at 40 MHz, and dynamic dissipation due to the two buffers and outputs switching at 80 MHz.

$$P_{D2} = 4 \times (C_{PD} + C_L) \times 3.6^2 \times 40 \text{ MHz} + 2 \times (C_{PD} + C_L) \times 3.6^2 \times 80 \text{ MHz}$$

= 87.1 mW + 87.1 mW

= 174.2 mW

The average power dissipation is then:

$$P_{D(ave)} = (15 \times 7.24 \text{ mW} + 25 \text{ x } 174.2 \text{ mW}) / 40$$

= 111.6 mW

#### 3.4.2 BiCMOS Device Calculation

Consider the LVT244 in the same application.

In the case of BiCMOS devices, the duty cycle must be taken into consideration because  $I_{CCL}$  and  $I_{CCH}$  are not identical. In the first 15 ms of the application the static power dissipation is calculated using Equation (2) to determine quiescent power dissipation and adding the power dissipation caused by the four inputs that are connected to  $V_{CC}$  –0.6 V.

$$P_{D1} = 3.6 \text{ V} \times (6 \times I_{CC(for output \ high)} + 2 \times I_{CC(for output \ low)}) / 8 + 4 \times 3.6 \text{ V} \times \Delta I_{CC}$$

$$= 11.3 \text{ mW} + 2.9 \text{ mW}$$

$$= 14.2 \text{ mW}$$

The power dissipation in the next 25 ms contains in addition to those of the 74LVC244A case the component  $I_{STAT}$ .  $P_{D1}$  can be used to approximate  $I_{STAT}$ .

$$P_{D2} = 4 \times (C_{PD} + C_L) \times 3.6^2 \times 40 \text{ MHz} + 2 \text{ x } (C_{PD} + C_L) \times 3.6^2 \times 80 \text{ MHz} + 3.6 \times I_{STAT}$$

= 180 mW + 180 mW + 14.2 mW

= 374.2 mW

It should be noted that in using equation 3 to determine our dynamic dissipation components we are assuming a rail to rail output swing. As BiCMOS outputs don't swing rail to rail this will produce a worse case approximation.

The calculated average power dissipation is then:

$$PD_{(ave)} = (15 \times 14.2 \text{mW} + 25 \times 374.2 \text{ mW}) / 40$$

= 239.2 mW

### 3.5 Results and conclusion

Table 2: Comparison of measured and calculated results

|           | St                           | atic 15 m         | s                    | Dyn                          | amic 25           | Total          |                 |               |

|-----------|------------------------------|-------------------|----------------------|------------------------------|-------------------|----------------|-----------------|---------------|

| Device    | I <sub>CC(ave)</sub><br>(mA) | P <sub>D1</sub> ( | Calculated <b>(M</b> | I <sub>CC(ave)</sub><br>(mA) | P <sub>D2</sub> ( | Calculated (Mm | <b>P</b> D(ave) | Calculated (M |

| 74LVC244A | 0,008                        | 0,028             | 7,24                 | 48,2                         | 173,5             | 174,2          | 108,4           | 111,6         |

| 74LVT244  | 2,5                          | 9                 | 14,2                 | 102,4                        | 368,6             | 374,2          | 233,8           | 239,2         |

Determination of power dissipation is an essential part of system design. By understanding the static and dynamic components of power dissipation, and how they can be modeled; a system designer is able to estimate the worst case power dissipation of an application.

Table 2 shows the comparison of the measured results to those calculated. The values of static and dynamic current that were calculated are within 10% of the measured values. Importantly the calculated values are higher than the measured values. This is due to the calculations being made with worse case datasheet limits. This is considered advantageous in system level power calculations, as it provides extra power budget margin in the application. It can be concluded, from the examples presented, that any device that has a linear relationship between supply current and frequency can be modeled as a single power dissipation capacitance CPD for the purpose of power dissipation calculations of that device used in any application.

#### Conditions for C<sub>PD</sub> tests

#### Gates

All inputs except one are held at either  $V_{CC}$  or GND, depending on which state causes the output to toggle. The remaining input is toggled at a known frequency.  $C_{PD}$  is specified per-gate.

#### Decoders

One input is toggled, causing the outputs to toggle at the same rate (normally one of the address-select pins is switched while the decoder is enabled). All other inputs are tied to V<sub>CC</sub> or GND, whichever enables operation. C<sub>PD</sub> is specified per-independent-decoder.

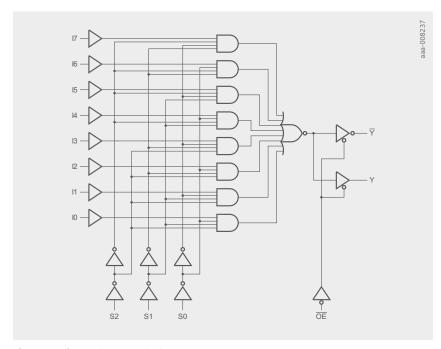

#### Multiplexers

One data input is tied HIGH and the other is tied LOW. The address-select and enable inputs are configured such that toggling one address input selects the two data inputs alternately, causing the outputs to toggle. With 3-State multiplexers, C<sub>PD</sub> is specified per output function for enabled outputs.

#### Bilateral switches

The switch inputs and outputs are open-circuit. With the enable input active, one of the select inputs is toggled, the others are tied HIGH or LOW. CPD is specified per switch.

#### 3-State buffers and transceivers

C<sub>PD</sub> is specified per buffer with the outputs enabled. Measurement is as for simple gates.

#### Latches

The device is clocked and data is toggled on alternate clock pulses. Other preset or clear inputs are held so that output toggling is enabled. If the device has common-locking latches, one latch is toggled by the clock. 3-State latches are measured with their outputs enabled. CPD is specified per-latch.

#### Flip-flops

Measurement is performed as for latches. The inputs to the device are toggled and any preset or clear inputs are held inactive.

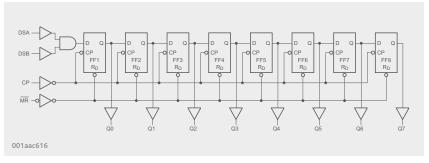

#### Shift registers

The register is clocked and the serial data input is toggled at alternate clock pulses (as described for latches). Clear and load inputs are held inactive and parallel data are held at V<sub>CC</sub> or GND.

3-State devices are measured with outputs enabled. If the device is for parallel loading only, it is loaded with 101010..., clocked to shift the data out and then reloaded.

#### Counters

A signal is applied to the clock input but other clear or load inputs are held inactive. Separate values for C<sub>PD</sub> are given for each counter in the device.

#### Arithmetic circuits

Adders, magnitude comparators, encoders, parity generators, ALUs and miscellaneous circuits are exercised to obtain the maximum number of simultaneously toggling outputs when toggling only one or two inputs.

#### Display drivers

C<sub>PD</sub> is not normally required for LED drivers because LEDs consume so much power as to make the effect of C<sub>PD</sub> negligible. Moreover, when blanked, the drivers are rarely driven at significant speeds. When it is needed, C<sub>PD</sub> is measured with outputs enabled and disabled while toggling between lamp test and blank (if provided), or between a display of numbers 6 and 7.

LCD drivers are tested by toggling the phase inputs that control the segment and backplane waveforms outputs. If either type of driver (LCD or LED) has latched inputs, then the latches are set to a flow-through mode.

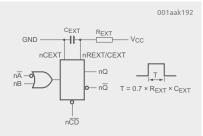

#### One-shot circuits

In some cases, when the device I<sub>CC</sub> is significant, C<sub>PD</sub> is not specified. When it is specified, C<sub>PD</sub> is measured by toggling one trigger input to make the output a square wave. The timing resistor is tied to a separate supply (equal to V<sub>CC</sub>) to eliminate its power contribution.

# Chapter 4

# Timing aspects of discrete devices

Timing aspects of discrete devices

In a circuit design, the right timing of all participating components is essential for functionality. A wrongly calculated delay of a component or a misunderstanding of its temporal behavior could end up in a complete system failure. This chapter will explain the required fundamentals to understand the timing aspects of logic devices and successfully apply them in the design process.

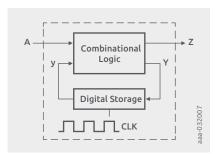

# 4.1 Synchronous and asynchronous logic

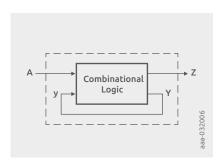

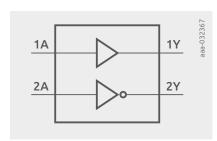

An asynchronous circuit, or self-timed circuit, is a digital logic circuit which is not governed by a clock circuit or global clock signal. Instead it often uses signals that indicate completion of instructions and operations, specified by simple data transfer protocols. This type of circuit is contrasted with synchronous circuits, in which changes to the signal values in the circuit are triggered by single or repetitive pulse called a clock signal. Most digital devices today use synchronous circuits. However asynchronous circuits have the potential to be faster, and may also have advantages in lower power consumption, lower electromagnetic interference, and better modularity in large systems. An illustration of asynchronous and synchronous logic circuit examples is given in Figure 4.1 and Figure 4.2.

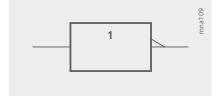

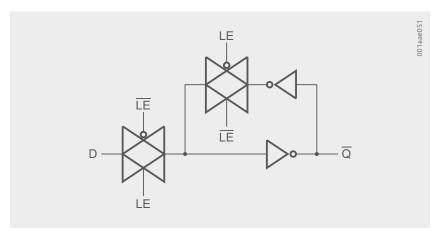

Figure 4.1 shows a symbol for asynchronous logic. In contrast to just combinatorial logic, a logic state can be stored and therefore a feedback loop is needed. An example for such an element is a simple RS Flip-Flop.

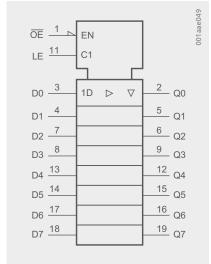

For a synchronous Logic element, the feedback loop id synchronized by an extra clock signal as shown in Figure 4.2.

Figure 4.1 | Asynchronous Logic element

Figure 4.2 | Synchronous Logic element

# 4.2 Propagation delay time of a device

In digital circuits, the propagation delay, or gate delay, is the length of time which starts when the input to a logic gate becomes stable and valid to change, to the time that the output of that logic gate is stable and valid to change. In logic components datasheets this refers to the time required for the output to reach 50% of its final output level when the input changes to 50% of its final input level. Reducing gate delays in digital circuits allows them to process data at a faster rate and improve overall performance. The determination of the propagation delay of a combined circuit requires identifying the longest path of propagation delays from input to output and by adding each  $t_{\rm PD}$  time along this path.

The difference in propagation delays of logic elements is the major contributor to glitches in asynchronous circuits as a result of race conditions.

Pulse Width  $t_W$  is the time gap between a rising edge and a falling edge of a signal. The reference signal level for measuring the time is 50% of the amplitude between high and low level. Figure 4.3 shows the measurement parameters for propagation delay ( $t_{pd}$  if  $t_{PHL} = t_{PLH}$ ), rise and fall times ( $t_{PL} = t_{PLH}$ ). Transition times are measured from 10% to 90% of signal level.

Figure 4.3 | Propagation delay measurement

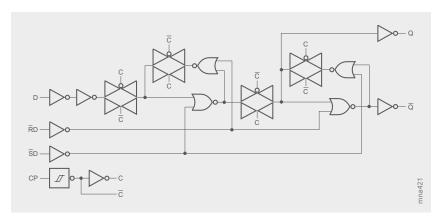

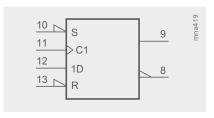

# 4.3 Timing parameters of Flip Flops and Latches

Flip-Flops and Latches are circuits with two stable states that can be used to store state information. Flip-flops can be either level-triggered (asynchronous, transparent or opaque) or edge-triggered (synchronous, or clocked).

**Propagation delay**—Propagation delay for a Flip Flop is the time between the clock event (either rising or falling edge) and the output signal change. As well as for gates, 50% of the signal level is taken for measurement window.

**Setup time t**<sub>SU</sub>—Setup time is the minimum amount of time the data input should be held steady before the clock event (either rising or falling edge), so that the data is reliably sampled by the clock.

**Hold time t**<sub>H</sub>—Hold time is the minimum amount of time the data input should be held steady after the clock event, so that the data is reliably sampled by the clock. Both set-up and hold time are illustrated in Figure 4.4.

The timing parameters set-up and hold time are related to interface signal levels and are caused by internal gate delays, meaning that the clock signal needs to be propagated internally to sample the data signal.

Aperture is the sum of setup and hold time. The data input should be held steady throughout for this period of time.

**Figure 4.4** | The Clock input (CP) to output (Q) propagation delays, clock pulse width, D to CP set-up and hold times and the maximum clock input frequency

Recovery time is the minimum amount of time the asynchronous set or reset input should be inactive before the clock event, so that the data is reliably sampled by the clock. The recovery time for the asynchronous set or reset input is thereby similar to the setup time for the data input.

Removal time is the minimum amount of time the asynchronous set or reset input should be inactive after the clock event, so that the data is reliably sampled by the clock.

## 4.4 Skew definitions

Skew specification measurements are taken at certain conditions which may or, more likely, may not match a specific condition in a system application. However, like other AC specifications the skew specification is valuable as a "benchmark" for estimating certain circuit characteristics. Skew specifications are most valuable in clock–driving applications and applications where duty cycle characteristics are important. Three specific skew specifications are described as follows:

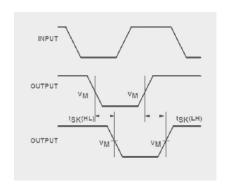

#### 4.4.1 Output Skew tSK(o)

JEDEC definition: "The difference between two concurrent propagation delay times that originate at either a single input or two inputs switching simultaneously and terminate at different outputs."

This skew generally characterizes like–going edges of a single IC only. It compares t<sub>PLH</sub> versus t<sub>PLH</sub> (or t<sub>PHL</sub> vs. t<sub>PHL</sub>) for two or more output data paths. This parameter is very useful in describing output distribution capabilities of a device. tSK(o) would be most valuable to designers using the device as a clock driver, distributing clock signals. tSK(o) could be further subdivided into tSK(LH) (output rising edge) and tSK(HL) (output falling edge) skews, as can be seen in Figure 4.5.

Figure 4.5 | Output skew illustration

**Timing aspects of discrete devices**

#### 4.4.2 Process Skew tSK(x)

JEDEC definition: "The difference between identically specified propagation delay times on any two samples of an IC at identical operating conditions."

This parameter addresses the issue of process variations by quantifying the difference between propagation delays that are caused by lot—to—lot variations. It does not include variations due to differences in supply voltage, operation temperature, output load, input edge rates, etc.

This parameter could be viewed as a tSK(o) skew over several like devices. An example of two devices with process skew is shown in Figure 4.6.

Figure 4.6 | Process Skew

#### 4.4.3 Pulse Skew tSK(p)

JEDEC definition: "The difference between the propagation delay times  $t_{\text{PHL}}$  and  $t_{\text{PLH}}$  when a single switching input causes one or more outputs to switch."

This parameter is used to quantify duty cycle characteristics. Some applications require a nearly perfect 50% duty cycle. tSK(p) specifies the duty cycle retention characteristics of the device.

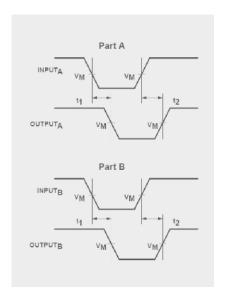

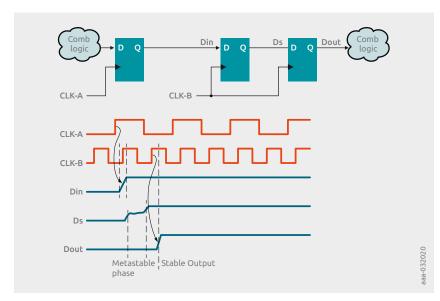

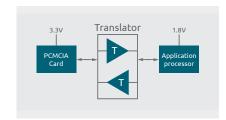

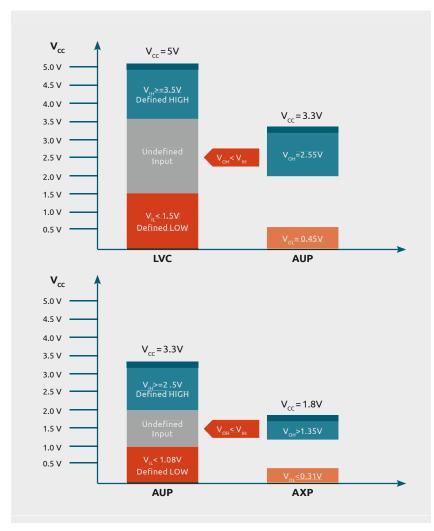

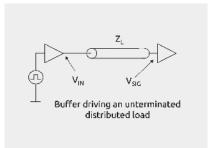

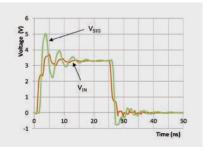

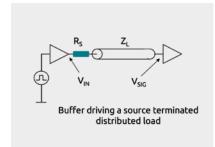

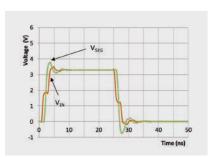

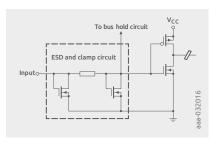

# 4.5 Meta stability and its mitigation