nexperia

May 23, 2019

#### Agenda - MOSFET Parameters and Data Sheets

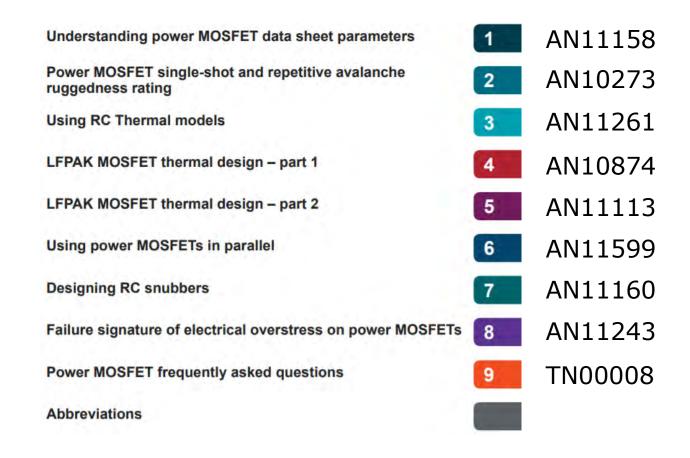

Nexperia MOSFET Applications Handbook Ap Notes of Interest **Basics - MOSFET Part Numbers** Secret Decoder Ring Data Sheet Headers Limiting or Maximum Values Voltage, Current, Power etc. Standard Derating Tables vs. Temperature Robustness SOA – Safe Operating Area and Temperature Derating Avalanche – Single Shot and Repetitive Static and Dynamic Characteristics Extended Topics **Thermal Loss Model** Understanding Snubbers SOA Derating Voltage and Current Scaling Constant Power and Sprito Region

#### **Power MOSFET Applications Handbook**

Nexperia still prints the Big Book

#### • Can be downloaded from the Website.

### **Other Applications Notes**

MOSFET

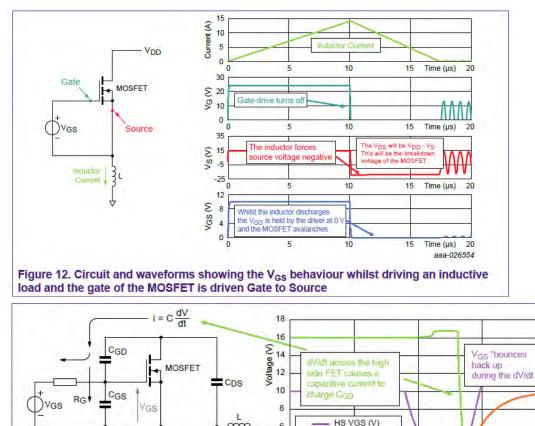

Figure 10. Dynamic behaviour of a MOSFET half bridge

Some of this charge is sunk by the driver but some will charge  $C_{GS}$  and  $V_{GS}$  will increase. Both MOSFETs can

potentially be on at the same time causing a short circuit and current to shoot through the MOSFETs LS VGS (V)

2

Switch Node (V)

6 Time (µs)

aaa-026552

Designing in MOSFETs for safe and reliable gate-drive operation

Rev. 1.0 — 31 March 2017

Application note

- AN90001 Explanation of Gate

Oxide effects over life from TDDB,

Gate Threshold (Vgs) decline over

Temperature / Life.

- Source Inductance Effects Package Inductance of Clip bond LFPAKxx is of minimal effect in Low Voltage applications. However, PCB layout and ground paths are pertinent.

- Parasitics C's and ½ Bridge drive, applicable to Inverters, H-Bridges, Buck Regulators, Motors, etc.

## **MOSFET Basics**

#### May 23, 2019

### **Data Sheet References**

Many Application Notes have been written on MOSFET Data Sheets

#### A MOSFET datasheet generally contains:

- 1. A part number using the secret decoder ring of the supplier.

- 2. A general description including voltage, on-resistance, current ratings and package information

- 3. A table of absolute maximum ratings

- 4. A table of thermal resistance parameters

- 5. A table of electrical characteristics

- 6. Figures, including

- 1. Graphs of typical characteristics

- 2. Diagrams of test circuits

- 7. Package information

#### <u>Nexperia</u>

• <u>AN11158: Understanding power MOSFET data sheet parameters</u>, Nexperia

#### <u>Others</u>

- *How to Read a Datasheet*, Michigan State University ECE480

- <u>How to Read a FET Datasheet</u>, University of Nevada Las Vegas PHYS483

- <u>A Complete Guide to Data Sheets</u>, Allegro Microsystems

- How to Read a Datasheet, Analog Devices

- Infineon OptiMOS Power MOSFET Datasheet Explanation, Infineon

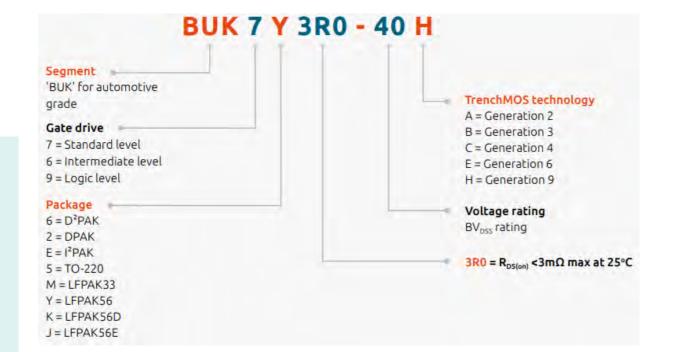

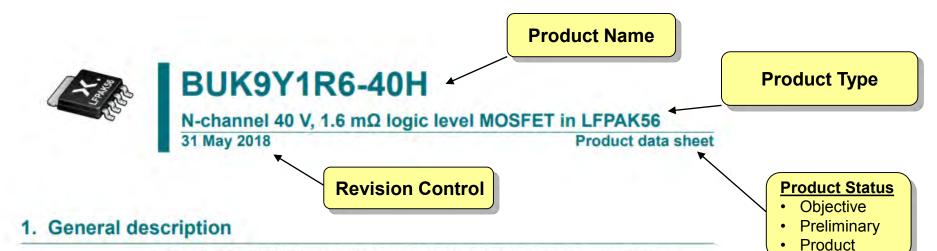

#### Automotive grade MOSFETs nomenclature

Automotive qualified N-channel MOSFET using the latest Trench 9 low ohmic superjunction technology, housed in a robust LFPAK56 package. This product has been fully designed and qualified to meet AEC-Q101 requirements delivering high performance and endurance.

#### 2. Features and benefits

- Fully automotive qualified to AEC-Q101:

- 175 °C rating suitable for thermally demanding environments

- Trench 9 Superjunction technology:

- Reduced cell pitch enables enhanced power density and efficiency with lower R<sub>DSon</sub> in same footprint

- Improved SOA and avalanche capability compared to standard TrenchMOS

- Tight V<sub>GS(th)</sub> limits enable easy paralleling of MOSFETs

- LFPAK Gull Wing leads:

- High Board Level Reliability absorbing mechanical stress during thermal cycling, unlike traditional QFN packages

- Visual (AOI) soldering inspection, no need for expensive x-ray equipment

- Easy solder wetting for good mechanical solder joint

- LFPAK copper clip technology:

- Improved reliability, with reduced Rth and RDSon

- Increases maximum current capability and improved current spreading

|                   | 1.4 Quick refe                   | rence data                                                                                                                            |           |       |       |        |                                               |

|-------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------|--------|-----------------------------------------------|

| Table 1. Q        | uick reference data              |                                                                                                                                       |           |       |       |        | <u>Conditions are</u><br>important!           |

| Symbol            | Parameter                        | Conditions                                                                                                                            | Min       | Тур   | Мах   | Unit   | When comparing                                |

| V <sub>DS</sub>   | drain-source voltage             | T <sub>j</sub> ≥ 25 °C; T <sub>j</sub> ≤ 175 °C                                                                                       | -         | •     | 40    | V      | MOSFETs from                                  |

| ID                | drain current                    | $V_{GS}$ = 5 V; T <sub>mb</sub> = 25 °C; see Figure 1                                                                                 | 녠 -       | -     | 120   | А      | different suppliers,<br>be aware of different |

| Ptot              | total power dissipation          | T <sub>mb</sub> = 25 °C; see Figure 2                                                                                                 | -         | -     | 357   | W      | specification                                 |

| Static charac     | teristics                        |                                                                                                                                       |           |       |       |        | conditions –                                  |

| R <sub>DSon</sub> | drain-source on-state resistance | $V_{GS}$ = 5 V; I <sub>D</sub> = 25 A; T <sub>j</sub> = 25 °C;<br>see <u>Figure 11</u>                                                | -         | 1.35  | 1.6   | mΩ     | Particularly for                              |

| Dynamic cha       | aracteristics                    |                                                                                                                                       |           |       |       |        | front page                                    |

| Q <sub>GD</sub>   | gate-drain charge                | $V_{GS}$ = 5 V; I <sub>D</sub> = 25 A; $V_{DS}$ = 32 V;<br>see <u>Figure 13</u> ; see <u>Figure 14</u>                                | -         | 40.9  | •     | nC     | headline<br>figures.                          |

| [1] Continuous    | s current is limited by packag   | e.<br>ximum voltage betweer                                                                                                           | n drain a | and s | sourc | e that | the device is                                 |

|                   | guarant                          | eed to block in the off                                                                                                               | state (tj | ≥ 25  | 5°C). |        |                                               |

| [D                |                                  | ximum <u>continuous</u> cu<br>nperature is held at 25                                                                                 |           |       |       |        | carry when the mountin<br>y on.               |

| Ptot              |                                  | ximum continuous pow<br>ng base temperature is                                                                                        |           |       |       | ET ca  | n dissipate when the                          |

| RDS(or            |                                  | cource on state resistance) - The typical and maximum drain to sourc ce of the MOSFET in its on-state under the conditions described. |           |       |       |        |                                               |

| QGD               | the `Mill                        | ntity of charge transfe<br>er plateau'. It is part of<br>:) + QGD= QG(tot).                                                           |           |       |       |        | ate pin from 0V, acros                        |

# **Pinning Information**

This section shows how the external outline and pin connections of the MOSFET relate to the internal connections to the die and the schematic symbol.

| Fable 2. | Pinning | j information                        |                                |                | Table 2 | Pinning | information                       |                                            |                |

|----------|---------|--------------------------------------|--------------------------------|----------------|---------|---------|-----------------------------------|--------------------------------------------|----------------|

| Pin      | Symbol  | Description                          | Simplified outline             | Graphic symbol | Pin     | Symbol  | Description                       | Simplified outline                         | Graphic symbol |

|          | G       | gate                                 |                                |                | 1       | S       | source                            | mb                                         | D              |

|          | D       | drain                                | mb                             | ,<br>,         | 2       | S       | source                            | had                                        | (A)            |

|          | S       | source                               |                                |                | 3       | S       | source                            | a                                          | G-(EA          |

| nb       | D       | mounting base;<br>connected to drain |                                | mbb076 S       | 4       | G       | gate                              |                                            | mbb076 S       |

|          |         |                                      | U 2 U<br>1 3<br>SOT404 (D2PAK) |                | mb      | D       | mounting base; connected to drain | 1 2 3 4<br>LFPAK56; Power-<br>SO8 (SOT669) |                |

#### 5. Pinning information

| Pin | Symbol | Description | Simplified outline    | Graphic symbol                         |

|-----|--------|-------------|-----------------------|----------------------------------------|

| 1   | D      | drain       |                       | D                                      |

| 2   | D      | drain       |                       |                                        |

| 3   | G      | gate        | 2                     | G-CT-Y                                 |

| 1   | S      | source      | 3 8 4                 | s                                      |

| 5   | D      | drain       | Transparent top view  | 017aaa094                              |

| 6   | D      | drain       | DFN2020MD-6 (SOT1220) | 11 C C C C C C C C C C C C C C C C C C |

| 7   | D      | drain       |                       |                                        |

| 3   | S      | source      |                       |                                        |

Mounting base or backside tab is normally the Drain in both N and P Channel MOSETs. And this is the primary thermal path.

# MOSFET Limiting Values

May 23, 2019

# **Limiting Values**

#### 5. Limiting values

#### Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol               | Parameter                                       | Conditions                                                                                                                                                          | Min   | Max  | Unit |

|----------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|

| V <sub>DS</sub>      | drain-source voltage                            | T <sub>j</sub> ≥ 25 °C; T <sub>j</sub> ≤ 175 °C                                                                                                                     | - (   | 40   | V    |

| V <sub>DGR</sub>     | drain-gate voltage                              | R <sub>GS</sub> = 20 kΩ                                                                                                                                             | -     | 40   | V    |

| V <sub>GS</sub>      | gate-source voltage                             | DC                                                                                                                                                                  | -10   | 10   | V    |

|                      |                                                 | Pulsed                                                                                                                                                              | -15   | 15   | V    |

| I <sub>D</sub>       | drain current                                   | T <sub>mb</sub> = 25 °C; V <sub>GS</sub> = 5 V; see Figure 1                                                                                                        | [1] - | 120  | А    |

|                      |                                                 | T <sub>mb</sub> = 100 °C; V <sub>GS</sub> = 5 V; see Figure 1                                                                                                       | 11 -  | 120  | Α    |

| IDM                  | peak drain current                              | T <sub>mb</sub> = 25 °C; pulsed; t <sub>p</sub> ≤ 10 μs;<br>see <u>Figure 4</u>                                                                                     | -     | 1363 | А    |

| P <sub>tot</sub>     | total power dissipation                         | T <sub>mb</sub> = 25 °C; see Figure 2                                                                                                                               | -     | 357  | W    |

| T <sub>stg</sub>     | storage temperature                             |                                                                                                                                                                     | -55   | 175  | °C   |

| Tj                   | junction temperature                            |                                                                                                                                                                     | -55   | 175  | °C   |

| Source-drai          | in diode                                        |                                                                                                                                                                     |       |      |      |

| ls                   | source current                                  | T <sub>mb</sub> = 25 °C                                                                                                                                             | 11 -  | 120  | А    |

| ISM                  | peak source current                             | pulsed; t <sub>p</sub> ≤ 10 µs; T <sub>mb</sub> = 25 °C                                                                                                             | -     | 1363 | А    |

| Avalanche            | ruggedness                                      |                                                                                                                                                                     |       |      |      |

| E <sub>DS(AL)S</sub> | non-repetitive drain-source<br>avalanche energy | I <sub>D</sub> = 120 A; V <sub>sup</sub> ≤ 40 V; R <sub>GS</sub> = 50 Ω;<br>V <sub>GS</sub> = 5 V; T <sub>j</sub> (init) = 25 °C; unclamped;<br>see <u>Figure 3</u> | 213 - | 1008 | mJ   |

Again - conditions are important to make a fair comparison between competing parts.

- Operation outside these limits is not guaranteed – except for avalanche ruggedness.

- They are all temperature dependent. They are quoted at Tj = 25°C and must be de-rated for Tj values <> 25°C.

- Datasheet de-rating graphs must be applied to check that the MOSFET is suitable for the worst-case application conditions).

Temperature dependence

# **Limiting Values**

| V <sub>DS</sub>   | The maximum voltage the device is guaranteed to withstand between the Drain and Source pins in the OFF-state <b>over the temperature range 25°C to 175°C.</b>                                                                                                              |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>GS</sub>   | The maximum voltage the device is guaranteed to withstand between the Gate and Source pins. (Note that TDDB also must be considered).                                                                                                                                      |

| V <sub>DGR</sub>  | The maximum drain - gate voltage is the same value as the maximum $V_{\text{DS}}$ voltage.                                                                                                                                                                                 |

| I <sub>D</sub>    | The maximum CONTINUOUS D.C. current that the MOSFET can handle under the specified conditions. <b>This is often limited by the package rather than the silicon die.</b><br>Some manufacturers state the theoretical silicon limit instead of package limit so be careful ! |

| I <sub>DM</sub>   | The maximum current that the MOSFET can safely carry for a pulse time of $\leq$ <b>10 µs.</b>                                                                                                                                                                              |

| P <sub>tot</sub>  | The maximum continuous MOSFET power dissipation when its <b>mounting base</b><br><b>temperature is HELD at 25°C</b> .<br>Some MOSFET suppliers use different conditions so 'normalisation' is needed to do a valid comparison.                                             |

| $T_{stg} / T_{j}$ | These limit values define the safe <b>storage</b> and <b>junction operating</b> temperature range of the MOSFET.                                                                                                                                                           |

| I <sub>S</sub>    | The maximum continuous current of the MOSFET body diode. The same considerations apply as for $\rm I_{\rm D}$                                                                                                                                                              |

| I <sub>SM</sub>   | The maximum current that the MOSFET body diode is guaranteed to carry for a pulse time of ${\leq}10~\mu\text{s}.$                                                                                                                                                          |

#### SOA Curve

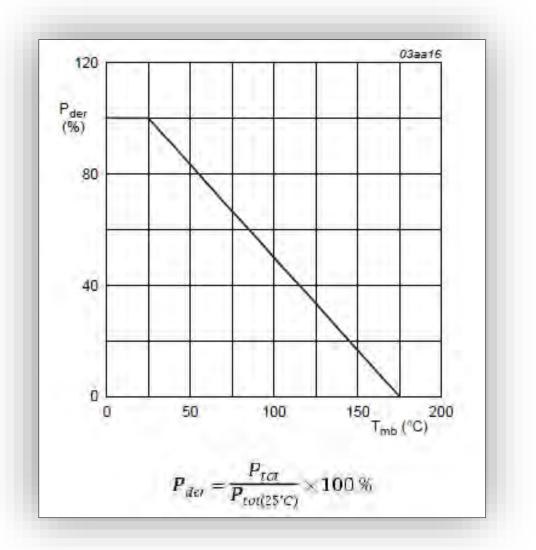

# **Power Dissipation Derating**

- The maximum (steady state) power dissipation allowed in the MOSFET is the power that would raise its junction temperature to 175°C when its mounting base temperature is held at 25°C.

- At T<sub>mb</sub> = 25°C, 100% of the power (357W) can be dissipated. This would cause a 150°C (K) Tj rise.

- At T<sub>mb</sub> = 100°C, 50% of the power (178W) can be dissipated. This would cause a 75°C (K) Tj rise.

- At T<sub>mb</sub> = **175°C**, power dissipation >**0W** in the die would result in a Tj > 175°C.

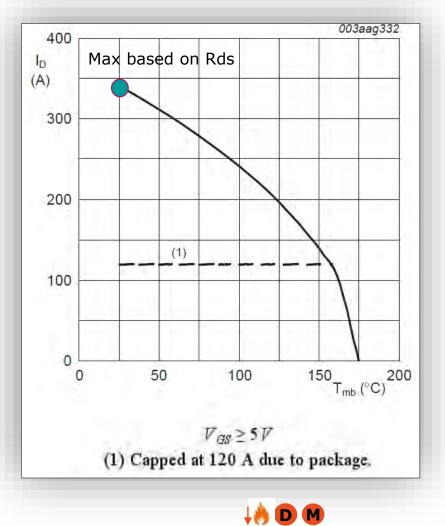

## **Continuous Drain Current Derating**

- Continuous drain current is limited to a maximum of **120A** by the package.

- At high mounting base temperatures, maximum continuous drain current is limited by maximum die temperature rather than the package limit.

- This limit assumes that the die R<sub>dson</sub> is at its maximum and die temperature is 175°C (Rds<sub>(ON)\_max.@175°C</sub>)

- The maximum current at a given mounting base temperature can be calculated from the equation

$\mathbf{I}_{\mathsf{D}} = \sqrt{(\mathsf{P} / \mathsf{Rds}_{(\mathsf{ON})\_\mathsf{max}.@175^{\circ}\mathsf{C}})}$

- **P** is derived from **P**<sub>tot</sub> by applying the previous graph

- **Rds**(ON)\_max.@175°C is stated on the datasheet (see slide 13)

# MOSFET Robustness

May 23, 2019

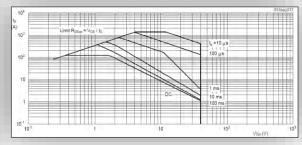

# Safe Operating Area - SOA

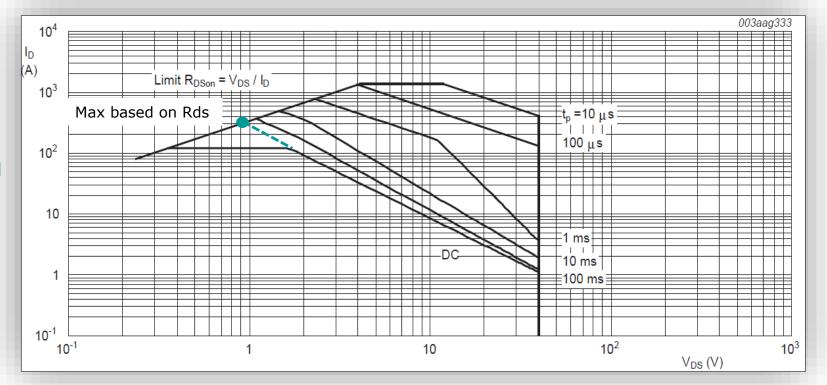

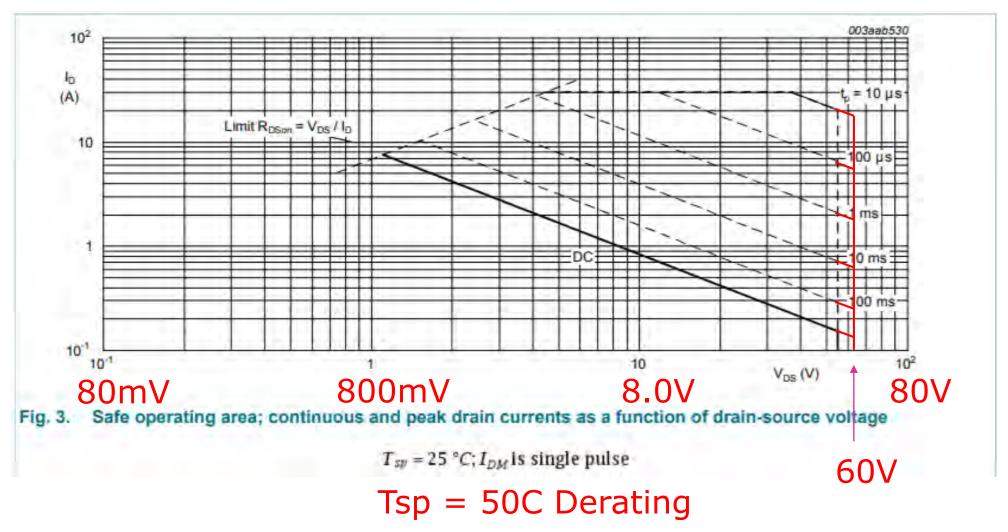

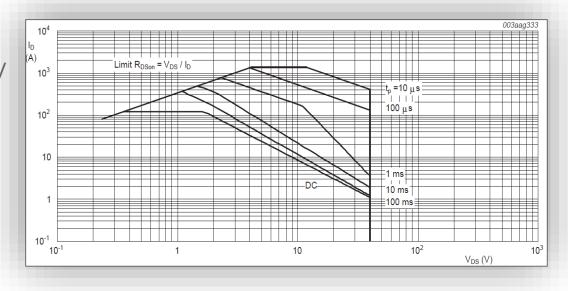

- The SOA curves show the permitted voltage – current – time envelope limit for MOSFET LINEAR MODE operation. In this zone the MOSFET is not fully enhanced ( it is between its OFF and ON states)

- The SOA lines are for a single rectangular power pulse with initial T<sub>j</sub> = 25°C; initial Tmb = 25°C.

- If initial Tj is >25°C the graph must be de-rated in a similar way to power and current de-rating. If possible this should be done by reducing V<sub>DS</sub>.

- Often the power pulse will not be rectangular (e.g. inductive load active clamping). Nexperia Applications Engineers

would be happy to advise in such cases.

### **SOA Derating Example (Vds Scale Method)**

#### BUK7880-55 Example

- SOA current pulse is a square wave. Therefore with constant voltage and a constant Current,

V \* I = a constant Power.

- The die heating is determined by the RC thermal model and is a scalable function with respect to Power. (i.e. – half the Power for a fixed pulse time will yield half the thermal rise at the die). The SOA curve represents a Power Level for a fixed pulse time, or a fixed amount of energy.

- Scalable function: f(ax) = af(x)

- The SOA curve is for a starting temp of 25C. The max die temp is 150C. This is a temperature differential of 125C.

- For a 50C starting temperature for single event SOA pulse, the differential die temp allowed is 150C 50C = 100C. Therefore the energy to get a die temp of 150C is

- 100C / 125C = 80%

- As V \* I = Power, we can adjust the 25C x-axis Voltage scale to achieve an 80% energy level in the same pulse period at 50C, as shown.

### **SOA Curve for BUK7880-55A**

Scaled to 80% for 50C Solder Point starting temperature

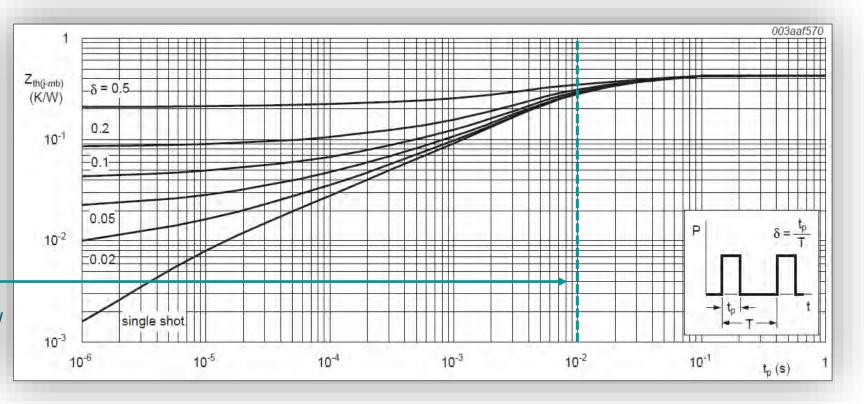

# **Thermal Characteristics**

- Thermal impedance characteristics can be used to estimate MOSFET junction temperature rise caused by a single power pulse or a sequence of power pulses.

- At pulse durations where t<sub>p</sub> > 10<sup>-</sup>

<sup>2</sup>s, Zth = Rth (steady state thermal resistance)

- At pulse durations < 10<sup>-2</sup>s heat flow out of the die junction depends more on the die thermal capacity.

- T<sub>j\_rise</sub> = Z<sub>th(j-mb)</sub> \* P; This temperature rise must be added to the initial mounting base temperature to give the actual junction temperature.

- Thermal modelling using SPICE or Flotherm is often easier, more accurate and more informative.

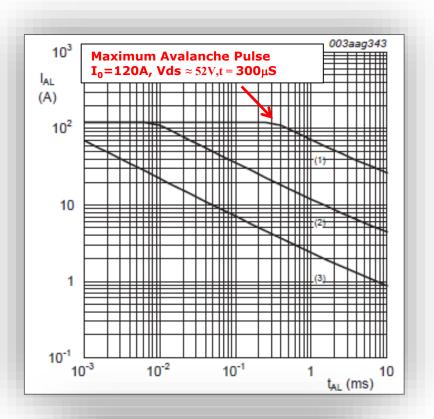

# **Limiting Values - Avalanche**

| EDS(AL)S                                             | • The maximum sing                                                                                                                                                                                                                                            | gle avalanche energy pulse allowed with t                                     | he conditions      | specifie | ed.  |  |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------|----------|------|--|--|--|

| non-repetitive drain-<br>source avalanche<br>energy) | This is the avalanche energy pulse that would cause the junction temperature of the MOSFET to rise from 25°C to 175°C while its mounting base temperature is held at 25°C. The avalanche energy is specified for the maximum continuous drain current.        |                                                                               |                    |          |      |  |  |  |

|                                                      | <ul> <li>Some vendors specify the avalanche energy for a lower current and longer duration, giving a<br/>apparent increase in avalanche energy. However this is only because the heat has a more<br/>time to dissipate.</li> </ul>                            |                                                                               |                    |          |      |  |  |  |

| DS(AL)R                                              | <ul> <li>The maximum avalanche energy allowed when the avalanche event is repetitive.</li> </ul>                                                                                                                                                              |                                                                               |                    |          |      |  |  |  |

| (repetitive drain-source<br>avalanche energy)        | <ul> <li>This parameter is only listed on Nexperia MOSFET data sheets where the repetitive avalanche<br/>capability has been verified.</li> </ul>                                                                                                             |                                                                               |                    |          |      |  |  |  |

|                                                      | <ul> <li>The thermal requirements for repetitive avalanche events are that the repetitive limit line on<br/>the avalanche energy SOA graph should not be exceeded and <i>average</i> MOSFET junction<br/>temperature <b>must not exceed 170°C.</b></li> </ul> |                                                                               |                    |          |      |  |  |  |

|                                                      | • The $\Delta T$ caused by                                                                                                                                                                                                                                    | the avalanche is 10°C (10K); Tj cycles be                                     | tween <b>165°C</b> | and 17   | ′5°C |  |  |  |

| Avalanche rugg                                       | ggedness                                                                                                                                                                                                                                                      |                                                                               |                    |          |      |  |  |  |

| E <sub>DS(AL)S</sub>                                 | non-repetitive drain-<br>source avalanche<br>energy                                                                                                                                                                                                           | $T_{j(init)} = 25 \ ^{\circ}C; I_D = -0.85 \ A; DUT in avalanche (unclamped)$ | -                  | 28       | mJ   |  |  |  |

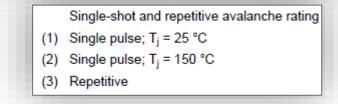

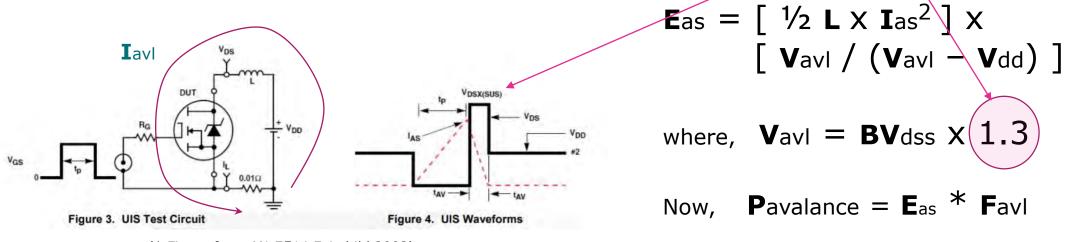

# **Avalanche Ruggedness**

- In an avalanche event Vds is taken above its limiting value usually by current fed from an unclamped inductive load. The MOSFET Body Diode conducts reverse (avalanche) current.

- To procure the avalanche, the MOSFET is initially switched ON ( $V_{gs}$ =5V); load current ramps up (to 120A). It is then switched OFF by pulling  $V_{GS}$  to zero; ( $R_{GS}$ = 50 $\Omega$ ).

- $E_{DS(AL)S} = 1008$ mJ causes Tj to rise from 25°C to 175°C.

- Avalanche voltage (BVDSS) ~ 1.3x V<sub>DS\_max</sub>

- BVDSS increases (slightly) as die temperature increases.

- All Nexperia Automotive Power MOSFETs are subjected to TWO high energy avalanche pulses after packaging to verify their avalanche ruggedness capability.

# Static Characteristics

May 23, 2019

# **Static Characteristics**

- Static characteristics define the steady state voltage, current and resistance ranges of the MOSFET over its full operating temperature range.

- They are the key parameters to consider when specifying a MOSFET for an application.

- Typical values are also given but limit values should be used for design calculations.

| Symbol                     | Parameter                           | Conditions                                                                                                                       | Min | Тур  | Мах  | Uni |

|----------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|------|------|-----|

| Static chara               | acteristics                         |                                                                                                                                  |     |      |      |     |

| V <sub>(BR)DSS</sub>       | drain-source<br>breakdown voltage   | $I_D$ = 250 µA; $V_{GS}$ = 0 V; $T_j$ = 25 °C                                                                                    | 40  | -    | -    | V   |

|                            |                                     | $I_D$ = 250 µA; $V_{GS}$ = 0 V; $T_j$ = -55 °C                                                                                   | 36  | -    | -    | V   |

| $V_{\text{GS}(\text{th})}$ | gate-source threshold<br>voltage    | I <sub>D</sub> = 1 mA; V <sub>DS</sub> = V <sub>GS</sub> ; T <sub>J</sub> = 25 °C;<br>see <u>Figure 9</u> ; see <u>Figure 10</u> | 1.4 | 1.7  | 2.1  | V   |

|                            |                                     | I <sub>D</sub> = 1 mA; V <sub>DS</sub> = V <sub>GS</sub> ; T <sub>J</sub> = -55 °C;<br>see <u>Figure 9</u>                       | -   | -    | 2.45 | V   |

|                            |                                     | I <sub>D</sub> = 1 mA; V <sub>DS</sub> = V <sub>GS</sub> ; T <sub>j</sub> = 175 °C;<br>see <u>Figure 9</u>                       | 0.5 | -    | -    | V   |

| I <sub>DSS</sub>           | drain leakage current               | $V_{DS}$ = 40 V; $V_{GS}$ = 0 V; $T_j$ = 25 °C                                                                                   | -   | 0.13 | 1    | μA  |

|                            |                                     | $V_{DS}$ = 40 V; $V_{GS}$ = 0 V; $T_j$ = 175 °C                                                                                  | -   | -    | 500  | μA  |

| I <sub>GSS</sub>           | gate leakage current                | $V_{GS}$ = 10 V; $V_{DS}$ = 0 V; $T_j$ = 25 °C                                                                                   | -   | 2    | 100  | nA  |

|                            |                                     | $V_{GS}$ = -10 V; $V_{DS}$ = 0 V; $T_j$ = 25 °C                                                                                  | -   | 2    | 100  | nA  |

| R <sub>DSon</sub>          | drain-source on-state<br>resistance | V <sub>GS</sub> = 5 V; I <sub>D</sub> = 25 A; T <sub>j</sub> = 25 °C;<br>see <u>Figure 11</u>                                    | -   | 1.35 | 1.6  | mΩ  |

|                            |                                     | V <sub>GS</sub> = 10 V; I <sub>D</sub> = 25 A; T <sub>j</sub> = 25 °C;<br>see <u>Figure 11</u>                                   | -   | 1.17 | 1.4  | mΩ  |

|                            |                                     | V <sub>GS</sub> = 5 V; I <sub>D</sub> = 25 A; T <sub>j</sub> = 175 °C;<br>see Figure 12; see Figure 11                           | -   | -    | 3.1  | mΩ  |

Temperature dependence

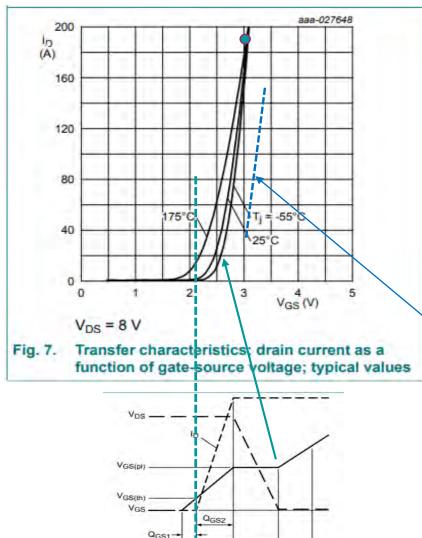

## **Transfer Characteristics**

G(tot)-

003aaa508

- The Transfer Characteristics of the MOSFET shows its 'gain' how I<sub>D</sub> increases as V<sub>GS</sub> increases.

- It shows the 25°C and 175°C characteristics

- They are more separated at low V<sub>GS</sub> values (near V<sub>GS(th)</sub>) but merge together at a higher V<sub>GS</sub> point (V<sub>GS</sub> ≈ 3.3V; I<sub>D</sub> ≈ 320A).

This is the Zero Temperature Coefficient (I\_zTC) point.

- This is of further interest in Linear Hot Spot failure. Nexperia have developed Trench MOSFETs that operate reliably in 'linear mode'.

- At **I** < **I**<sub>\_zTC</sub> thermal instability due to **positive electrothermal feedback** can occur.

- The slope at 25C across the Miller Plateau is used to define the Transconductance - gm = delta A / delta V

- This is not usually a problem with (fast) switching, but careful design is needed for quasi steady state `linear mode' applications such as clamping.

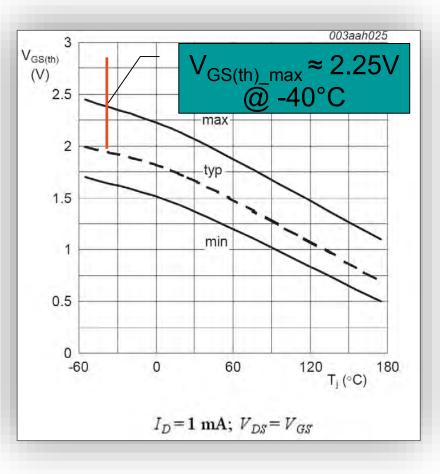

# **VGS Threshold Characteristics**

- Gate Source threshold voltage is the 'gate drive' voltage needed to <u>start</u> to turn the MOSFET **ON**.

- More critically it is the limit above which the MOSFET may conduct some current (and dissipate some power). Vg-s MUST be kept below this level to guarantee that it is held **OFF**.

- The gate drive circuit must accommodate application conditions (noise, high temperature etc.) that could cause the MOSFET to start to turn ON when it should be held OFF.

- V<sub>GS(th)</sub> must be above 2.25V at -40C to begin to turn the device on.

- V<sub>GS(th)</sub> decreases with Temperature. The BUK<u>9</u>61R6-40E is a `Logic Level' MOSFET. At 175°C V<sub>GS(th)</sub> is guaranteed to be at least 0.5V.

- In applications needing more margin, 'Standard Level' MOSFETs (BUK7\*\*\*) may be a better choice. At 175°C V<sub>GS(th)</sub> is guaranteed to be at least 1.0V.

#### Typical Logic Level

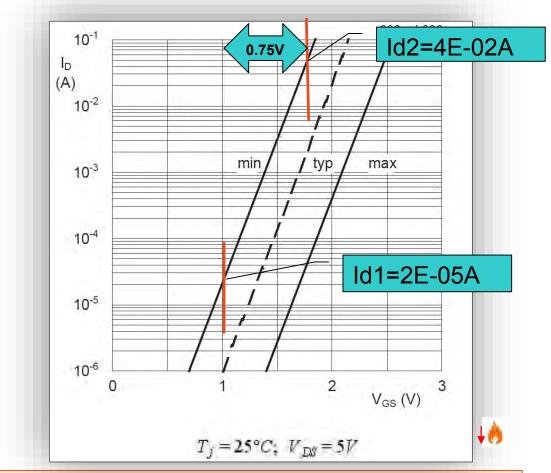

### **Threshold Ids vs Vgs**

*Customer Question Example: We have had a concern from the Boost converter chip supplier.*

#### We need to ensure that the FET can achieve an ID of 2A with a VGS of 3V over temp from -40°C to 105°C.

Can the BUK98150-55A and BUK9880-55A achieve this requirement. The graphs below don't show the -40°C curves for Id Vs VGS. I know VGS goes up with lower Temp's.

#### Can we get a updated graph with worst case curves for VGS Vs ID over temp from -40°C to 150°C (Tj) as below.

- This graph shows how drain current  $(I_D)$  increases exponentially with increasing  $V_{GS}$ . (y-axis log, x-axis linear as compared to Transfer Characteristic graph)

- Note that the difference between the minimum and maximum  $V_{GS}$  voltage for a given drain current is constant and independent of  $I_D$ .

- It can be used with the previous graph to match the MOSFET and its load to its gate driver

Vgsth max @ -40C = 2.25V (see last slide) ∆V between 2.25V and 3V = 0.75V  $\Delta I_D$  for  $\Delta V_{(0.75V)}$  or,  $k_{I(0.75V)} = I_{D2}/I_{D1} = 2000$ (from graph above)  $I_D$  at 3V =>  $I_{D(@Vgs=2.25V)}$ \*2000  $I_{dmin(@Vgs=3V)} = 1mA*2000 = 2A$  ✓

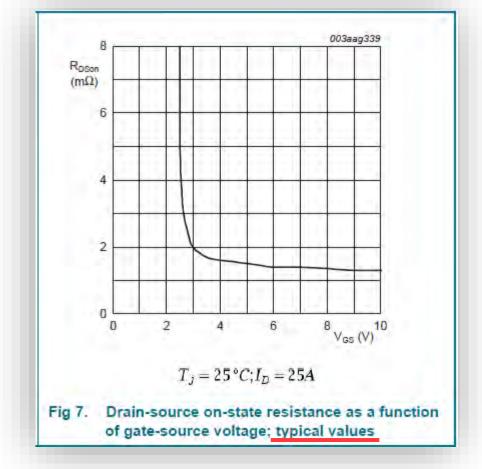

# Drain Source On-State Resistance Rds ON

R<sub>DS(on)</sub> (Drain-Source on-state resistance) is often the most important MOSFET parameter.

It determines how good a closed-switch the 'ON' MOSFET is. It is usually the key factor **determining the power loss and efficiency** of the circuit.

- ALL graphs where the title is followed by 'typical values' should not be used for design data. They will not be worst case.

- They are usually shown with junction temperature = 25°C. This will rarely be the case with automotive applications.

- They are an **indication** of how the MOSFET characteristics are related.

## Drain Source On-State Resistance Rds ON over Temperature

- This graph is `normalised' which means that the  $Tj = 25^{\circ}C R_{DS(on)}$  is equated to `1'.

- Its value at other temperatures within its operating range is scaled by the factor 'a'.

- This graph is valid for the specific technology (T6 40V Logic Level in this case) and <u>can</u> be used for design parameter estimation.

- e.g. at 105°C the  $R_{DS(on)}$  for this technology will be 1.5 X the 25°C  $R_{DS(on)}$  value.

- For the BUK<u>9</u>61R6-40E the maximum 25°C  $R_{DS(on)}$  value is **1.6m** $\Omega$  (with  $V_{gs} = 5V$ ).

- Max. 105°C R<sub>DS(on)</sub> value is therefore 2.4mΩ.

#### **Overdriving**

- Driving it with  $V_{gs} = 10V$ , 25°C  $R_{DS(on)} = 1.4m\Omega$

- With  $V_{gs} = 10V$ ,  $T_j = 105^{\circ}C R_{DS(on)} = 2.1m\Omega$

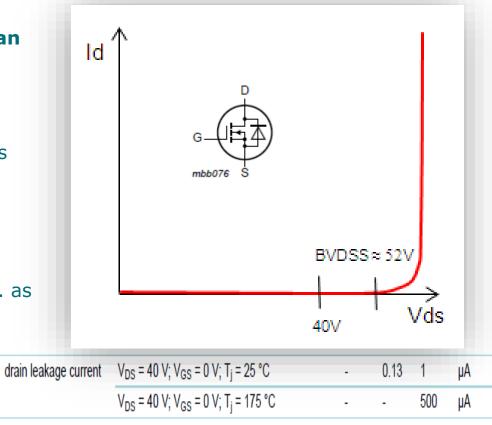

## Ids - Drain Source Leakage Current

DSS

- This current flows through the (reverse biased) body diode. This diode is an integral part of the MOSFET structure. It cannot be omitted.

- The leakage current is highly temperature dependent; it approximately doubles for every 10°C rise in T<sub>i</sub>.

- As with any junction diode it starts to conduct reverse current when Vds reaches a critical value (BVDSS).

- BVDSS (or V<sub>(BR)DSS</sub>) is nominally 1.3 times the rated V<sub>DS</sub> (52V for a 40V MOSFET) at 25°C. Reverse current increases disproportionately above this voltage.

- The breakdown voltage (V<sub>(BR)DSS</sub>) has a positive temperature coefficient, i.e. as temperature increases, BVDSS increases.

- + At low temperatures  $V_{(BR)DSS}$  may be  $\underline{\textbf{less than}}~V_{DS\_max}$  .

| Symbol               | Parameter         | Conditions                                                              | Min | Тур | Max | Unit |

|----------------------|-------------------|-------------------------------------------------------------------------|-----|-----|-----|------|

| Static charac        | teristics         |                                                                         |     |     |     |      |

| V <sub>(BR)DSS</sub> | drain-source      | I <sub>D</sub> = 250 μA; V <sub>GS</sub> = 0 V; T <sub>j</sub> = 25 °C  | 40  | -   | -   | V    |

|                      | breakdown voltage | I <sub>D</sub> = 250 μA; V <sub>GS</sub> = 0 V; T <sub>j</sub> = -55 °C | 36  | -   | -   | V    |

NOTE: Nexperia give Idss conditions At max.  $V_{ds}$ = 40V; max. Tj= 175°C

## **Idss – Example – Competitor**

As mentioned previously, be aware of the conditions that the MOSFET parameters are specified at.

This is a 40V MOSFET but the maximum Idss condition is given at  $V_{ds}$ = 18V; Tj = 85°C.

These conditions are well below the maximum allowed ratings (40V; 175°C).

IDSS roughly doubles for every 10°C rise in temperature.

Although this 'headline'  $20\mu A$  figure looks better than the  $500\mu A$  Nexperia figure, it is in fact **WORSE**

| Parameter                                                                                                     | Symbol                                                    | Conditions                                   | Values   |                  |               |         |

|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------|----------|------------------|---------------|---------|

|                                                                                                               |                                                           |                                              | min.     | typ.             | max.          |         |

| Thermal characteristics <sup>2)</sup>                                                                         |                                                           |                                              |          |                  |               |         |

| Thermal resistance, junction - case R <sub>thJC</sub> -                                                       |                                                           |                                              |          |                  | 1.0           | K/W     |

| Thermal resistance, junction -<br>ambient, leaded                                                             | R <sub>thJA</sub>                                         | -                                            | - 3      | 14               | 62            |         |

| SMD version, device on PCB                                                                                    | R <sub>thJA</sub>                                         | minimal footprint                            |          |                  | 62            |         |

|                                                                                                               | 1.0                                                       | 6 cm <sup>2</sup> cooling area <sup>3)</sup> | Net of a | la sta           | 40            |         |

|                                                                                                               |                                                           |                                              |          |                  |               |         |

| Electrical characteristics, at T <sub>j</sub> =25<br>Static characteristics<br>Drain-source breakdown voltage | 1                                                         | otherwise specified                          | 40       |                  | -             | V       |

| Static characteristics                                                                                        | °C, unless<br>V <sub>(BR)DSS</sub><br>V <sub>GS(th)</sub> |                                              | 40       | -<br>3.0         | - 4.0         | V       |

| Static characteristics<br>Drain-source breakdown voltage                                                      | V (BR)DSS                                                 | V <sub>GS</sub> =0V, / <sub>D</sub> = 1mA    |          | -<br>3.0<br>0.04 | -<br>4.0<br>1 | ν<br>μA |

# **Dynamic Characterists**

May 23, 2019

# **Dynamic Characteristics**

- Dynamic characteristics are parameters that affect switching performance.

- The MOSFET gate is electrically insulated from the channel structure by the gate oxide.

- However, it is capacitively coupled to the channel structure.

- The electric field created by

V<sub>GS</sub> controls the conductivity of the channel – hence R<sub>DS(on)</sub>.

| Dynamic c           | haracteristics                  |                                                                                                               |   |       |       |    |

|---------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------|---|-------|-------|----|

| Q <sub>G(tot)</sub> | total gate charge               | I <sub>D</sub> = 25 A; V <sub>DS</sub> = 32 V; V <sub>GS</sub> = 5 V;                                         | - | 120   | -     | nC |

| Q <sub>GS</sub>     | gate-source charge              | see Figure 13; see Figure 14                                                                                  | - | 26.9  | -     | nC |

| Q <sub>GD</sub>     | gate-drain charge               |                                                                                                               | - | 40.9  | -     | nC |

| Ciss                | input capacitance               | V <sub>GS</sub> = 0 V; V <sub>DS</sub> = 25 V; f = 1 MHz;                                                     | - | 12300 | 16400 | pF |

| Coss                | output capacitance              | $T_j = 25 \text{ °C}; \text{ see } \frac{\text{Figure } 15}{15}$                                              | - | 1530  | 1840  | pF |

| C <sub>rss</sub>    | reverse transfer<br>capacitance |                                                                                                               | - | 740   | 1020  | pF |

| t <sub>d(on)</sub>  | turn-on delay time              | $V_{DS} = 30 \text{ V}; \text{ R}_{L} = 1.2 \Omega; \text{ V}_{GS} = 5 \text{ V};$<br>$R_{G(ext)} = 5 \Omega$ | - | 95    | -     | ns |

| t <sub>r</sub>      | rise time                       |                                                                                                               | - | 118   | -     | ns |

| t <sub>d(off)</sub> | turn-off delay time             |                                                                                                               | - | 195   | -     | ns |

| t <sub>f</sub>      | fall time                       |                                                                                                               | - | 119   | -     | ns |

| L <sub>D</sub>      | internal drain<br>inductance    | from upper edge of drain mounting base to center of die                                                       | - | 2.5   | -     | nH |

| Ls                  | internal source<br>inductance   | from source lead to source bonding<br>pad                                                                     | - | 7.5   | -     | nH |

| Source-dra          | ain diode                       |                                                                                                               |   |       |       |    |

| V <sub>SD</sub>     | source-drain voltage            | I <sub>S</sub> = 25 A; V <sub>GS</sub> = 0 V; T <sub>j</sub> = 25 °C;<br>see <u>Figure 16</u>                 | - | 0.77  | 1.2   | V  |

| t <sub>rr</sub>     | reverse recovery time           | $I_{\rm S}$ = 20 A; dI_{\rm S}/dt = -100 A/µs; V_{GS} = 0 V;                                                  | - | 57    | -     | ns |

| Qr                  | recovered charge                | V <sub>DS</sub> = 25 V                                                                                        | - | 97    | -     | nC |

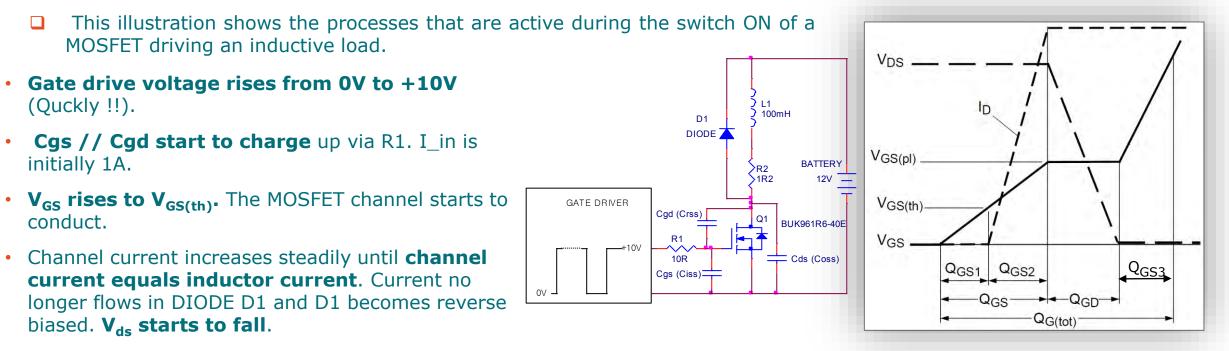

# **The Switching Process**

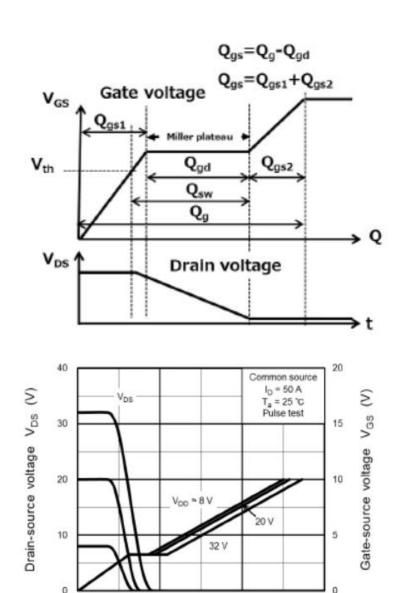

- Input current now diverts into  $C_{qd}$  as  $V_{ds}$  decreases. Current flow into  $C_{qs}$  reduces and the 'Miller plateau' phase starts.

- This continues until  $V_{ds}$  drops to  $I_D * R_{DS(on)}$  (  $\approx 0V$ ).  $C_{ds}$  ( $C_{oss}$ ) has now fully discharged through the MOSFET. **Input current** continues to flow into  $C_{gs}$  and  $C_{gd}$  even though the MOSFET is now fully enhanced (ON). ٠

- To turn the MOSFET OFF, gate drive voltage is set to 0V. ٠

- Charge starts to flow out through R1 and the reverse sequence of events takes place. When V<sub>GS</sub> drops below V<sub>GS(th)</sub>, ٠ channel current will stop flowing.

•

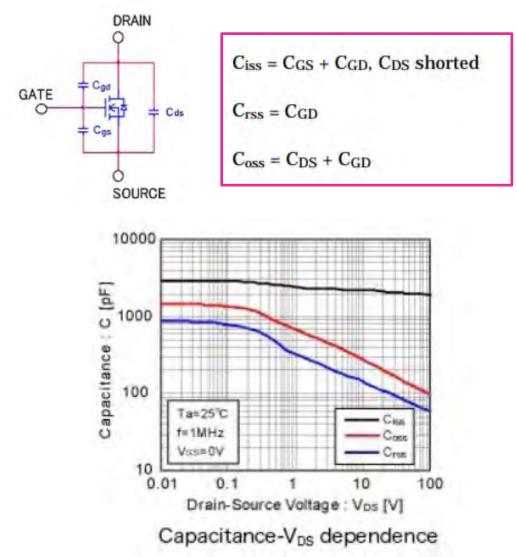

## **MOSFET Capacitance and Charges**

- The MOSFET capacitances are associated with structures within the MOSFET die. They are complex.

- C<sub>ISS</sub> is associated primarily with the gate oxide layer. Its thickness is fixed;

C<sub>ISS</sub> is not voltage dependent (Stable over Vds)

- C<sub>RSS</sub> & C<sub>OSS</sub> are associated with the reverse biased (body diode) junction, they depend on `depletion layer' thickness (which depends on V<sub>DS</sub>).

High V<sub>DS</sub> = thick depletion layer = low capacitance. Low V<sub>DS</sub> = thin depletion layer = high capacitance.

- Due to the voltage dependence of the capacitances, it is often easier to use gate charge transferred to / from the capacitances as design parameters.

- To make valid comparisons between MOSFETs, the measurement conditions

for the parameters must also be comparable

$\int_{C_{p}}^{0} \int_{0}^{0} \int_{0}^{0}$

Fig 15. Input, output and reverse transfer capacitances as a function of drain-source voltage; typical values

### **Dynamic Capacitance**

**Ciss, Coss, Crss** relate to the parasitic capacitances referred to as the as dynamic characteristics.

**Ciss** is the input capacitance, and is the capacitance obtained by totaling the gate-source capacitance Cgs and the gate-drain capacitance Cgd; it is the capacitance of the MOSFET as a whole, as seen from the input. This capacitance must be driven (charged) in order to cause the MOSFET to operate, and so is a parameter of importance when studying the drivability of an input device or input losses. Qg is the amount of charge necessary to drive (charge) Ciss.

**Coss** is the output capacitance, obtained by adding the drain-source capacitance Cds and the gate-drain capacitance Cgs, and is the total capacitance on the output side. If Coss is large, a current arising due to Coss flows at the output even when the gate is turned off, and time is required for the output to turn off completely.

**Crss** is the gate-drain capacitance Cgd itself, and is called the feedback capacitance or the reverse transfer capacitance. If Crss is large, the rise in drain current is delayed even after the gate is turned on, and the fall in current is delayed after the gate is turned off. In other words, this parameter greatly affects switching speed. Qgd is the charge amount necessary to drive (charge) Crss.

### **Gate Charge Definitions**

Electrical characteristics of MOSFETs (Charge Characteristic  $Q_g/Q_{gs1}/Q_{gd}/Q_{SW}/Q_{OSS}$ )

#### > Gate charge

Because the Gate (G) input terminal of a MOSFET is insulated, the amounts of charge Q seen from the Gate are important characteristics. Figure 1.5 illustrates the definitions of gate charge characteristics.

#### > Total gate charge Qg

The amount of charge to apply voltage (from zero to designated voltage) to gate

#### Gate-source charge 1 Q<sub>gs1</sub>

The amount of charge required for a MOSFET to begin to turn on (before dropping drain-source voltage)

#### > Gate-drain charge Q<sub>gd</sub>

The amount of gate charge charged in the Miller plateau

#### Gate switch charge Q<sub>sw</sub>

The amount of charge stored in the gate capacitance from when the gate-source voltage has reached  $V_{th}$  Until the end of the Miller plateau

#### Output charge Qoss

Drain-source charge

40

80

Total gate charge Q<sub>n</sub> (nC)

120

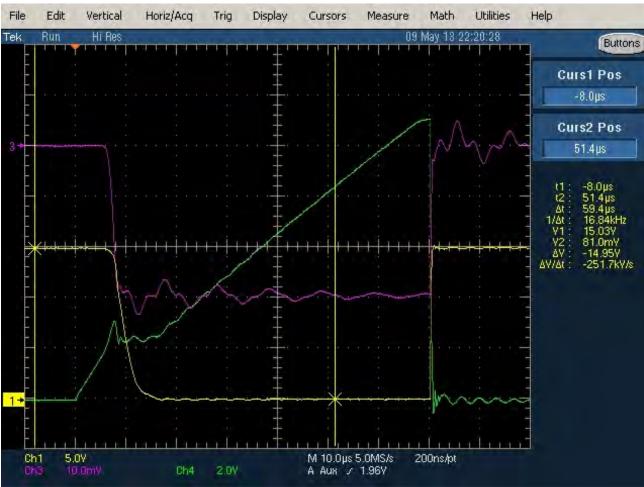

## Oscilloscope Traces of MOSFET switching On / Off

- Green trace V<sub>GS</sub>

- Yellow trace V<sub>DS</sub>

- Purple trace  $I_{D}$  (10mV = 1A)

Gate drive source current << gate drive sink current.

- Turn OFF time << turn ON time (different gate drive currents)</li>

- Note the VGS 'ring' due to high dV/dt

# **Delay, Rise and Fall Times**

- There is always some resistance associated with the gate structure of the MOSFET. Also it is advisable to include a low value external resistance in series with the gate (to damp out any oscillatory transients).

- Initial MOSFET response to gate drive depends on the nature of the load. A resistively loaded MOSFET should be used for these measurements.

- Turn Off depends on Vgs. i.e. it's quicker to turn off from Vgs = 5V than Vgs = 10V due to RG

- There is always some unavoidable 'stray' **inductance** associated with the conductors (lead frame, wire bonds etc.) of a packaged MOSFET. These inductances will affect the switching behaviour while the channel current is changing.

| t <sub>d(on)</sub>  | turn-on delay time            | V <sub>DS</sub> = 30 V; R <sub>L</sub> = 1.2 Ω; V <sub>GS</sub> = 5 V;<br>R <sub>G(ext)</sub> = 5 Ω | - | 95  | - | ns |

|---------------------|-------------------------------|-----------------------------------------------------------------------------------------------------|---|-----|---|----|

| t <sub>r</sub>      | rise time                     |                                                                                                     | - | 118 | - | ns |

| t <sub>d(off)</sub> | turn-off delay time           |                                                                                                     | - | 195 | - | ns |

| t <sub>f</sub>      | fall time                     |                                                                                                     | - | 119 | - | ns |

| L <sub>D</sub>      | internal drain<br>inductance  | from upper edge of drain mounting base to center of die                                             | - | 2.5 | - | nH |

| L <sub>S</sub>      | internal source<br>inductance | from source lead to source bonding<br>pad                                                           | - | 7.5 | - | nH |

## **MOSFET Body Diode Characteristics**

- The 'Body Diode' in the MOSFET structure behaves similarly to all silicon junction diodes. In normal MOSFET operation this diode is reverse biased and **plays no part** in the function.

- When the MOSFET is OFF (V<sub>GS</sub>=0), it will still operate as a diode; D = cathode, S = anode. It will carry current if it is forward biased (V<sub>SD</sub> ≥ 0.5V @ 25°C)

- If the channel is fully enhanced (switched ON) at this stage, current flows through the channel rather than through the diode (if I<sub>D</sub> \* R<sub>DS(on)</sub> < 0.5V). Power loss reduces.</li>

- This 'third quadrant' operation when the MOSFET is turned ON is called 'synchronous rectifier' mode.

- As with all p-n junction diodes, current does not cease immediately when the bias voltage is reversed. There is a short *`reverse recovery'* time while charge carriers are withdrawn from the junction. The charge that is withdrawn from the p-n junction in this process is the *`recovered charge'*.

| • | These non ideal diode characteristics contribute towards power losses. The reverse recovery event can be a troublesome EM |

|---|---------------------------------------------------------------------------------------------------------------------------|

|   | noise source, hence an EMC concern.                                                                                       |

| Source-di       | rain diode            |                                                                                                                                                                                   |   |      |     |    |

|-----------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|-----|----|

| V <sub>SD</sub> | source-drain voltage  | I <sub>S</sub> = 25 A; V <sub>GS</sub> = 0 V; T <sub>j</sub> = 25 °C; <u>Fig. 15</u>                                                                                              | ÷ | 0.8  | 1.2 | V  |

| trr             | reverse recovery time | I <sub>S</sub> = 25 A; dI <sub>S</sub> /dt = -100 A/µs; V <sub>GS</sub> = 0 V;<br>V <sub>DS</sub> = 20 V; T <sub>I</sub> = 25 °C; <u>Fig. 16</u>                                  | - | 32.3 | -   | ns |

| Qr              | recovered charge      |                                                                                                                                                                                   |   | 26.8 | 4   | nC |

| S               | softness factor       |                                                                                                                                                                                   | - | 0.85 | +   |    |

|                 |                       | $I_S = 25 \text{ A}; \text{ d}I_S/\text{d}t = -500 \text{ A}/\mu\text{s}; \text{ V}_{GS} = 0 \text{ V};$<br>$V_{DS} = 20 \text{ V}; \text{ T}_1 = 25 \text{ °C}; \text{ Fig. 16}$ | ~ | 0.7  | -   |    |

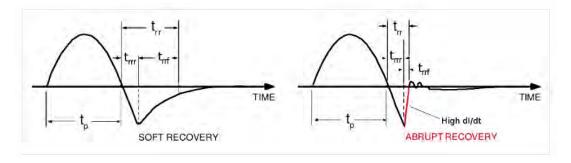

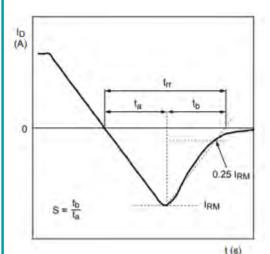

### **Diode Recovery terminology and MOSFETs**

#### Speed => trr and Charge => Qrr

- SiC Rectifiers have minimal Qrr (HV Schottky)

- Schottky has low Qrr

- PN Rectifiers have higher Qrr

#### • trr classes

- Schottky <10nS (including SiC HV devices)</li>

- Standard PN ~1000nS

- Fast ~200nS , Ultrafast 50 to 150nS, Hyperfast <25nS</li>

- Soft Recovery usually 45 to 120nS

#### Softness Factor

- Stated at a dI/dt value (ex. 200A / uS)

- RRSF = Tb / Ta

#### • MOSFET PN Junction -

#### Recovery

- trr and Qrr are listed in Data Sheets. (previous slide)

- RRSF, Softness is not normally listed for MOSFETs for the body diode (PN). For Trench 9 devices this is in the data sheet.

- This can be measured using the same Double Pulse test used for Rectifiers. Example on next slide.

| Source-di       | rain diode            |                                                                                                                                                                                                   |   |      |     |    |

|-----------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|-----|----|

| V <sub>SD</sub> | source-drain voltage  | $I_{S}$ = 25 A; $V_{GS}$ = 0 V; $T_{j}$ = 25 °C; <u>Fig. 15</u>                                                                                                                                   | £ | 0.8  | 1.2 | V  |

| t <sub>rr</sub> | reverse recovery time | I <sub>S</sub> = 25 A; dI <sub>S</sub> /dt = -100 A/µs; V <sub>GS</sub> = 0 V;<br>V <sub>DS</sub> = 20 V; T <sub>j</sub> = 25 °C; <u>Fig. 16</u>                                                  | • | 32.3 | -   | ns |

| Qr              | recovered charge      |                                                                                                                                                                                                   | - | 26.8 | ÷.  | nC |

| S               | softness factor       |                                                                                                                                                                                                   | - | 0.85 | 1   |    |

|                 |                       | $I_{S} = 25 \text{ A}; \text{ dI}_{S}/\text{dt} = -500 \text{ A}/\mu\text{s}; \text{ V}_{GS} = 0 \text{ V};$<br>$V_{DS} = 20 \text{ V}; \text{ T}_{I} = 25 \text{ °C}; \frac{\text{Fig. 16}}{16}$ | 4 | 0.7  | ÷   |    |

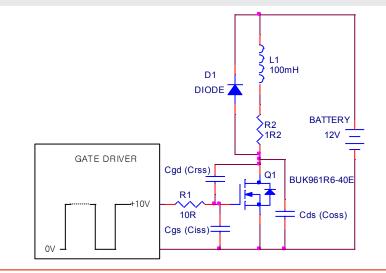

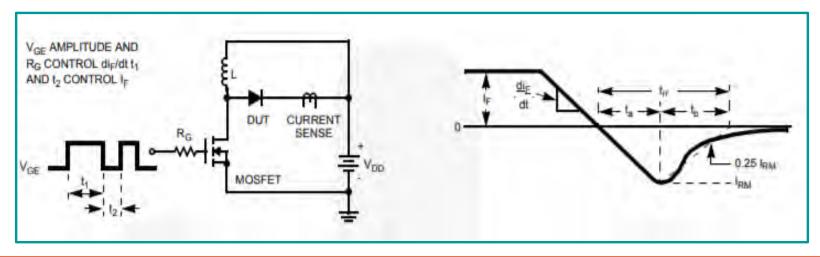

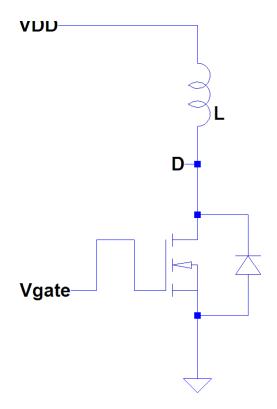

### How trr and Softness are measured

Double Pulse Method

- Test Circuit for MOSFET Body Diode as DUT is the same test method as used for Rectifiers. Test method is similar to  $\frac{1}{2}$  Bridge applications.

- DUT is MOSFET with Gate shorted to source.

- First Pulse establishes the current If in t1

- Off Pulse t2, establishes current in Diode as If

- Second Pulse used to measure the waveform.

# **Extended Topics**

May 23, 2019

### **Power Dissipation Thermal Design**

#### Power Handling

Average Power Total Loss Model Loss Calculation Methods Conduction Switching Avalanche Static Device Temperature Dynamic Die Temp

### **Total Power Loss Model**

#### Why:

1) A large percentage of customer design questions are thermal.

2) Aside from ESD, MOSFET operational failure is primarily from thermal overstress.

#### **Primary Components**

**P**total = **P**conduction + **P**switching + **P**avalanche

- Pconduction ~ f ( I, Rds@Vgs, DutyCycle) in ON State

- Fairly easy to estimate at max constant current (Idc<sup>2</sup> \* Rds)

- Also, Reverse conduction in OFF state across body diode (Ir \* Vd)

- **P**switching ~ f ( deltaI, deltaV, Fswitching, Zload)

- Also could include Gate Drive losses if Fswitching is high. With large power MOSFETs, most the gate drive losses are in the driver circuitry (i.e. low Rgate)

**P**gatesw ~ f ( Qgtot @Vgs, Fswitching, Rgate)

- Pavalanche f ( Vbat, Iavl, Vavl, Favl, Zavl)

- BVdss exceeded from switching off Inductive load. Eas is specified as one time event.

## **Example Application**

Inductive Load – 14V Fuel Injector

### Customer Application Parameters Example:

#### Conduction

**R**load = 22 Ohms **V**dd = 16V **DTY** = 12% (max at Fmax)

#### Switching

Trise = 50uS Tfall = 50uS Fmax = 60Hz (7200 rpm, 4 cycle) deltaI = 16V/220hms deltaV = Vdd - Gnd = 16V

#### Avalanche

Lload = 12mH \*Cload = 0.3uF Rmb-ambient = 10 K/W

### **Conduction Losses - Estimating**

**P**conduction ~ f (Id, Rds@Vgs, Rload, Vbat, DutyCycle) in ON State

- Fairly easy to estimate at max constant current (Id<sup>2</sup> \* Rds \* DutyCycle )

- Steps:

- 1. Use max Id (Rload and Vbat)

- 2. Use ON Duty Cycle

- 3. Use max Steady State Tj design target in Application (1<sup>st</sup> pass) to estimate max **R**dson. Example: 25mOhm \* 1.5 (at 120C) = <u>33mOhm</u>

| Symbol            | Parameter                        | Conditions                                                           | Min | Тур | Max | Unit |

|-------------------|----------------------------------|----------------------------------------------------------------------|-----|-----|-----|------|

| Static chara      | acteristics                      |                                                                      |     |     |     |      |

| R <sub>DSon</sub> | drain-source on-state resistance | V <sub>GS</sub> = 10 V; I <sub>D</sub> = 8 A; T <sub>j</sub> = 25 °C | -   | 18  | 25  | mΩ   |

**Pr**conduction ~ f (Ir, Vd, Tr, Fswitching) in OFF State

- Reverse conduction in OFF state across body diode during periodic switching.

- Specifications and Spice models of Body Diodes are simplistic.

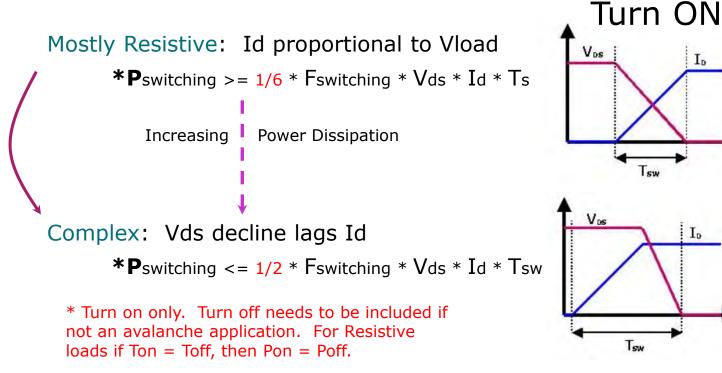

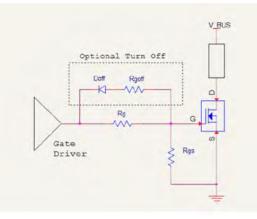

## **Switching Losses - Estimating**

#### Methods used to Estimate Switching Losses

**P**switching  $\sim f$  (deltaI, deltaV, Fswitching, Tsw, Zload)

\* Figures from Peter Markowski, ePOWER LLC (2012) and John Hargenrader, Fairchild Semiconductor (2013)

Validation

#### **Spice Simulation**

Electrical Model of Load

Loads are not ideal. inductance changes with current, or Solenoid

Spice Model with Accurate Switching

Gate Drive Model is critical.

Compare Simulation to circuit performance.

Gate Drive Losses can be evaluated in model. Usually, small enough to neglect.

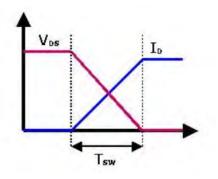

## **Resistive Load Example**

For the linear waveforms shown, where T is the total switching time:

Vds = Vp (1-t/T) Ids = Ip (t/T)

So, the instantaneous power is

**P**swon = **V**p \* **I**p \* t/T \* (1-t/T)

Integrating the Energy over T (switching time) gives the ON switching Energy as:

**E**swon =  $\int_0^T \mathbf{P} dt$

- $= \int_0^T \mathbf{V} p^* \mathbf{I} p^* t/T^* (1-t/T) dt$

- =  $\mathbf{V}p^* \mathbf{I}p^* [\int_0^T t/T dt \int_0^T (t/T)^2 dt]$

- =  $\mathbf{V}p^* \mathbf{I}p^* [ [ 1/2T * t^2 ] [1/3T^2 * t^3 ] ]_0^{T_{sw}}$

- = **V**p\* **I**p \* [ 1/2Tsw 1/3Tsw]

#### Resistive Load waveforms

### **Avalanche Losses**

**E**<sub>as</sub> specifications in data sheets is for a one time event at specific I and L value. Can be used for device comparison, but limited value for design.

- 1. Avalanche (Eas) calculations can be used for Pavalanche, to be used in Static Thermal analysis.

- 2. Avalanche data sheet curves can be used for singular and repetitive event robustness. (Discussed later)

Eas - Avalanche energy can be higher than the energy stored in the inductor. (What??)

VavI - Is higher than BVdss. A Swag factor is included in these calculations, normally 1.2 to 1.3. This can be verified in the application with the exact device.

$\mathbf{R}_{L}$  - When the series R of the Inductor is small, these losses can be ignored.  $\mathbf{T}_{av}$  -Time in Avalance depends on rate of energy dissipated across MOSFET.

(\* Figure from AN-7514 Fairchild 2002)

### Static Thermal Model – Final Output - Tmb

- 1. Use the **P**total Power Dissipation to estimate the Device Mounting Base Max Operating Temperature, **T**mb(max)

- 3D thermal model (i.e. *FloTherm*)

- Physical Calculations of **R**mb-ambient (old school, sometimes including blackbody radiation portion)

- Use of standard **R**mb-ambient ratings for device on specified pad area (\*No longer specified on many device data sheets), or from Test Card in the literature.

- Lab Measurement with known power dissipation, and thermocouples on prototype hardware.

- 2. Use **T**mb(max) as input to Dynamic Spice Model with RC Thermal network.

#### Output: Tjmax, deltaTj, Tjavg

3. Use the data sheet **R**j-mb to Calculate the Max average die temp, **T**javg. This can be used for FIT Rate Calculations, and to cross check the simulations. **\*\***

```

Thermal characteristics

9.

Table 6.

Thermal characteristics

Symbol

Conditions

Min

Max

Unit

Parameter

Typ.

thermal resistance

Fig. 5

0.9

K/W

R<sub>th(j-mb)</sub>

from junction to

mounting base

```

**T**javg = (**P**conduction + **P**switching + **P**avalanche) \* (**R**j-mb + **R**mb-Ambient)

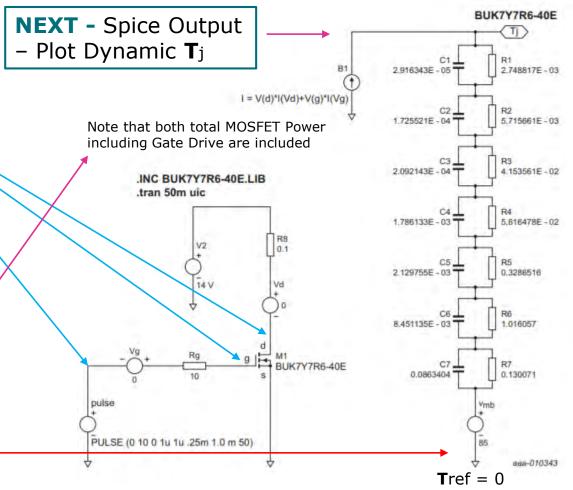

## **Dynamic Die Temp – RC Thermal Model**

Methodology

1. Construct Electrical Spice Model

Compare Model to switching waveforms of actual circuit Verify Maximum Conditions, Duty Cycle, Min Ioad R, Max Ioad L, etc.

- 2. Integrate RC Thermal Model (Foster or Cauer) in Spice.

- May be integrated into Spice Model already

- If not, set up Power Input to RC / Network.

- Establish Tmb reference Voltage. Use Tmb(max) as input to Dynamic Spice Model. (here Tmb is set to 85)

\*figures from Power MOSFET Application Handbook, Nexperia Semiconductor

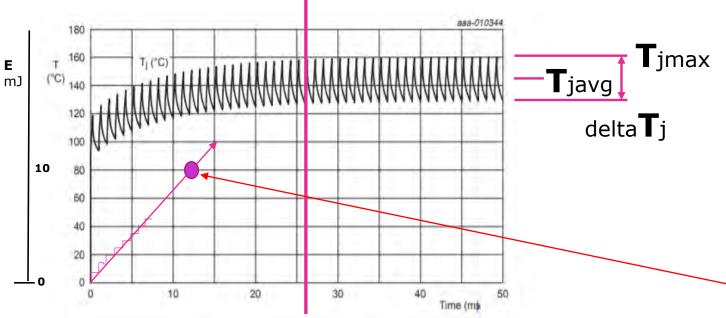

## **Dynamic Die Temp – RC Thermal Model**

Spice Output – Dynamic Die Temp

Thermal Model Reaches Steady State

Questions Using Spice:

- 1) Is Rds thermally adjusted for Temp? In models that have embedded Cauer RC models, if they are connected to a reference temp, the Rds may be compensated.

- ) Is Rds set to the max, or to nominal in the model at 25C as a starting point.

Basic Thermal Design elements: 1) Is **T**jmax below 175C? 2) Is delta**T**j extreme?

\*\* Crosscheck **T**javg with calculated value from slide 19

Conduction, Switching and Avalanche loss estimates, can all be compared to the Spice Model calculations.

Switching - Using the integrated Energy functions in Spice and looking at the loss over multiple cycles is useful.

Example = (10mJ / 12mS) ~= 0.83W

# May 23, 2019 Understanding Snubbers

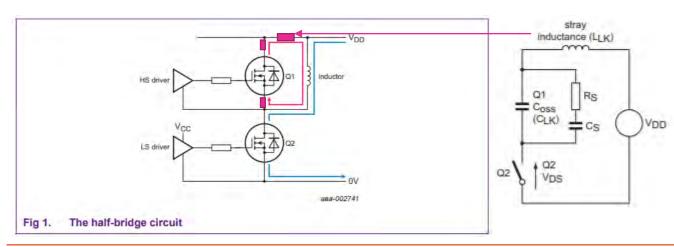

### **Snubbers -** 1/2 Bridge Example AN11160

#### What does a snubber do?

- Manages sudden changes in current during switching.

- In AN11160, the stray inductance in series with the MOSFET is what is being 'snubbed', from PCB traces and package inductance.

#### **Basics of Selecting RC components.**

- $\ensuremath{R_{\text{S}}}$  is selected to maintain instantaneous current during switching event.

- **C**s is selected to allow transfer of stored energy from Inductor to damp ringing from **C**oss, **L**LK interaction.

#### Rs (Snubber Resistor)

- Rule of Thumb use the load current, and Vdd. Rs = Vdd / Iload

- Experimental Use Cadd in parallel with Coss, and measure frequency of fring at two different points in the Lab (Section 3). Calculate Lik (Section 5).

$$R_S = \left(\frac{1}{2\zeta}\right) \sqrt{\frac{L_{LK}}{C_{LK}}}$$

- Cs (Snubber Cap)

- 1. Rule of Thumb

- Use **C**<sub>s</sub> = ~**C**<sub>oss</sub> of the MOSFET

- 2. Experimental Use **R**s and **f**ring to calculate. (Section 5)

# SOA Derating

May 23, 2019

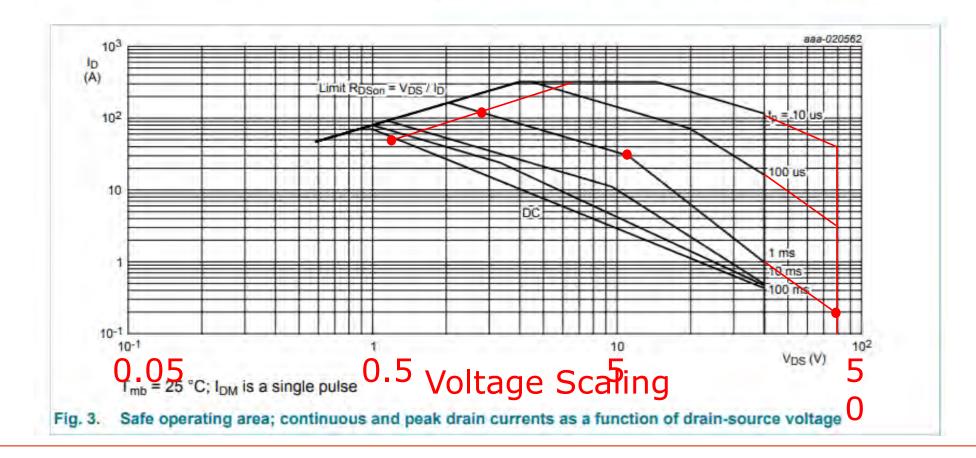

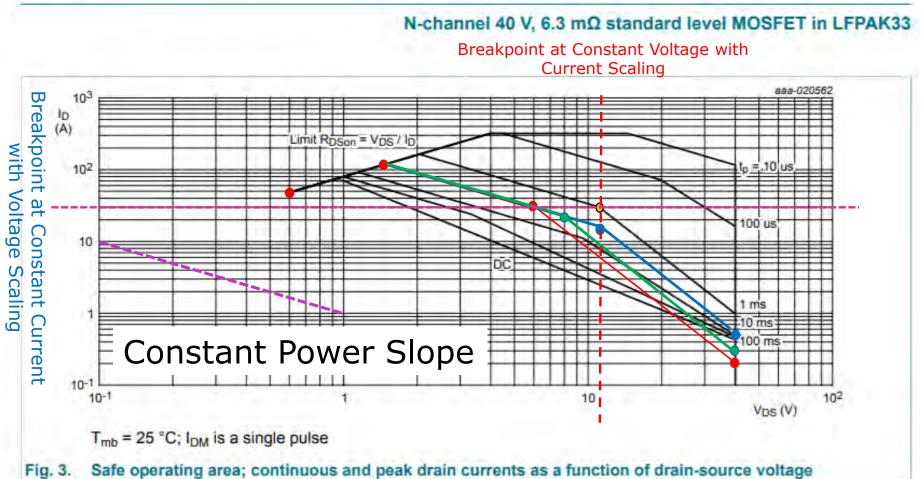

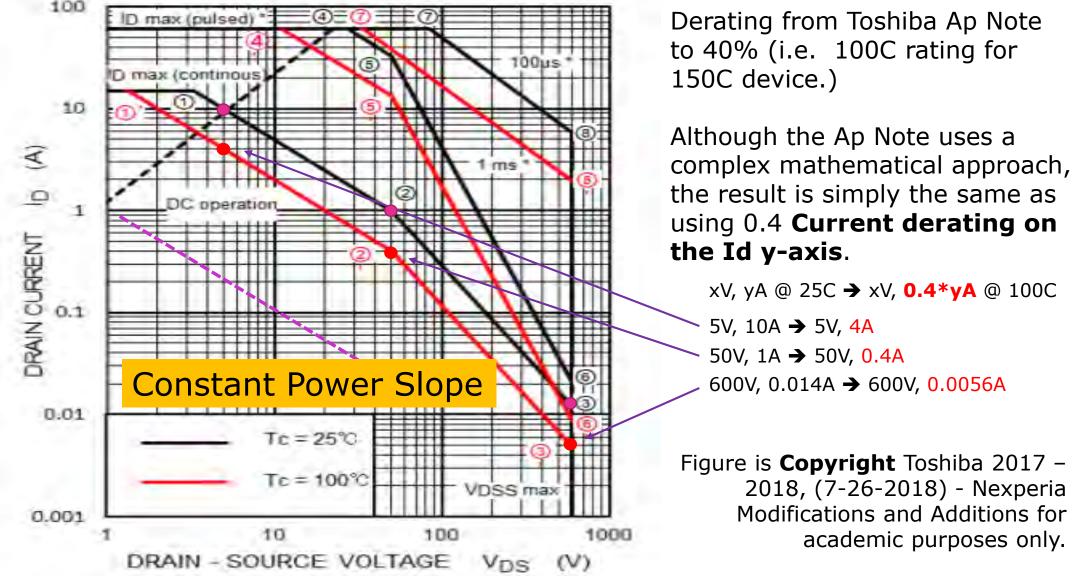

### **Voltage Scale or Current Scale SOA Method**

Calculate the proportion based on

Tjmax and Tmb

Power Scale Factor = [Tjmax – Tmb(application)] [Tjmax – Tmb(SOA Curve)]

For a 175C device at 100C this is: PSF = [175 - 100] / [175 - 25] = 0.5

- 1) Scale either the Voltage Axis or Current Axis using this factor.

- 2) Reposition the BVdss vertical line or Imax line to the new axis scale

- 3) Reposition the Rds Limit line based on the new x-axis scale

- Move horizontally for Voltage axis

- Move Vertically for Current axis

- 4) Extend the data lines to the endpoints with the same slope

#### **De-rated to 50% power using Voltage Scaling on the x-axis,** This is a 50% derating for 100C (using 175 C max)

Nexperia

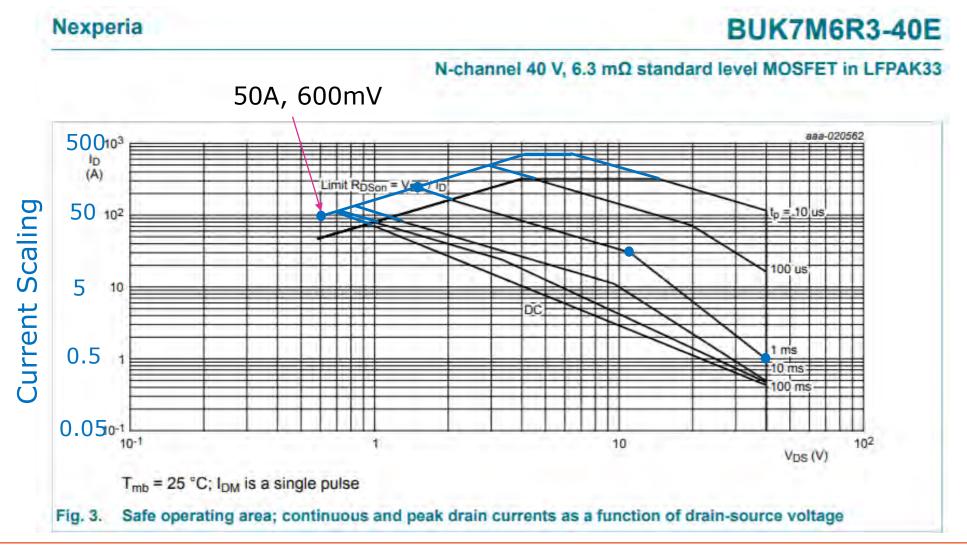

#### BUK7M6R3-40E

N-channel 40 V, 6.3 mΩ standard level MOSFET in LFPAK33

#### **Derated to 50% power using Current Scaling on the Y-Axix** This is a 50% derating for 100C (using 175 C max)

### **\*New - Combined V & I - SOA De-rating Method**

• Calculate the proportion based on Tjmax and Tmb Power Scale Factor = [Tjmax - Tmb(application)] / [Tjmax - Tmb(SOA Curve)]

For a 175C device at 100C this is: PSF = [175 - 100] / [175 - 25] = 0.5

Take the Square Root of the PSF.

√ PSF = **0.707**

- 1) Rescale the x and y axis using the square root of the scale factor.

- 2) Reposition the Imax and BVdss lines based on the new scale

- 3) Extend the Rds limit line based on the new scale to intersect Imax

- 4) Extend the data lines using the existing slopes

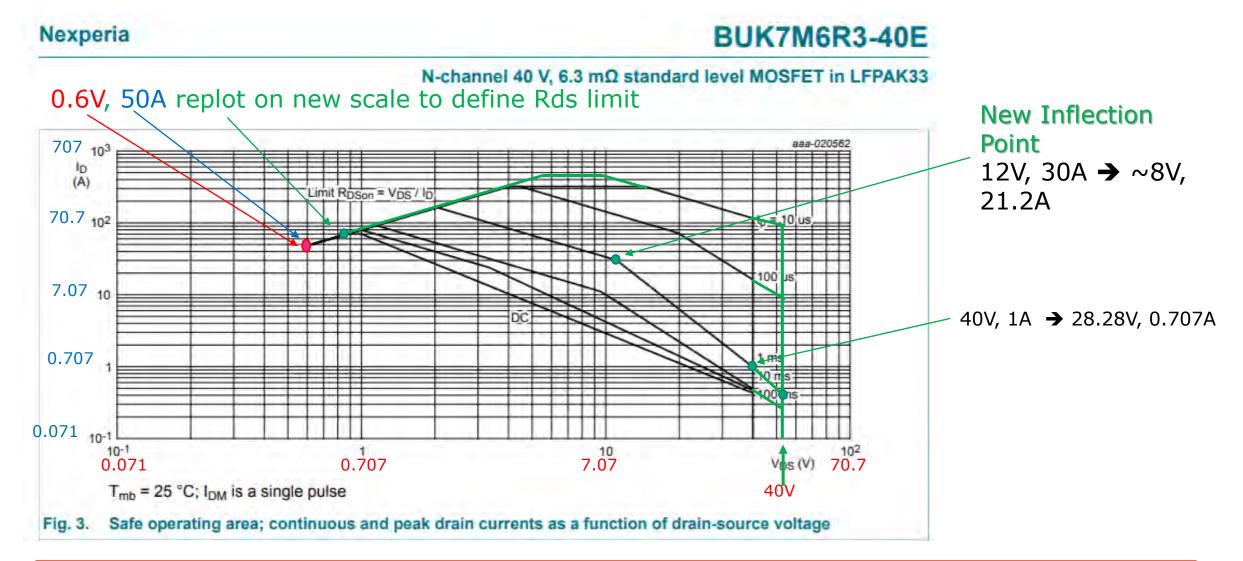

#### **Derated to 50% power using combined Voltage and Current Scaling** This is a 50% derating for 100C (using 175 C max)

#### Derated to 50% power comparison at <u>1mS</u> – derating for 100C (using 175 C max) Voltage vs. Current vs. V\*I

Nexperia

#### BUK7M6R3-40E

Note that there is no difference in any method left of the Spirito effect region where the line follows the constant power formula.

The difference lies in where the Spirito effect break point starts.

(named after Professor Paolo Spirito)

### **Comparison to Toshiba method which uses more complex derivations**

### EFFICIENCY WINS.