## **Product Change Notification / SYST-20SYRM787**

Date:

23-Mar-2023

## **Product Category:**

**Inductive Position Sensors**

## **PCN Type:**

Document Change

## **Notification Subject:**

Data Sheet - LX34211 - Inductive Position Sensor with Embedded MCU

## **Affected CPNs:**

SYST-20SYRM787\_Affected\_CPN\_03232023.pdf SYST-20SYRM787\_Affected\_CPN\_03232023.csv

## **Notification Text:**

SYST-20SYRM787

Microchip has released a new Datasheet for the LX34211 - Inductive Position Sensor with Embedded MCU of devices. If you are using one of these devices please read the document located at LX34211 - Inductive Position Sensor with Embedded MCU.

**Notification Status: Final**

#### **Description of Change:**

The following is the list of modifications:

• Updated Electrical Characteristics

Impacts to Data Sheet: See above details.

Reason for Change: To Improve Productivity

Change Implementation Status: Complete

Date Document Changes Effective: 23 Mar 2023

NOTE: Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices:: N/A

| Attachments:                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LX34211 - Inductive Position Sensor with Embedded MCU                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                             |

| Please contact your local Microchip sales office with questions or concerns regarding this notification.                                                                                                                                                                                    |

| Terms and Conditions:                                                                                                                                                                                                                                                                       |

| If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section. |

| If you wish to <u>change your PCN profile</u> , <u>including opt out</u> , please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.                              |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

Affected Catalog Part Numbers (CPN)

LX34211QPW-TR LX34211QPW-TR-V01 LX34211QPW-TR-VAO

Date: Wednesday, March 22, 2023

## **Inductive Position Sensor with Embedded MCU**

#### **Features**

- · 12-Bit Positional Output Resolution

- One 0 5V DAC Output of Position

- · One PWM Output of Position

- · Adjustable Position Sensor Gain

- · High Automatic Gain Control for Larger Airgaps

- · 6-Segment Calibration

- Dynamic Calibration for Extended Accuracy over Airgap

- · Immune to Stray Magnetic Fields

- · Low Temperature Drift

- · Reverse Power Protection

- · 32-bit CORTUS APS3 RISC MCU

- -40°C to +125°C Operation

- · AEC-Q100 Certification

- · ISO26262 ASIL B Developed and Supported

#### **Applications**

- Automotive Actuators

- · Industrial Position

- Medical Control

#### **Description**

The LX34211 is a highly accurate inductive position sensor interface IC with features that simplify the sensor design for a wide range of applications. This IC has more automatic control gain and a dynamic calibration algorithm that makes it easier to design accurate sensors with larger air gap and more mechanical tolerances with less current.

The device includes an integrated oscillator circuit for driving the primary coil of an inductive sensor, along with two independent analog conversion paths for conditioning, converting, and processing of sine and cosine analog signals from the secondary coils of the sensor. The output signal is an DAC analog or PWM signal that represents the position with 12-bit measurement range resolution.

Each analog signal path includes adjustable AGC gain and digital calibration capability to match the mechanical system variation and maximize accuracy.

The automatic gain control unit has improved gain for an even wider range of target-to-sensor airgap applications. In addition, a unique dynamic calibration algorithm corrects for errors before the on board linearization stage, maintaining accuracy over a wider range of airgaps.

The calibration information can be written to the internal nonvolatile EEPROM memory during end-of-line production resulting in improved production yields by compensating for a wider range of mechanical tolerances.

The LX34211 is available in a 14-lead TSSOP package. The device is specified over a temperature range of -40°C to +125°C making it suitable for commercial, industrial, medical, and/or automotive sensor applications.

The IC was developed using the ISO26262 standard to reach ASIL B levels as an SEooC. Redundant sensor system with two ICs can be used for ASIL-C and ASIL-D applications.

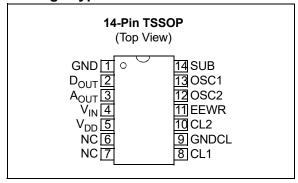

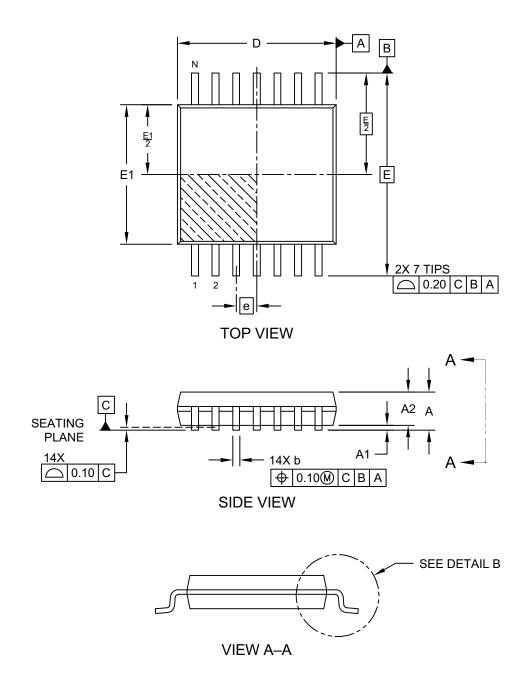

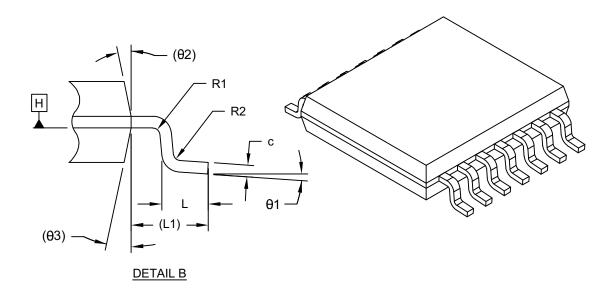

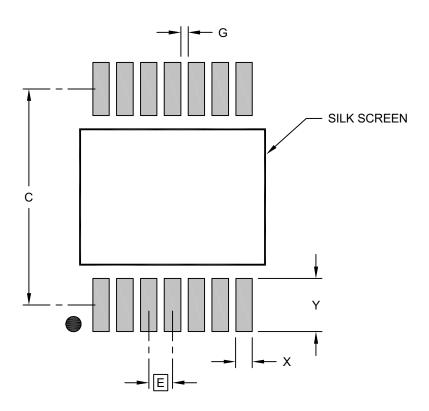

## **Package Types**

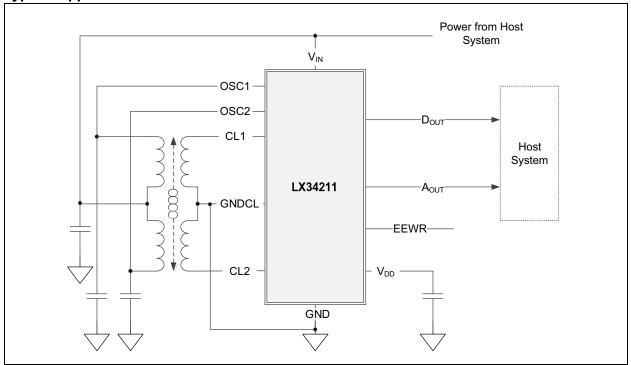

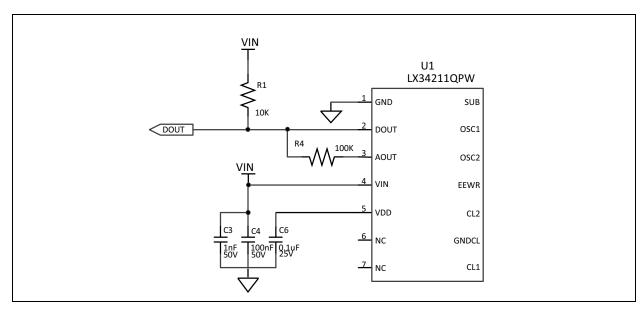

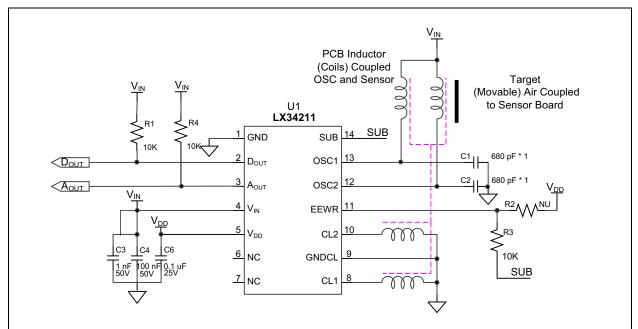

## **Typical Application**

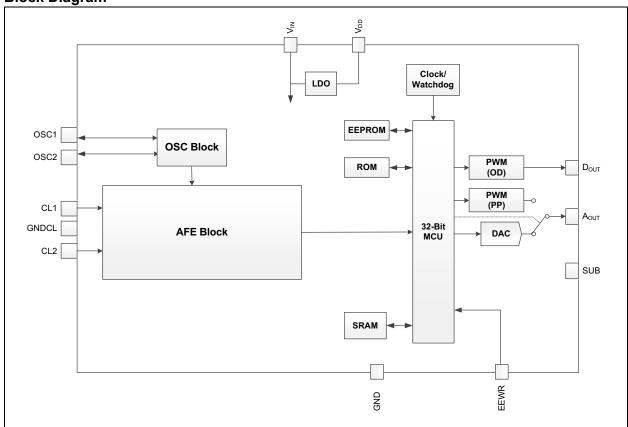

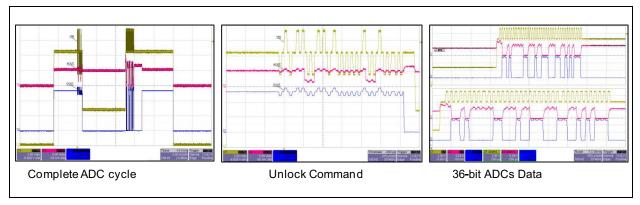

## **Block Diagram**

### 1.0 ELECTRICAL CHARACTERISTICS

## 1.1 Electrical Specifications

## **Absolute Maximum Ratings †**

| Supply Input Voltage Pin (V <sub>IN</sub> )                      | -7V to 20V     |

|------------------------------------------------------------------|----------------|

| Load Current on V <sub>DD</sub> Pin                              | 1 mA to 15 mA  |

| Voltage on OSC1 and OSC2 Pins                                    | 0.3V to 16V    |

| Voltage on CL1, CL2, EEWR Pins                                   | 0.5V to 3.6V   |

| Voltage on A <sub>OUT</sub> , D <sub>OUT</sub> Pins              | 0.5V to 16V    |

| Operating Humidity (non-condensing)                              | 0% to 95%      |

| Operating Temperature                                            | 40°C to +125°C |

| Storage Temperature                                              | 40°C to +150°C |

| Lead Temperature (soldering, 10 seconds)                         | +300°C         |

| Package Peak Temperature for Solder Reflow (40 seconds exposure) | +260°C         |

| ESD Rating – All Pins except Pin 11 – HBM (AEC-Q100-002D)        | ±2 kV          |

| ESD Rating – Pin 11 – HBM (AEC-Q100-002D)                        | +2 kV/-1 kV    |

| ESD Rating – All Pins – CDM (AEC-Q100-011)                       | ±1.5 kV        |

† Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability. All voltages are with respect to GND. All voltages on ESD are with respect to SUB.

## **Recommended Operating Range**

| Parameters                             | Symbol             | Min. | Тур. | Max. | Units | Conditions                                              |

|----------------------------------------|--------------------|------|------|------|-------|---------------------------------------------------------|

| Supply Voltage                         | V <sub>IN</sub>    | 4.4  | 5.0  | 5.6  | V     | For normal operation                                    |

| V <sub>IN</sub> EEPROM Program<br>High | VIN_PH             | _    | _    | 17   | V     |                                                         |

| Supply Current                         | I <sub>IN</sub>    | _    | _    | 9.3  | mA    | For normal operation, excluding oscillator tail current |

| Total Tank Driving<br>Current Range    | ITK                | 0    | _    | 10   | mA    | $V_{TAP} = 5V$                                          |

| Output Current                         | I <sub>AOUT0</sub> | -15  | _    | -8   | mA    | A <sub>OUT</sub> = 0V                                   |

|                                        | I <sub>AOUT5</sub> | 6    | _    | 15   | mA    | A <sub>OUT</sub> = 5V                                   |

|                                        | I <sub>DOUT0</sub> |      | _    | 35   | mA    | D <sub>OUT</sub> = 0V                                   |

| Internal Clock Frequency               | F <sub>OSC</sub>   | 6.4  | 6.55 | 6.72 | MHz   | T <sub>A</sub> = Room temperature                       |

| Operating Temperature                  | $T_OP$             | -40  | _    | +125 | °C    |                                                         |

### **Electrical Characteristics**

| Parameters                               | Symbol               | Min. | Тур.  | Max.               | Units    | Conditions                                                                                                             |

|------------------------------------------|----------------------|------|-------|--------------------|----------|------------------------------------------------------------------------------------------------------------------------|

| Power                                    | <u> </u>             |      |       |                    |          |                                                                                                                        |

| V <sub>IN</sub> Input Voltage            | V <sub>IN</sub>      | 4.4  | 5.0   | 5.6                | V        | For normal operation                                                                                                   |

| V <sub>IN</sub> Supply Current           | I <sub>IN</sub>      | _    | 8     | 9.3                | mA       | For normal operation, excluding oscillator tail current, I <sub>DD</sub> = 0 mA, I <sub>I/O</sub> = 0 mA, f = 6.55 MHz |

| V <sub>IN</sub> UV High Threshold        | VIN_UV_HI            | 3.8  | _     | 4.3                | V        |                                                                                                                        |

| V <sub>IN</sub> UV Low Threshold         | VIN_UV_LO            | 3.6  | 3.75  | 4.1                | V        | A <sub>OUT</sub> goes low                                                                                              |

| V <sub>IN</sub> OV High Threshold        | VIN_OV_HI            | 6.1  | 6.384 | 6.7                | V        |                                                                                                                        |

| V <sub>IN</sub> OV Low Threshold         | VIN_OV_LO            | 6.0  | 6.311 | 6.6                | V        |                                                                                                                        |

| V <sub>DD</sub> Reference Voltage        | _                    |      |       | _                  |          |                                                                                                                        |

| Output Voltage                           | $V_{DD}$             | 3.45 | 3.5   | 3.55               | V        | I <sub>DD</sub> = 10 mA, trimmed                                                                                       |

| Output Current                           | I <sub>DD</sub>      | _    |       | 10                 | mA       | Additional current sourced to external load(s)                                                                         |

| V <sub>DD</sub> UVLO                     | VDD_UVLO             | 2.9  | _     | 3.4                | V        | Rising edge                                                                                                            |

| V <sub>DD</sub> UVLO Hysteresis          | VDD_UVHYST           |      | 0.2   |                    | V        |                                                                                                                        |

| V <sub>DD</sub> Oscillation<br>Threshold | VDD_RIPPLE           |      | 0.17  |                    | Vpk      | 1MHz < Freq(V <sub>DD_RIPPLE</sub> ) < 10 MHz                                                                          |

| V <sub>DD</sub> short Current            | IDD_SHT_N40          |      | 120   |                    | mA       | $V_{DD}$ is shorted to GND, $V_{IN}$ =5.5V, $T_A$ =-40°C                                                               |

| V <sub>DD</sub> Short Current            | IDD_SHT_25           |      | 100   |                    | mA       | $V_{DD}$ is shorted to GND, $V_{IN}$ =5.5V, $T_A$ =25°C                                                                |

| V <sub>DD</sub> Short Current            | IDD_SHT_125          |      | 80    |                    | mA       | $V_{DD}$ is shorted to GND, $V_{IN}$ =5.5V, $T_A$ =125°C                                                               |

| Oscillator                               |                      |      |       |                    |          |                                                                                                                        |

| Middle Tap Voltage                       | $V_{TAP}$            |      | 5     | _                  | V        | V <sub>IN</sub> = 5V                                                                                                   |

| Midtap Open Threshold                    | VTAP_OPEN            | 3.0  | 3.3   | 3.6                | V        | V <sub>TAP</sub> = 5V                                                                                                  |

| Total Tank Driving<br>Current Range      | ITK                  | 0    | _     | ITK <sub>MAX</sub> | mA       | $V_{TAP} = 5V$                                                                                                         |

| Max Total Tank Driving<br>Current        | ITK <sub>MAX</sub>   | 9.1  | 12.8  | _                  | mA       | V <sub>TAP</sub> = 5V                                                                                                  |

| Swing Voltage of OSC1 and OSC2           | V <sub>osc</sub>     | 2.2  | _     | 10                 | $V_{pp}$ | V <sub>TAP</sub> = 5V                                                                                                  |

| OSC1 Over Voltage threshold              | V <sub>OSC_OV</sub>  |      | 10.8  |                    | $V_{pp}$ | $V_{TAP} = 5V$                                                                                                         |

| OSC1 Under Voltage threshold             | V <sub>osc_uv</sub>  |      | 2.0   |                    | $V_{pp}$ | $V_{TAP} = 5V$                                                                                                         |

| Typical Swing Voltage of OSC1            | V <sub>OSC1TYP</sub> | _    | 6     | _                  | $V_{pp}$ | V <sub>TAP</sub> = 5V, Target at typical air gap distance. Set by external capacitor.                                  |

| Reference Frequency<br>Range             | F <sub>OSC</sub>     | 1    | _     | 5                  | MHz      | $V_{TAP} = 5V$                                                                                                         |

| Frequency Variation                      | F <sub>OSCTOL</sub>  | -5   | _     | 5                  | %        | V <sub>TAP</sub> = 5V                                                                                                  |

| Reference Inductance                     | L <sub>OSC</sub>     | _    | 6     | _                  | μH       | V <sub>TAP</sub> = 5V, Inductor connected to OSC1, 2 pins                                                              |

| Tank Circuit Quality Factor              | Q <sub>OSC</sub>     | 15   | 25    | _                  | _        | V <sub>TAP</sub> = 5V                                                                                                  |

| Harmonics                                | H <sub>OSC</sub>     |      |       | 2                  | %        | $V_{TAP}$ = 5V, $V_{OSC1}$ =8.5 $V_{pp}$ , GBNT                                                                        |

## **Electrical Characteristics (Continued)**

| Parameters                                       | Symbol           | Min.     | Тур.  | Max.  | Units | Conditions                                                            |

|--------------------------------------------------|------------------|----------|-------|-------|-------|-----------------------------------------------------------------------|

| Resistance between OSC1 and V <sub>IN</sub>      | ROSC1_VIN        | 1        | _     | _     | MΩ    | V <sub>IN</sub> = 5V, OSC1 = GND, Measure<br>Current from OSC1 to GND |

| Resistance between OSC2 and V <sub>IN</sub>      | ROSC2_VIN        | 1        | _     | _     | MΩ    | V <sub>IN</sub> = 5V, OSC2 = GND, Measure<br>Current from OSC2 to GND |

| Resistance between OSC1 and GND                  | ROSC1_GND        | 1        | _     | _     | ΜΩ    | V <sub>IN</sub> = 0V, OSC1 = 5V, Measure<br>Current from OSC1 to 5V   |

| Resistance between OSC2 and GND                  | ROSC2_GND        | 1        | _     | _     | MΩ    | V <sub>IN</sub> = 0V, OSC2 = 5V, Measure<br>Current from OSC2 to 5V   |

| Resistance between OSC1 and OSC2                 | ROSC1&2_HI       | 500      | _     | _     | kΩ    | OSC1 = 1V <sub>pp</sub> , OSC2 = GND                                  |

| CL1 and CL2                                      |                  |          |       |       |       |                                                                       |

| CL1& CL2 Signal<br>Regulated Amplitude<br>@FBK=0 | CLPPFBK0         | 30       | 50    | 65    | mVpp  | FBK=0                                                                 |

| CL1& CL2 Signal regulated Amplitude @ FBK=1      | CLPPFBK1         | 80       | 100   | 120   | mVpp  | FBK=1                                                                 |

| CL1, CL2, GNDCL input open threshold             | CL_OPN           |          | 1     |       | V     |                                                                       |

| Analog-Front End                                 |                  | •        |       |       |       |                                                                       |

| EMI Filter Cut-off Freq                          | EF01             |          | 13.5  |       | MHz   | GBNT                                                                  |

| Demodulator Gain                                 | DAA01            |          | 14    |       | V/V   | FBK=0                                                                 |

| Demodulator Gain                                 | DAA02            |          | 7     |       | V/V   | FBK=1                                                                 |

| PGA Gain Range                                   | GRPGA            | 2.375    | 3.125 | 3.688 | V/V   | GBNT GADJ=000 to 111                                                  |

| PGA Gain Step                                    | GPGAS            |          | 6     |       | %     |                                                                       |

| 13 Bits Sigma-Delta ADC                          | s(ADC1/2) and 10 | bits SAR | ADC(A | DC3)  |       |                                                                       |

| ADC Resolution                                   | RADC12           | _        | 13    | _     | bits  | ADC1 & ADC2                                                           |

| Full-Scale Range                                 | FSR12            |          | VDD   |       | V     | ADC1 & ADC2                                                           |

| Integral Nonlinearity                            | INL12            | -1       | _     | 1     | LSB   | GBNT, ADC1 & ADC2                                                     |

| ADC Sampling Clock                               | FADC12           | 0.1025   |       | 0.82  | MHz   | FCLK/8 ~ FCLK/64, ADC1&ADC2                                           |

| ADC3 Resolution                                  | RADC3            |          | 10    |       | bits  |                                                                       |

| ADC3 Resolution                                  | RADC3EX          |          | 12    |       | mV    | OSC1 Peak voltage per LSB                                             |

| ADC3 Sampling Clock                              | FADC3            |          | 0.82  |       | MHz   | FCLK/8                                                                |

| ADC3 Integral<br>Nonlinearity                    | INL3             | -2       |       | 2     | LSB   |                                                                       |

| CL1, CL2 Too High<br>Threshold                   | CLIPPING         |          | 4040  |       |       |                                                                       |

| CL1, CL2 Too Low<br>Threshold                    | LOW              |          | 1000  |       |       | (4096-ADC1) <sup>2</sup> +(4096-ADC2) <sup>2</sup> =LOW <sup>2</sup>  |

## **Electrical Characteristics (Continued)**

| Parameters                       | Symbol   | Min.    | Тур. | Max. | Units  | Conditions                                                                                                                                                                         |

|----------------------------------|----------|---------|------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SINC, SINC + FIR Filter 1        |          | 141111. | יאף. | max. | Cilits | Conditions                                                                                                                                                                         |

|                                  |          | T       | 1.6  |      | Id I=  | DEEDECH = 00                                                                                                                                                                       |

| Data Update Rate                 | DUR00    | _       | 1.6  | _    | kHz    | REFRESH = 00,<br>(SINC, SINC + FIR)                                                                                                                                                |

|                                  | DUR01    |         | 0.8  | _    | kHz    | REFRESH = 01,<br>(SINC, SINC + FIR)                                                                                                                                                |

|                                  | DUR02    |         | 400  | _    | Hz     | REFRESH = 10,<br>(SINC, SINC + FIR)                                                                                                                                                |

|                                  | DUR03    | _       | 200  | _    | Hz     | REFRESH = 11,<br>(SINC, SINC + FIR)                                                                                                                                                |

| Digital Filter Delay of SINC     | DLSINC   |         | 256  |      | Cycle  | FADC12 Clock Cycle                                                                                                                                                                 |

| Digital Filter Delay of SINC+FIR | DLSFIR   |         | 512  |      | Cycle  | FADC12 Clock Cycle                                                                                                                                                                 |

| Filter SNR                       | FLTRSNR  | _       | -86  | -73  | dB     | GBNT                                                                                                                                                                               |

| Crosstalk Rejection              | CTR      | _       | -44  | _    | dB     | GBNT                                                                                                                                                                               |

| Power Supply Rejection<br>Ratio  | PSRR     |         | -86  | _    | dB     | GNBT                                                                                                                                                                               |

| Internal Clock                   |          | L       |      |      |        |                                                                                                                                                                                    |

| Clock Frequency                  | FCLK     | 6.4     | 6.55 | 6.72 | MHz    | After trimming, T <sub>A</sub> =+25°C                                                                                                                                              |

| Clock Frequency<br>Tolerance     | FCLK_TOL | -6      | _    | 6    | %      | T <sub>A</sub> =-40°C to 125°C                                                                                                                                                     |

| Processing Resources             |          |         |      |      | 1      |                                                                                                                                                                                    |

| MCU Data Bus                     | MCU01    | _       | 32   | _    | bits   |                                                                                                                                                                                    |

| MCU Instruction Size             | MCU02    | 16      | _    | 32   | bits   |                                                                                                                                                                                    |

| ROM Size                         | MCU03    | _       | 12   | _    | Kbytes | 32-bit words                                                                                                                                                                       |

| SRAM Size                        | MCU04    | _       | 128  | _    | bytes  | Application data, 32-bit words                                                                                                                                                     |

| EEPROM Write<br>Endurance        | MCU05    | 100     | _    | _    | cycles |                                                                                                                                                                                    |

| EEPROM Size                      | MCU06    | _       | 16   | _    | words  | 16-bit words                                                                                                                                                                       |

| Watchdog Timer                   |          |         |      |      |        |                                                                                                                                                                                    |

| Power-Up Watchdog<br>Timer       | TPUWT    | _       | 20.4 | _    | ms     |                                                                                                                                                                                    |

| Start-Up Time                    |          |         |      |      |        |                                                                                                                                                                                    |

| Start-Up Time                    | TS0      | _       | 4.5  | 25   | ms     | $A_{OUT}$ = Analog, 2.5V, Time interval<br>between $V_{IN}$ = $V_{IN}$ _UVHI to $A_{OUT}$<br>reaches 2.5V, Refresh =1.6kHz,<br>$T_A$ = 25°C, GBNT                                  |

|                                  | TS1      | _       | 4.7  | 26   |        | A <sub>OUT</sub> =Analog, 2.5V, Time interval<br>between V <sub>IN</sub> =V <sub>IN_UVHI</sub> to A <sub>OUT</sub><br>reaches 2.5V, Refresh=0.8kHz,<br>T <sub>A</sub> = 25°C, GBNT |

|                                  | TS2      | _       | 6.0  | 28   |        | A <sub>OUT</sub> =Analog, 2.5V, Time interval<br>between V <sub>IN</sub> =V <sub>IN UVHI</sub> to A <sub>OUT</sub><br>reaches 2.5V, Refresh=400Hz,<br>TA=25°C, GBNT                |

|                                  | TS3      | _       | 8.5  | 30   |        | A <sub>OUT</sub> =Analog, 2.5V, Time interval<br>between V <sub>IN</sub> =V <sub>IN UVHI</sub> to A <sub>OUT</sub><br>reaches 2.5V, Refresh=200Hz,<br>T <sub>A</sub> =25°C, GBNT   |

## LX34211

## **Electrical Characteristics (Continued)**

| Parameters                               | Symbol             | Min.  | Тур. | Max.  | Units            | Conditions                                                                                                                                           |

|------------------------------------------|--------------------|-------|------|-------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| D <sub>OUT</sub> (PWM, Open-Drain)       |                    |       |      | I     |                  |                                                                                                                                                      |

| Frequency                                | D <sub>OUT01</sub> | 1.556 | 1.6  | 1.644 | kHz              | Refresh = 1.6 kHz, after trimming, +25°C                                                                                                             |

| Minimum PWM Duty                         | D <sub>OUT02</sub> |       | 0.3  | _     | %                | HCLMP = 1023, LCLMP = 0, ORI-<br>GIN = 0, Frequency = 1.6 kHz                                                                                        |

| Maximum PWM Duty                         | D <sub>OUT03</sub> | _     | _    | 100   | %                | No clamped output                                                                                                                                    |

| PWM Jitter                               | D <sub>OUT04</sub> | _     | 0.2  | _     | %P               | %P = % Period                                                                                                                                        |

| Maximum Sink Current                     | D <sub>OUT05</sub> | _     | _    | -35   | mA               | D <sub>OUT</sub> = OD PWM                                                                                                                            |

| A <sub>OUT</sub> (As Address Select      | •                  |       |      | •     | •                |                                                                                                                                                      |

| High-Level Input Voltage                 | AOUT_VIH           | 2.0   |      | _     | V                |                                                                                                                                                      |

| Low-Level Input Voltage                  | AOUT_VLO           | _     |      | 0.3   | V                |                                                                                                                                                      |

| A <sub>OUT</sub> (Analog Output)         |                    |       |      |       |                  |                                                                                                                                                      |

| A <sub>OUT</sub> Analog Range            | AOUT_R             | 0     | 1    | 100   | %V <sub>IN</sub> | A <sub>OUT</sub> level is dependent of V <sub>IN</sub>                                                                                               |

| A <sub>OUT</sub> Low Voltage             | VAOUT_LO           | _     |      | 4     | %V <sub>IN</sub> | $R_{L\_AOUT} = 10 \text{ k}\Omega \text{ to } V_{IN}$                                                                                                |

| A <sub>OUT</sub> High Voltage            | VAOUT_HI           | 96    |      |       | %V <sub>IN</sub> | $R_{L\_AOUT}$ = 10 k $\Omega$ to GND                                                                                                                 |

| A <sub>OUT</sub> Output Load             | RL_AOUT            | 7     | 10   | _     | kΩ               |                                                                                                                                                      |

| A <sub>OUT</sub> Sink Current            | I <sub>AOUT0</sub> | -8    | _    | 15    | mA               | A <sub>OUT</sub> = 0V                                                                                                                                |

| A <sub>OUT</sub> Source Current          | I <sub>AOUT5</sub> | 6     | _    | 15    | mA               | A <sub>OUT</sub> = 5V                                                                                                                                |

| A <sub>OUT</sub> Slew Rate               | AOUTSR1            | _     | 0.2  | _     | V/µs             | C <sub>LOAD</sub> = 22 nF                                                                                                                            |

|                                          | AOUTSR2            | _     | 0.1  | _     |                  | C <sub>LOAD</sub> = 100 nF                                                                                                                           |

| Ratiometric Error                        | $V_{RatioErr}$     | -0.2  | 0    | 0.2   | %V <sub>IN</sub> |                                                                                                                                                      |

| Fault Output Low Level                   | VAOUT_FL10K        |       | _    | 1     | %V <sub>IN</sub> | RL_AOUT = $10 \text{ k}\Omega$ to $V_{IN}$                                                                                                           |

|                                          | VAOUT_FL1K         |       | _    | 15    |                  | RL_AOUT = 1 kΩ to V <sub>IN</sub>                                                                                                                    |

| Fault Output High Level                  | VAOUT_FH10K        | 98    | _    | _     | %V <sub>IN</sub> | RL_AOUT = 10 k $\Omega$ to GND                                                                                                                       |

|                                          | VAOUT_FH1K         | 97    | _    | _     |                  | RL_AOUT = 1 k $\Omega$ to GND                                                                                                                        |

| Ground Off Output Low<br>Level           | VAOUT_GF125C       |       | _    | 4     | %V <sub>IN</sub> | Broken GND, $8 \text{ k}\Omega \leq \text{RL\_AOUT} \leq$<br>50 k $\Omega$ to external ground,<br>$T_A \leq +125^{\circ}\text{C}$                    |

|                                          | VAOUT_GF105C       |       | _    |       |                  | Broken GND, 50 kΩ < RL_AOUT ≤ 160 kΩ to external ground, T <sub>A</sub> ≤ +105°C                                                                     |

|                                          | VAOUT_GF85C        |       | _    |       |                  | Broken GND, 160 kΩ ≤ RL_AOUT < 600 kΩ to external ground, $T_A \le +85$ °C.                                                                          |

|                                          | VAOUT_GF           |       | _    |       |                  | Broken GND, 7 k $\Omega$ ≤ RL_AOUT < 8 k $\Omega$ to external ground.<br>With 10 k $\Omega$ assist pull-up on board between V <sub>IN</sub> and GND. |

| Ground Off Output High Level             | VAOUT_GF1K         | 99    | 100  | _     | %V <sub>IN</sub> | Broken GND, RL_AOUT $\ge 1 \text{ k}\Omega$ to $V_{IN}$                                                                                              |

| V <sub>IN</sub> Open Output Low<br>Level | VAO_VIN1K          | _     | 0    | 1     | %V <sub>IN</sub> | Broken V <sub>IN</sub> , RL_AOUT ≥ 1 kΩ to GND                                                                                                       |

| A <sub>OUT</sub> Over voltage threshold  | VAOUT_OV           |       | 108  |       |                  | Current limit not to damage A <sub>OUT</sub> internal circuit.                                                                                       |

| A <sub>OUT</sub> (PWM Output)            |                    |       |      |       |                  |                                                                                                                                                      |

### **Electrical Characteristics (Continued)**

**Electrical Specifications:** Unless otherwise indicated, the following specifications apply over the operating temperature range of -40°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C and the following test conditions: V<sub>IN</sub> = 5V, V<sub>DD</sub> = 3.5V, I<sub>DD</sub> = 5 mA, I<sub>I/O</sub> = 0 mA. Typical values are at +25°C.

| Parameters                           | Symbol                             | Min.  | Тур.  | Max. | Units            | Conditions                                   |  |

|--------------------------------------|------------------------------------|-------|-------|------|------------------|----------------------------------------------|--|

| High-Level Output<br>Voltage         | V <sub>OH</sub>                    | 95    |       | 100  | %V <sub>IN</sub> | Duty = 50%, 10 kΩ pull-down to GND           |  |

| Low-Level Output Voltage             | $V_{OL}$                           | 0     | _     | 200  | mV               | Duty = 50%, 10 kΩ pull-up to V <sub>IN</sub> |  |

| Rise Time                            | AOUT_TR                            | _     | 10    |      | μs               | Duty = 50%, max $C_{LOAD}$ = 10 nF           |  |

| Fall Time                            | AOUT_TF                            | _     | 10    | _    | μs               | Duty = 50%, max C <sub>LOAD</sub> = 10 nF    |  |

| Minimum Duty                         | $D_{min}A_{OUT}$                   | _     | _     | 4    | %                | PWM (PP)                                     |  |

| Maximum Duty                         | D <sub>max</sub> _A <sub>OUT</sub> | 94    | _     | _    | %                | PWM (PP)                                     |  |

| Max. Drive/Sink Current              | IAOUTP                             | -35   | _     | 35   | mA               | A <sub>OUT</sub> = PWM                       |  |

| Output CLAMP                         |                                    |       |       |      |                  |                                              |  |

| Clamp High Output Level              | HCLMP                              | 0     | _     | 99.9 | %V <sub>IN</sub> | Pull-up Output to V <sub>IN</sub>            |  |

| Clamp Low Output Level               | LCLMP                              | 0     | _     | 99.9 | %V <sub>IN</sub> | Pull-up Output to V <sub>IN</sub>            |  |

| <b>EEPROM Programming</b>            |                                    |       |       |      |                  |                                              |  |

| Programming Mode<br>Enable Threshold | VIN_EE_ENTH                        | 6.1   | 6.384 | 6.7  |                  | For Entering EEPROM program-<br>ming mode    |  |

| Program Low                          | VIN_PL                             | 9.5   | 10    | 10.5 | V                | For EEPROM programming mode                  |  |

| Program Idle                         | VIN_PI                             | 11.75 | 13    | 13.5 | V                | For EEPROM programming mode                  |  |

| Program High                         | VIN_PH                             | 14.75 | 16    | 17   | V                | For EEPROM programming mode                  |  |

| Duration Time                        | td                                 | 25    | _     | _    | μs               | Duration time for each voltage state         |  |

| Maximum Clock Period from Programmer | PRGCLKmax                          |       |       | 110  | μs               |                                              |  |

## Temperature Specifications<sup>(1)</sup>

| Parameters                                 | Symbol        | Min. | Тур. | Max. | Units | Conditions |

|--------------------------------------------|---------------|------|------|------|-------|------------|

| Thermal Resistance,<br>Junction to Ambient | $\theta_{JA}$ | _    | +117 | _    | °C/W  |            |

| Thermal Resistance,<br>Junction to Case    | θјс           | _    | +22  | _    | °C/W  |            |

Note 1: The  $\theta_{JA}$  numbers assume no forced airflow. Junction temperature is calculated using the formula:  $T_J = T_A + (P_D \times \theta_{JA})$ . In particular,  $\theta_{JA}$  is a function of the Printed Circuit Board (PCB) construction. The stated number above is for a four-layer board in accordance with JESD-51-7 (JEDEC®).

## 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1.

TABLE 2-1: PIN DESCRIPTIONS

| 14-Lead<br>TSSOP | Symbol           | Description                                                                                                                                                                                                                                                                                                                                                       |

|------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | GND              | Analog and Digital Power Ground pin.                                                                                                                                                                                                                                                                                                                              |

| 2                | D <sub>OUT</sub> | Digital Out pin. This pin can be programmed to open-drain PWM with current limit.                                                                                                                                                                                                                                                                                 |

| 3                | A <sub>OUT</sub> | Analog Out pin. This pin can be programmed to provide an analog output (DAC), threshold detector, or a PWM output. PWM will be the push-pull operation. This pin can be used as an address pin for EEMODE.                                                                                                                                                        |

| 4                | V <sub>IN</sub>  | Power Supply and Internal EEPROM Programming pin. DC input power is applied to this pin for normal operation. It is also used for EEPROM programming. Bypass this pin to GND pin with a low-ESR capacitor. The recommended value is between 100 nF and 1 $\mu$ F. A larger capacitance will affect the EEPROM programming.                                        |

| 5                | V <sub>DD</sub>  | Regulator Output pin. This is the output of the internal voltage regulator providing power to the analog and digital blocks. Bypass this pin to GND pin with a low-ESR capacitor not lower than $0.1~\mu F$ .                                                                                                                                                     |

| 6, 7             | NC               | Not Connected. These pins are not internally connected.                                                                                                                                                                                                                                                                                                           |

| 8                | CL1              | Sensor Signal from Secondary Coil 1 of Inductive Sensor pin.                                                                                                                                                                                                                                                                                                      |

| 9                | GNDCL            | Reference Ground for CL1 and CL2 pins. Connect CL1 and CL2 coils to GNDCL and connect the GNDCL to GND directly.                                                                                                                                                                                                                                                  |

| 10               | CL2              | Sensor Signal from Secondary Coil 2 of Inductive Sensor pin.                                                                                                                                                                                                                                                                                                      |

| 11               | EEWR             | EEWR is active-low. When EEWR is low, it prohibits change to the internal EEPROM contents. The pin contains an internal pull-down so it can be left floating for normal use. If an external pull-down is desired, the SUB pin must be used as reference, and not GND. To unlock when the LOCK bits are set to '1', pull this pin to $V_{DD}$ with 10 k $\Omega$ . |

| 12               | OSC2             | Oscillator Pin 2. It connects to the second side of the primary inductor coil. An external capacitor is connected between this pin and GND as part of the LC tank circuit. The external capacitor should be low-ESR, C0G or NP0, or equivalent, rated voltage 50V.                                                                                                |

| 13               | OSC1             | Oscillator Pin 1. It connects to the first side of the primary inductor coil. An external capacitor is connected between this pin and GND as part of the LC tank circuit. The external capacitor should be low-ESR, C0G or NP0, or equivalent, rated voltage 50V.                                                                                                 |

| 14               | SUB              | Substrate pin. It is used for ground failure protection. It should not be connected to GND. For normal applications, leave this pin open.                                                                                                                                                                                                                         |

### 3.0 EEPROM CONFIGURATION

The LX34211 integrates a 16 words by 16 bits (256 bits), user-programmable EEPROM for storing calibration and configuration parameters. The calibration parameters enable the production sensor assembly to be customer-factory calibrated assuring consistent unit to unit performance.

Table 3-1 itemizes the LX34211 Configuration EEPROM contents and Table 3-2 shows the LX34211 EEPROM Configuration map. Note that EEPROM contents of ID and Reserved shall be kept as original value when EEPROM is reprogrammed.

TABLE 3-1: LX34211 EEPROM CONFIGURATION

| Name      | Description                           | Size<br>(bits) | Words and Bits<br>(MSb:LSb)         | Sign | Min.<br>Value | Max.<br>Value | Default<br>Value |

|-----------|---------------------------------------|----------------|-------------------------------------|------|---------------|---------------|------------------|

| ID        | Customer Part ID                      | 18             | W0[15:0]<br>W1[15:14]               | No   | 0             | 3FFFF         | Serial #         |

| REFRESH   | Refresh Rate                          | 2              | W1[13:12]                           | No   | 0             | 3             | 0                |

| Reserved  | Factory TRIM (Main Oscillator)        | 5              | W1[11:7]                            | _    | _             | _             | Factory Trim     |

| Reserved  | Factory TRIM (VDD)                    | 3              | W1[2:0]                             | _    | _             | _             | Factory Trim     |

| GADJ      | Front-end PGA Gain                    | 3              | W1[6:4]                             | Yes  | 100b          | 101b          | 0                |

| FBK       | Radius of closed loop                 | 1              | W1[3]                               | No   | 0             | 1             | 1                |

| CHKSUM    | 4-bit Checksum Value                  | 4              | W2[15:12]                           | No   | 0             | _             | _                |

| S5        | Slope of Sixth Segment                | 12             | W2[11:0]                            | No   | 0             | 4095          | 511              |

| OUTSEL    | Output Setup                          | 4              | W3[15:12]                           | No   | _             | _             | 1011B            |

| S0        | Slope of First Segment                | 12             | W3[11:0]                            | No   | 0             | 4095          | 511              |

| ORIGIN    | Origin                                | 12             | W4[15:12]<br>W5[15:12]<br>W6[15:12] | No   | 0             | 4095          | 0                |

| Y5        | Linearization Point 5<br>Y-Coordinate | 12             | W4[11:0]                            | No   | 0             | 4095          | 3413             |

| X5        | Linearization Point 5<br>X-Coordinate | 12             | W5[11:0]                            | No   | 0             | 4095          | 3413             |

| Y3        | Linearization Point 3<br>Y-Coordinate | 12             | W6[11:0]                            | No   | 0             | 4095          | 2047             |

| OSCOMP    | OSC Voltage Compensation              | 8              | W7[15:12]<br>W8[15:12]              | No   | 0             | 255           | 255              |

| X3        | Linearization Point 3<br>X-Coordinate | 12             | W7[11:0]                            | No   | 0             | 4095          | 2047             |

| Y1        | Linearization Point 1<br>Y-Coordinate | 12             | W8[11:0]                            | No   | 0             | 4095          | 683              |

| FILTER    | Select Digital Filter                 | 1              | W9[15]                              | No   | 0             | 1             | 1                |

| Reserved1 | Reserved1                             | 3              | W9[14:12]                           | No   | 0             | 112           | 111B             |

| X1        | Linearization Point 1<br>X-Coordinate | 12             | W9[11:0]                            | No   | 0             | 4095          | 683              |

| Reserved  | Reserved                              | 12             | W10[15:10]<br>W11[15:10]            | No   | 0             | 4095          | 4089             |

| LCLMP     | Low Clamp                             | 10             | W10[9:0]                            | No   | 0             | 1023          | 1                |

| HCLMP     | High Clamp                            | 10             | W11[9:0]                            | No   | 0             | 1023          | 1023             |

| Y2        | Linearization Point 2<br>Y-Coordinate | 6              | W12[15:10]                          | Yes  | -31           | 31            | 0                |

| DSIN      | Dynamic Sine Offset                   | 10             | W12[9:0]                            | Yes  | -511          | 511           | 0                |

| Y4        | Linearization Point 4<br>Y-Coordinate | 6              | W13[15:10]                          | Yes  | -31           | 31            | 0                |

| SSIN      | Static Sine Offset                    | 10             | W13[9:0]                            | Yes  | -511          | 511           | 0                |

TABLE 3-1: LX34211 EEPROM CONFIGURATION

| Name     | Description                      | Size<br>(bits) | Words and Bits<br>(MSb:LSb) | Sign | Min.<br>Value | Max.<br>Value | Default<br>Value |

|----------|----------------------------------|----------------|-----------------------------|------|---------------|---------------|------------------|

| IOSC     | OSC Current Source               | 2              | W14[15:14]                  | No   | 0             | 3             | 0                |

| DEBUG    | Debug                            | 1              | W14[13]                     | No   | 0             | 1             | 0                |

| Reserved | Reserved                         | 1              | W14[12]                     | No   | 0             | 1             | 0                |

| CLSEL    | CL1, 2 Input Select              | 1              | W14[11]                     | No   | 0             | 1             | 0                |

| EELOCK   | EEPROM Write Protection          | 1              | W14[10]                     | No   | 0             | 1             | 0                |

| DCOS     | Dynamic Cosine Offset Correction | 10             | W14[9:0]                    | Yes  | -511          | 511           | 0                |

| GMTCH    | Gain Match                       | 6              | W15[15:10]                  | Yes  | -12.09%       | 12.09%        | 0                |

| SCOS     | Static Cosine Offset Correction  | 10             | W15[9:0]                    | Yes  | -511          | 511           | 0                |

TABLE 3-2: LX34211 EEPROM CONFIGURATION MAP

|        | MSb    | _      | _        |       | _       | _         | _        |      |   |       | _     | _     |     |    |          | LSb |  |  |  |

|--------|--------|--------|----------|-------|---------|-----------|----------|------|---|-------|-------|-------|-----|----|----------|-----|--|--|--|

|        | 15     | 14     | 13       | 12    | 11      | 10        | 9        | 8    | 7 | 6     | 5     | 4     | 3   | 2  | 1        | 0   |  |  |  |

| WORD0  |        |        |          |       |         |           | ID[      | 172] |   |       |       |       |     |    |          |     |  |  |  |

| WORD1  | ID[1   | 10]    | REFF     | RESH  |         | Reser     | ved[117  | 7]   |   | G     | ADJ[6 | 4]    | FBK | Re | served[2 | 20] |  |  |  |

| WORD2  |        | CHKSL  | JM[30]   |       |         |           |          |      |   | S5[11 | .0]   |       |     |    |          |     |  |  |  |

| WORD3  |        | OUTS   | EL[30]   |       | S0[110] |           |          |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD4  |        | ORIGII | N[118]   |       |         | Y5[110]   |          |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD5  |        | ORIGI  | N[74]    |       |         |           | X5[110]  |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD6  |        | ORIGI  | N[30]    |       |         |           |          |      |   | Y3[11 | .0]   |       |     |    |          |     |  |  |  |

| WORD7  |        | OSCO   | MP[74]   |       |         | X3[110]   |          |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD8  |        | OSCO   | MP[30]   |       | Y1[110] |           |          |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD9  | FILTER | F      | RSVD1[20 | )]    | X1[110] |           |          |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD10 |        |        | RSVE     | [116] |         |           |          |      |   |       | LCLM  | P[90] |     |    |          |     |  |  |  |

| WORD11 |        |        | RSVI     | D[50] |         | HCLMP[90] |          |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD12 |        |        | Y2[      | 50]   |         |           | DSIN[90] |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD13 |        |        | Y4[      | 50]   |         |           | SSIN[90] |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD14 | IOSC   | [10]   | FMSK     | RSVD  | CLSEL   | EELOCK    | DCOS[90] |      |   |       |       |       |     |    |          |     |  |  |  |

| WORD15 |        | •      | GMTC     | H[50] |         |           | SCOS[90] |      |   |       |       |       |     |    |          |     |  |  |  |

#### 3.1 ID

This is the ID field. The Customer Part ID is an 18-bit field containing customer part identification information.

#### 3.2 CHKSUM

This 4-bit value is a 4-bit cyclic redundancy check (CRC) to check the rest of content reliability through lifetime. The CRC calculation is based on the code as shown in Example 3-1. Sum2 is 4-bit checksum.

### 3.3 Reserved

The Reserved bits contain factory trimmed information. It shall be kept the factory value when EEPROM is updated by the user.

#### **EXAMPLE 3-1:**

```

uint16 t data[16];

#define GENPOLY 0x0013U /* x^4 + x + 1 */

uint32 t makecrc4(uint32 t b)

* Takes b as input, which should be the information vector already multiplied by x^4 (ie. shifted

* over 4 bits), and returns the crc for this input based on the defined generator polynomial GENPOLY

uint32_t i;

i = 1 U:

while (b>=16U) { /* >= 2^4, so degree(b) >= degree(genpoly) */

if ((((b >> (20U-i))) & 0x1U) == 1U)

b ^= GENPOLY << (16U-i); /* reduce with GENPOLY */

i++;

}

return b;

void Calculate_CRC(void)

int sum2=0, sum1=0;

for (uint8_t counter = 0U; counter <= 16U; counter++) {

if (counter != 2U) {

sum1 += data[counter];

} else {

sum1 += data[counter] & 0x0FFFU;

sum2 = makecrc4(((sum1 >> 16)^(sum1&0xFFFFU)) << 4);

cout<< " IC CRC :"<<sum2<<end1<<end1;</pre>

```

#### 3.4 FILTER

This bit selects the digital filter type. Setting the bit to '0' will set the filter type to SINC and setting the bit to '1' will set the filter to SINC + FIR. See Table 3-3.

**TABLE 3-3: FILTER CONFIGURATION**

| Filter Bit | Filter Type |

|------------|-------------|

| 0          | SINC        |

| 1          | SINC + FIR  |

#### 3.5 REFRESH

This parameter sets the value of the refresh rate of the ADC update. If the PWM output is selected, the PWM frequency is always equal to the ADC update rate. See Table 3-4.

TABLE 3-4: REFRESH BIT CONFIGURATION

| Bit Value | Refresh Rate |

|-----------|--------------|

| 0         | 1.6 kHz      |

| 1         | 0.8 kHz      |

| 2         | 400 Hz       |

| 3         | 200 Hz       |

#### 3.6 **IOSC**

These two bits set the oscillator tail current value. See Table 3-5.

TABLE 3-5: IOSC CONFIGURATION

| IOSC Bits | Tail Current | Feedback |

|-----------|--------------|----------|

| 0.0       | Full Range   | Enabled  |

| 01        | 1/2          | Enabled  |

| 10        | 1/4          | Enabled  |

| 11        | 1/8          | Enabled  |

#### 3.7 EELOCK

There are two control signals: one is from the EEWR pin (if set to Active-Low, it disables to write EEPROM at EEMODE) and the other is for the EELOCK bits on the Configuration EEPROM (W14[10]). If the EELOCK bit is set to '1' and the EEWR pin is pulled to low, the EEPROM cannot be written. The default value of W14[10] is '0'.

#### 3.8 OUTSEL

The OUTSEL bits provide the various output selection options. See Table 3-6.

TABLE 3-6: OUTSEL BITS CONFIGURATION

|                 | Output Cor       | nfigura         | tion             |                                 |

|-----------------|------------------|-----------------|------------------|---------------------------------|

| Bit 1,<br>Bit 0 | A <sub>OUT</sub> | Bit 3,<br>Bit 2 | D <sub>OUT</sub> | Remarks                         |

| 00              | Reserved         | 00              | Reserved         |                                 |

| 01              | Reserved         | 01              | Reserved         |                                 |

| 10              | PWM (PP)         | 10              | OD_PWM           | PP = Push-Pull, OD = Open-Drain |

| 11              | Analog           | 11              | Reserved         |                                 |

#### **3.9 SCOS**

Static offset correction of the CL1 input channel used in input correction calculations.

#### 3.10 DCOS

Dynamic offset correction of the CL1 input channel used in input correction calculations.

#### 3.11 **SSIN**

Offset correction of the CL2 input channel used in input correction calculations.

#### 3.12 **DSIN**

Dynamic offset correction of the CL2 input channel used in input correction calculations.

#### 3.13 **GMTCH**

Value of the input channel gain mismatch correction used in input correction calculations.

#### 3.14 OSCOMP

Maximum amplitude of the oscillator swing used in the input correction calculations. The maximum value of the OSCOMP is 255, Step 1. Multiplied by 4, it converts as internal OSCOMP data.

#### 3.15 ORIGIN

Offset value of the system origin relative to fore-and-after position. This is not a DC output offset adjustment. Verify that the LCLMP and HCLMP parameters are not limiting the output range. Multiplied by 2, it converts as internal ORIGIN data.

#### 3.16 **HCLMP**

This parameter sets the output high clamp level. The output is clamped at this value if the output swing can go above this level. The HCLMP value used in

calculations is  $8 \times (\text{value} + 1) - 1$  on W11[9:0]. It reduces the maximum output swing. Maximum level is achieved with HP = 1023.

#### 3.17 LCLMP

This parameter sets the output low clamp level. The output is clamped at this level if the output swing can go below this level. The LCLMP value raises the minimum output value from 0. The LCLMP value used in calculations is  $8 \times (value - 1)$  on W10[9:0]. An output value of 0 is achieved with LCLMP = 1. The LCLMP setting value overrides the HCLMP setting if both settings are crossed over.

#### 3.18 S0

This parameter sets the slope of the first linearization segment.

#### 3.19 X1 and Y1

The value of the X and Y coordinates for the first linearization point. Multiplied by 2, it converts as internal data.

#### 3.20 X3 and Y3

The value of the X and Y coordinates for the third linearization point. Multiplied by 2, it converts as internal data.

#### 3.21 X5 and Y5

The value of the X and Y coordinates for the fifth (and last) linearization point. Multiplied by 2, it converts as internal data.

#### 3.22 S5

This parameter sets the slope of the last linearization segment.

#### 3.23 Y2

The value of X2 is calculated by X1 and X3 parameters as X2 = (X1 + X3)/2. The Y2 value is the value that can adjust the coordinates for the second linearization point. The Y2 value has polarity and the calculated value of the second coordinate (y) at X2 is y = (Y1 + Y3)/2 + Y2. Multiplied by 2, it converts as internal data.

#### 3.24 Y4

The value of X4 is calculated by X3 and X5 parameters as X4 = (X3 + X5)/2. The Y4 value is the value that can adjust the coordinates for the fourth linearization point. The Y4 value has polarity and the calculated value of the fourth coordinate (y) at X4 is y = (Y3 + Y5)/2 + Y4. Multiplied by 2, it converts as internal data.

#### 3.25 CLSEL

The CLSEL bit selects the CL1 or CL2 inputs as sine or cosine inputs. When CLSEL is set to '1', the CL1 input is selected as a sine value and the CL2 input is selected as a cosine input. When CLSEL is set to '0', the CL1 input is selected as a cosine value and the CL2 input is selected as a sine value.

#### 3.26 **GADJ**

This parameter is used to adjust the gain of the Programmable Gain Amplifier (PGA). The bit, WORD1[6], is the polarity bit. The remaining two bits adjust gains. The default gain ('000b') is 3.125. Refer to **Section 4.3** "Input Amplifier and Signal Conditioning" for more information.

#### 3.27 FBK

The Bit W1[3] of the EEPROM is used to set FBK radius setting. This is user selectable. Bit value = 0 sets 50mVpp radius and Bit value =1 sets to 100mVpp radius. Factory Default setting is 1.

#### 4.0 THEORY OF OPERATION

#### 4.1 General Information

The LX34211 is a highly integrated programmable data conversion IC designed for interfacing to and managing of inductive sensors. The device includes an integrated oscillator circuit for driving the primary coil of an inductive sensor, along with two independent analog conversion paths for conditioning, converting, and processing of two analog signals from the secondary coils of the PCB sensor. Each path includes an EMI filter, demodulator, anti-alias filter, programmable amplifier, and a 13-bit Sigma-Delta Analog-to-Digital Converter before the signal processing unit. The signal processing unit peripherals include programmable PWM controller and a 12-bit digital-to-analog converter.

#### 4.2 Oscillator

The on-chip excitation circuit provides a excitation current to oscillate and maintain parallel resonant circuit to generate the carrier signal for driving the primary coil of the inductive sensor via pins OSC1 and OSC2. The oscillator operates over a frequency range from 1 MHz to 5 MHz as shown in Equation 4-1.

#### **EQUATION 4-1:**

$f = \frac{1}{2\pi\sqrt{L_{eq}C_{eq}}}$

Where:

L<sub>eq</sub> = Inductance of coil between OSC1 and OSC2 pins

$C_{eq}$  = Tanking capacitance between OSC1 and OSC2 pins.  $C_{eq} \approx C1 * C2/(C1 + C2)$

The value of the inductor  $L_{eq}$  is the most critical element in the cross-coupled LC tank oscillator. Because the inductance is relatively low, the parasitic resistance of Leq can dominate and impact the ability to maintain oscillation. As such, the value of the inductor  $L_{eq}$  should be as large as possible and with a high Q factor. The external capacitor should be low-ESR, COG or NPO, or equivalent and 50V rated.

In most applications, the inductor  $L_{\rm eq}$  is implemented as traces on a PCB. Depending on the processing of the PCB, the height and width of the trace will vary, resulting in a variation of the inductance  $L_{\rm eq}$  and of the parasitic resistance. Because these variations will change from PCB to PCB, it is necessary to calibrate each PCB sensor independently. Care should be taken to select a PCB source which can achieve the manufacturing tolerances required by a given set of system requirements.

The amplitude of the carrier signal is a function of the primary coil tank circuit configuration and feedback of the secondary coil signals from the CL1 and CL2 inputs. The shoulder signals of the tank circuit are detected by an internal circuit. It will distort the sinusoidal waveform if the tank circuit and the secondary coil feedback signal are not within design limits.

In order to detect system Faults, the IC monitors the amplitude of the carrier signal on pin OSC1. When the amplitude is above or below the specified amplitude (see OSCILLATOR: OSC1 Over Voltage ( $V_{OSC\_OV}$ ) and OSC1 Under Voltage ( $V_{OSC\_UV}$ ), in the **Electrical Characteristics** section), the  $A_{OUT}$  output pin is forced to 0V. This output level indicates a system Fault. When initially calibrating a sensor, the voltage on OSC1 should be monitored in order to verify that the amplitude is within the specified range.

The optimal level of OSC1 is about  $6V_{PP}$ , with target at typical air gap distance. If the OSC1 voltage is too high, the signal levels at CL1 and CL2 may be too low. If the OSC1 voltage is too low, the signal levels at CL1 and CL2 may be too high.

Internal feedback circuit adjusts the current drive of the exciter in order to maintain the signal relationship:

#### **EQUATION 4-2:**

$$a^2 \sin^2 \theta + b^2 \cos^2 \theta = k^2$$

Where 'k' is the function of the current source amplitude controlled by the 'FBK' parameter on the EEPROM, coefficients 'a' and 'b' are the relative areas of the two secondary coils whose signals are applied to CL1 and CL2, typically two values are equal to each other by sensor design.

# 4.3 Input Amplifier and Signal Conditioning

Pins CL1 and CL2 are the inputs to analog front-end (AFE) block paths.

The front-end gain amplifier can be programmed with 4 bits, where the 0000b default gain value is 3.125. Bit value percentage changes can be done as shown in Table 4-1.

TABLE 4-1: PROGRAMMABLE GAIN AMPLIFICATION SETTING

| Bit # | Function           |

|-------|--------------------|

| 0     | Amplification +6%  |

| 1     | Amplification +12% |

| 2     | Amplification -24% |

The output of the front-end gain amplifier is then passed through an anti-aliasing filter prior to input to the Sigma-Delta ADC.

# 4.4 Sigma-Delta ADC with Digital Filters

Each analog path includes a 4th-order 13-bit Sigma-Delta ADC with precision internal voltage reference, which produces true 12-bit measurement results. The sampling frequency for the ADC is derived from the main clock and selected by REFRESH in the configuration EEPROM. See Table 4-2.

TABLE 4-2: SAMPLING FREQUENCY

| REFRESH | Function                  |

|---------|---------------------------|

| 00      | ADC clock = Main clock/8  |

| 01      | ADC clock = Main clock/16 |

| 10      | ADC clock = Main clock/32 |

| 11      | ADC clock = Main clock/64 |

The ADC decimation filter includes a SINC filter and a half-band FIR filter. The SINC filter provides -40 dB of stop-band attenuation. Because the SINC filter does not provide the same sharp response as a finite/infinite filter response, a half-band FIR filter is also provided. The drawback of the FIR filter is that it adds delay to the input signal and this delay depends on the number of coefficients and the output data rate. The filter can be selected by the Filter setting in the configuration EEPROM.

#### 4.5 Embedded MCU

The LX34211 includes an embedded 32-bit microcontroller core, which is used to perform filtering and math functions on the digitized samples from the ADC. The device includes a set of preprogrammed filtering and math functions, which can be selected by setting the appropriate bits in the on-chip configuration EEPROM. Also, system calibration and linearization coefficient bits are included in the on-chip configuration EEPROM.

### 4.6 Configuration EEPROM

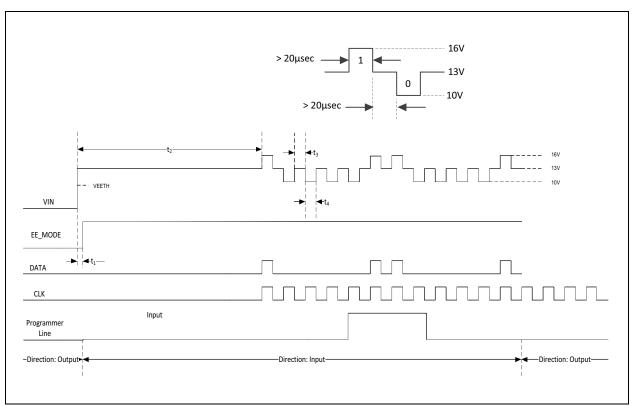

The LX34211 includes a user-programmable 16 x 16 bits EEPROM for storing configuration parameters into nonvolatile memory. The device is placed into EEPROM Programming mode (EEMODE) by increasing the voltage on the  $V_{\text{IN}}$  pin to  $6.5V(V_{\text{EETH}})$ .

Note that the data can be clocked only after  $t_2 > 4.4 \text{ ms}$  from last power-on, and the maximum  $t_2$  time is less than 12 ms.