## Product Change Notification / SYST-02D0ZZ491

# Date:

10-Mar-2023

# **Product Category:**

General Purpose FPGAs, System On Chip FPGAs

# **PCN Type:**

**Document Change**

# **Notification Subject:**

Data Sheet - SmartFusion2 Microcontroller Subsystem User Guide

# Affected CPNs:

SYST-02DOZZ491\_Affected\_CPN\_03102023.pdf SYST-02DOZZ491\_Affected\_CPN\_03102023.csv

# Notification Text:

SYST-02DOZZ491

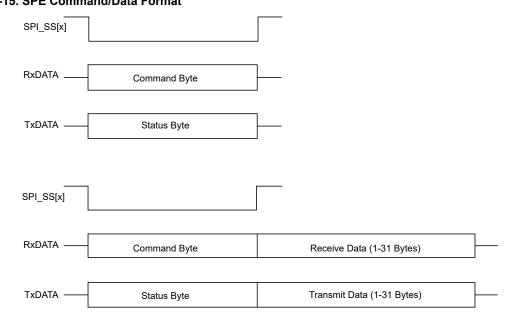

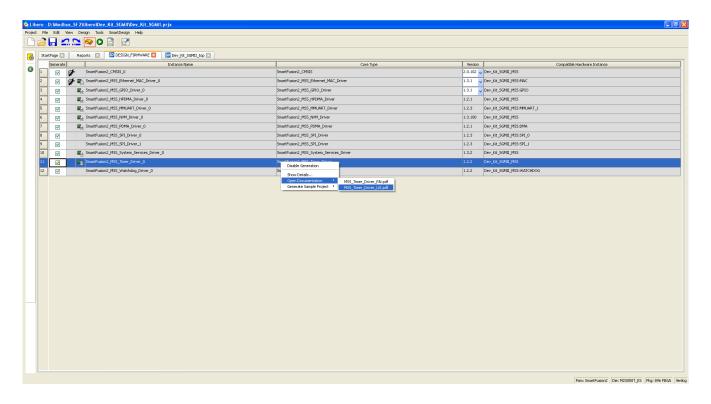

Microchip has released a new Datasheet for the SmartFusion2 Microcontroller Subsystem User Guide of devices. If you are using one of these devices please read the document located at SmartFusion2 Microcontroller Subsystem User Guide.

#### Notification Status: Final

#### Description of Change:

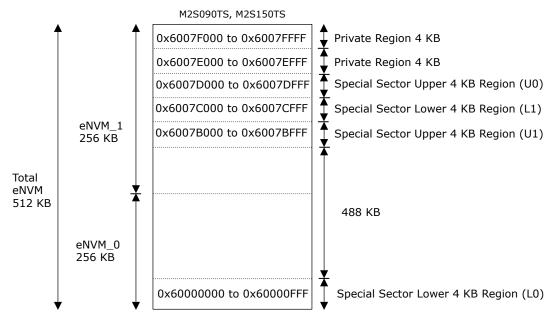

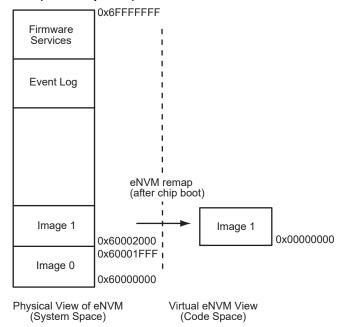

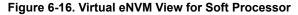

• Remapping eNVM data from eNVM\_1 memory block to Cortex®-M3 Code space is not permitted for SmartFusion® 2 M2S090/150 and IGLOO® 2 M2GL090/150 devices. For information about eNVM remapping and limitation, see the note under Figure 4-28.

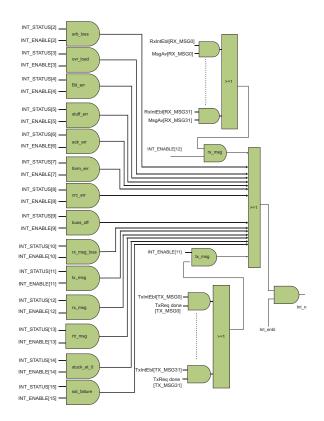

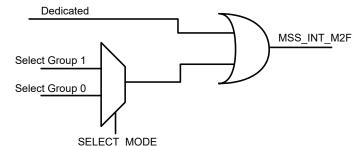

• Timing models for Fabric to MSS interrupts have been updated with additional time delay. This changes the timing arcs of nets and interface between Fabric to MSS interrupts. For more information about the updated timing arcs, see PCN 17005A.

• Updated 1.5.2.3. Embedded Trace Macrocell to include information about timing arcs update from Fabric to Embedded Trace Macrocell.

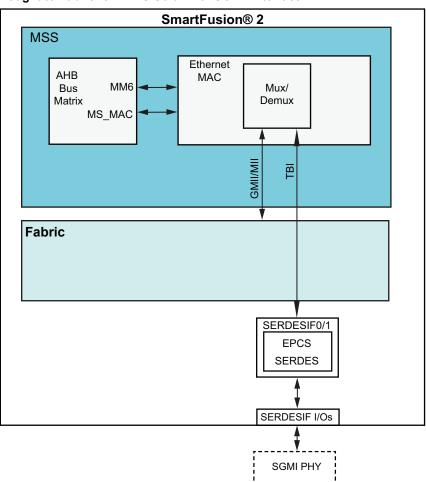

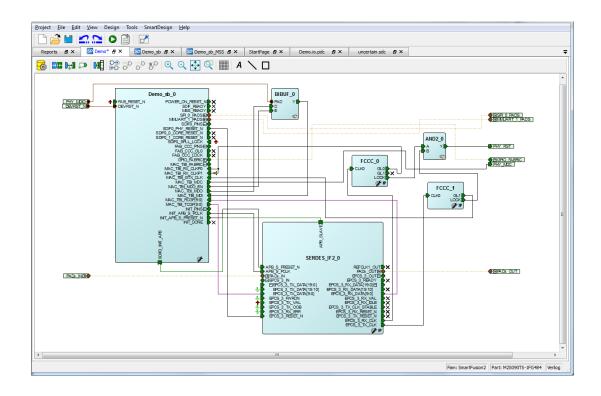

• Updated 10.5.1. SGMII Interface Configuration to include information about timing arcs update from SerDes to Fabric.

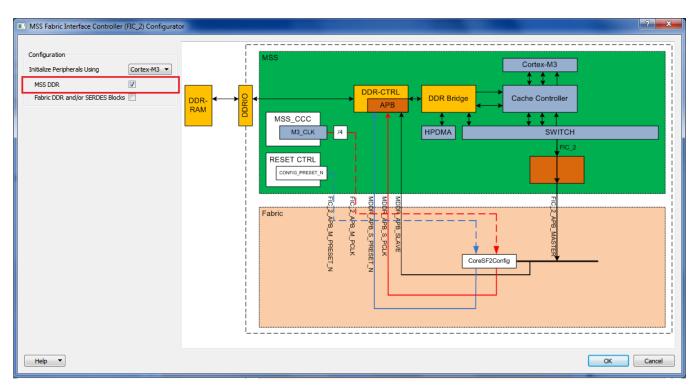

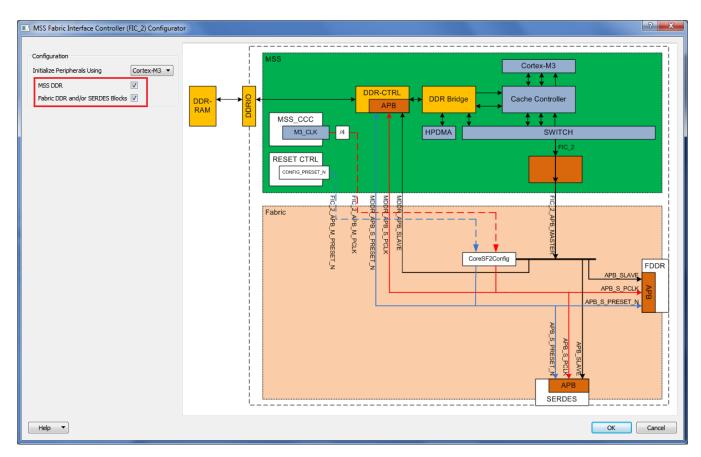

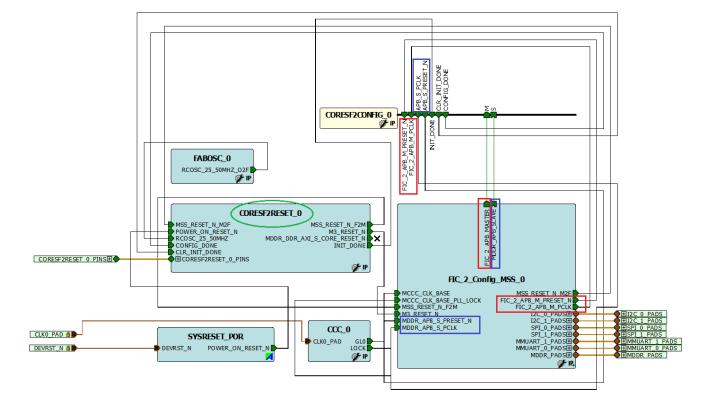

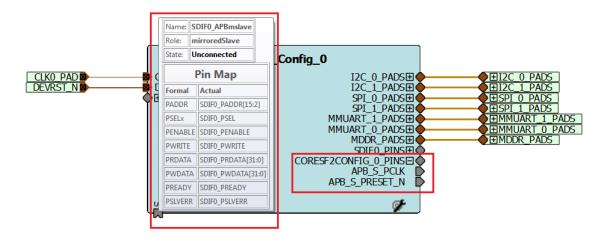

• Updated 22.3.1. Configuring the FIIC Using the Libero SoC to include information about timing arcs update from Fabric to MSS interrupts.

- The document was converted to Microchip template.

- The document number was changed to DS50003495 from UG0331.

Impacts to Data Sheet: See above details.

Reason for Change: To Improve Productivity

Change Implementation Status: Complete

Date Document Changes Effective: 10 Mar 2023

NOTE: Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

# Attachments:

SmartFusion2 Microcontroller Subsystem User Guide

Please contact your local Microchip sales office with questions or concerns regarding this notification.

## **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our PCN home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the PCN FAQ section.

If you wish to <u>change your PCN profile</u>, <u>including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections. Affected Catalog Part Numbers (CPN)

M2S090T-1FGG676S0027 M2S090T-1FGG676S0028 M2S090T-1FGG676S0030 M2S090T-1FGG676S0032 M2S090T-1FGG676X416 M2S090T-1FGG676Z246 M2GL150TS-FCVG484I M2S090TS-1FG484MX3 M2S090TS-1FG484MX399 M2S090TS-1FG484MX471 M2S090TS-1FG676 M2S090TS-1FG676I M2S090TS-1FG676IX417 M2S090TS-1FGG484 M2S090TS-1FGG484I M2S090TS-1FGG484IX416 M2S090TS-1FGG484IX418 M2S090TS-1FGG484M M2S090TS-1FGG484T2 M2S090TS-1FGG484X416 M2S090TS-1FGG484X418 M2S090TS-1FGG676 M2S090TS-1FGG676H0017 M2S090TS-1FGG676H0044 M2S090TS-1FGG676H0046 M2S090TS-1FGG676H0071 M2S090TS-1FGG676H0090 M2S090TS-1FGG676H0132 M2S090TS-1FGG676H0144 M2S090TS-1FGG676H0223 M2S150-1FCV484I M2S150-1FCVG484 M2S150-1FCVG484I M2S150-FC1152 M2S150-FC1152I M2S150-FCG1152 M2S150-FCG1152I M2S150-FCG1152X486 M2S150-FCS536 M2S150-FCS536I M2S150-FCSG536 M2S150-FCSG536I M2S150-FCV484 M2S150-FCV484I M2S150-FCVG484 M2S150-FCVG484I

M2S150T-1FC1152 M2S150T-1FC1152I M2S150T-1FC1152IX3 M2S150T-1FC1152M M2S150T-1FC1152MX259 M2S150T-1FCG1152 M2S150T-1FCG1152I M2S150T-1FCG1152IX417 M2S150T-1FCG1152M M2S150T-1FCG1152X416 M2S150T-1FCS536 M2S150T-1FCS536I M2S150T-1FCSG536 M2S150T-1FCSG536I M2S150T-1FCV484 M2S150T-1FCV484I M2S150T-1FCV484IX259 M2S150T-1FCV484IX3 M2S150T-1FCV484M M2S150T-1FCV484MX259 M2S150T-1FCVG484 M2S150T-1FCVG484I M2S150T-FC1152 M2S150T-FC1152I M2S150T-FC1152X416 M2S150T-FCG1152 M2S150T-FCG1152I M2S150T-FCG1152X416 M2S150T-FCG1152X417 M2S150T-FCS536 M2S150T-FCS536I M2S150T-FCSG536 M2S150T-FCSG536I M2S150T-FCV484 M2S150T-FCV484I M2S150T-FCVG484 M2S150T-FCVG484I M2S150T-FCVG484IX94 M2S150TS-1FC1152 M2S150TS-1FC1152I M2S150TS-1FC1152IX130 M2S150TS-1FC1152IX167 M2S150TS-1FC1152IX3 M2S150TS-1FC1152M M2S150TS-1FC1152MX259 M2S150TS-1FC1152MX417 M2S150TS-1FCG1152 M2S150TS-1FCG1152H0012 M2S150TS-1FCG1152H0038 M2S150TS-1FCG1152H0061 M2S150TS-1FCG1152H0084 M2S150TS-1FCG1152H0105 M2S150TS-1FCG1152H0121 M2S150TS-1FCG1152H0163 M2S150TS-1FCG1152H0186 M2S150TS-1FCG1152H0195 M2S150TS-1FCG1152H0261 M2S150TS-1FCG1152H0313 M2S150TS-1FCG1152H0327 M2S150TS-1FCG1152H0338 M2S150TS-1FCG1152H0342 M2S150TS-1FCG1152H0343 M2S150TS-1FCG1152H0354 M2S150TS-1FCG1152H0363 M2S150TS-1FCG1152I M2S150TS-1FCG1152IX417 M2S150TS-1FCG1152M M2S150TS-1FCG1152X416 M2S150TS-1FCG1152X417 M2S150TS-1FCS536 M2S150TS-1FCS536I M2S150TS-1FCSG536 M2S150TS-1FCSG536I M2S150TS-1FCV484 M2S150TS-1FCV484I M2S150TS-1FCV484M M2S150TS-1FCVG484 M2S150TS-1FCVG484I M2S150TS-DIELOTW M2S150TS-FC1152 M2S150TS-FC1152I M2S150TS-FC1152X416 M2S150TS-FCG1152 M2S150TS-FCG1152H0012 M2S150TS-FCG1152H0138 M2S150TS-FCG1152I M2S150TS-FCG1152X416 M2S150TS-FCS536 M2S150TS-FCS536I M2S150TS-FCSG536 M2S150TS-FCSG536I M2S150TS-FCSG536X416 M2S150TS-FCV484 M2S150TS-FCV484I M2S150TS-FCVG484 M2S150TS-FCVG484I M2GL090-1FCS325 M2GL090-1FCS325I

M2GL090-1FCSG325 M2GL090-1FCSG325I M2GL090-1FG484 M2GL090-1FG484I M2GL090-1FG484IX417 M2GL090-1FG676 M2GL090-1FG676I M2S090TS-1FGG676H0280 M2S090TS-1FGG676H0374 M2S090TS-1FGG676I M2S090TS-1FGG676IX418 M2S090TS-1FGG676T2 M2S090TS-1FGG676X416 M2S090TS-DIELOTW M2S090TS-FCS325 M2S090TS-FCS325I M2S090TS-FCS325IX416 M2S090TS-FCS325IX417 M2S090TS-FCSG325 M2S090TS-FCSG325I M2S090TS-FCSG325IX418 M2S090TS-FG484 M2S090TS-FG484I M2S090TS-FG484IX416 M2S090TS-FG484IX456 M2S090TS-FG484X416 M2S090TS-FG676 M2S090TS-FG676I M2S090TS-FGG484 M2S090TS-FGG484I M2S090TS-FGG484IH0365 M2S090TS-FGG484IH0382 M2S090TS-FGG484IX416 M2S090TS-FGG484IX418 M2S090TS-FGG484X416 M2S090TS-FGG676 M2S090TS-FGG676H0137 M2S090TS-FGG676H0309 M2S090TS-FGG676H0376 M2S090TS-FGG676H0379 M2S090TS-FGG676I M2S090TS-FGG676IH0053 M2S090TS-FGG676IH0076 M2S090TS-FGG676IH0107 M2S090TS-FGG676IH0122 M2S090TS-FGG676IH0145 M2S090TS-FGG676IH0231 M2S090TS-FGG676IH0258 M2S090TS-FGG676IH0275

M2S090TS-FGG676IH0279 M2S090TS-FGG676IH0334 M2S090TS-FGG676IH0370 M2S090TS-FGG676IS0004 M2S090TS-FGG676IX416 M2S090TS-FGG676X416 M2S150-1FC1152 M2S150-1FC1152I M2S150-1FCG1152 M2S150-1FCG1152I M2S150-1FCS536 M2S150-1FCS536I M2GL090T-1FG676I M2GL090T-1FGG484 M2GL090T-1FGG484I M2GL090T-1FGG484M M2GL090T-1FGG676 M2S090-FGG676X425 M2S090T-1FCS325 M2S090T-1FCS325I M2S090T-1FCSG325 M2S090T-1FCSG325I M2S090T-1FCSG325Q183 M2S090T-1FG484 M2S090T-1FG484I M2S090T-1FG484IX399 M2S090T-1FG484IX416 M2S090T-1FG484IX538 M2S090T-1FG484M M2S090T-1FG676 M2S090T-1FG676I M2S090T-1FGG484 M2S090T-1FGG484I M2S090T-1FGG484IX417 M2S090T-1FGG484IX418 M2S090T-1FGG484IX538 M2S090T-1FGG484M M2S090T-1FGG484MX399 M2S090T-1FGG484MX416 M2S090T-1FGG484MX417 M2S090T-1FGG484X538 M2S090T-1FGG676 M2S090T-1FGG676H0316 M2S090T-1FGG676I M2S090T-1FGG676Q149 M2S090T-1FGG676Q326 M2S090T-1FGG676Q353 M2S090T-1FGG676Q355 M2S090T-1FGG676S0001

M2S090T-1FGG676S0002 M2S090T-1FGG676S0003 M2S090T-1FGG676S0006 M2S090T-1FGG676S0007 M2S090T-1FGG676S0012 M2S090T-1FGG676S0016 M2GL090T-FCSG325 M2GL090T-FCSG325I M2GL090T-FG484 M2GL090T-FG484I M2GL090T-FG676 M2GL090T-FG676I M2GL090T-FGG484 M2GL090T-FGG484I M2GL090T-FGG484IX416 M2GL090T-FGG676 M2GL090T-FGG676I M2GL090T-FGG676IX416 M2GL090TS-1FCS325 M2GL090TS-1FCS325I M2GL090TS-1FCSG325 M2GL090TS-1FCSG325I M2GL090TS-1FG484 M2GL090TS-1FG484I M2GL090TS-1FG484M M2GL090TS-1FG676 M2GL090TS-1FG676I M2GL090TS-1FGG484 M2GL090TS-1FGG484I M2GL090TS-1FGG484IX416 M2GL090TS-1FGG484M M2GL090TS-1FGG484T2 M2GL090TS-1FGG676 M2GL090TS-1FGG676I M2GL090TS-1FGG676T2 M2GL090TS-FCS325 M2GL090TS-FCS325I M2GL090TS-FCSG325 M2GL090TS-FCSG325I M2GL090TS-FG484 M2GL090TS-FG484I M2GL090TS-FG676 M2GL090TS-FG676I M2GL090TS-FGG484 M2GL090TS-FGG484I M2GL090TS-FGG676 M2GL090TS-FGG676I M2GL150-1FC1152 M2GL150-1FC1152I

M2GL150-1FC1152IX259 M2GL150-1FC1152IX441 M2GL150-1FC1152IX520 M2GL150-1FCG1152 M2GL150-1FCG1152I M2GL150-1FCG1152IX417 M2GL150-1FCG1152IX538 M2GL150-1FCG1152X417 M2GL150-1FCS536 M2GL150-1FCS536I M2GL150-1FCSG536 M2GL150-1FCSG536I M2GL150-1FCV484 M2GL150-1FCV484I M2GL150-1FCVG484 M2GL150-1FCVG484I M2GL150-FC1152 M2GL150-FC1152I M2GL150-FC1152X417 M2GL150-FCG1152 M2GL150-FCG1152I M2GL150-FCS536 M2GL150-FCS536I M2GL150-FCS536IX3 M2GL150-FCSG536 M2GL150-FCSG536I M2GL150-FCV484 M2GL150-FCV484I M2GL150-FCVG484 M2GL150-FCVG484I M2GL150-FCVG484IX475 M2GL150T-1FC1152 M2GL150T-1FC1152I M2GL150T-1FC1152IX417 M2GL150T-1FC1152M M2GL150T-1FC1152MX3 M2GL150T-1FC1152MX441 M2GL150T-1FC1152MX520 M2GL150T-1FCG1152 M2GL150T-1FCG1152I M2GL150T-1FCG1152IX417 M2GL150T-1FCG1152IX538 M2GL150T-1FCG1152M M2GL150T-1FCS536 M2GL150T-1FCS536I M2S090-1FCS325 M2S090-1FCS325I M2S090-1FCSG325 M2S090-1FCSG325I

M2S090-1FG484 M2S090-1FG484I M2S090-1FG484IX6 M2S090-1FG676 M2S090-1FG676I M2S090-1FG676IX417 M2S090-1FGG484 M2S090-1FGG484I M2S090-1FGG484IX418 M2S090-1FGG484X418 M2S090-1FGG676 M2S090-1FGG676I M2S090-1FGG676IX538 M2S090-FCS325 M2S090-FCS325I M2S090-FCS325X339 M2S090-FCSG325 M2S090-FCSG325I M2S090-FG484 M2S090-FG484I M2S090-FG484IX416 M2S090-FG484IX538 M2S090-FG484X416 M2S090-FG484X456 M2S090-FG676 M2S090-FG676I M2S090-FG676IX416 M2S090-FG676X416 M2S090-FGG484 M2S090-FGG484I M2S090-FGG484IX416 M2S090-FGG484IX417 M2S090-FGG484IX418 M2S090-FGG484X416 M2S090-FGG484X417 M2S090-FGG484X418 M2S090-FGG484X456 M2S090-FGG676 M2S090-FGG676I M2S090-FGG676ORT M2S090-FGG676X416 M2GL150TS-FCSG536I M2GL150TS-FCV484 M2GL150TS-FCV484I M2GL150TS-FCVG484 M2S090T-FCS325 M2S090T-FCS325I M2S090T-FCSG325 M2S090T-FCSG325I

M2S090T-FG484 M2S090T-FG484I M2S090T-FG484X538 M2S090T-FG676 M2S090T-FG676I M2S090T-FG676IX417 M2S090T-FGG484 M2S090T-FGG484I M2S090T-FGG484IX417 M2S090T-FGG484IX418 M2S090T-FGG484X416 M2S090T-FGG484X417 M2S090T-FGG676 M2S090T-FGG676I M2S090T-FGG676Q189 M2S090T-FGG676S0006 M2S090T-FGG676S0029 M2S090T-FGG676X416 M2S090TS-1FCS325 M2S090TS-1FCS325I M2S090TS-1FCS325IX417 M2S090TS-1FCS325IX418 M2S090TS-1FCSG325 M2S090TS-1FCSG325I M2S090TS-1FCSG325IX416 M2S090TS-1FCSG325IX418 M2S090TS-1FG484 M2S090TS-1FG484I M2S090TS-1FG484IX3 M2S090TS-1FG484IX416 M2S090TS-1FG484IX418 M2S090TS-1FG484M M2GL150T-1FCSG536 M2GL150T-1FCSG536I M2GL150T-1FCV484 M2GL150T-1FCV484I M2GL150T-1FCV484M M2GL150T-1FCVG484 M2GL150T-1FCVG484I M2GL150T-FC1152 M2GL150T-FC1152I M2GL150T-FCG1152 M2GL150T-FCG1152I M2GL150T-FCG1152IX417 M2GL150T-FCS536 M2GL150T-FCS536I M2GL150T-FCSG536 M2GL150T-FCSG536I M2GL150T-FCV484

M2GL150T-FCV484I M2GL150T-FCVG484 M2GL150T-FCVG484I M2GL150TS-1FC1152 M2GL150TS-1FC1152I M2GL150TS-1FC1152M M2GL150TS-1FCG1152 M2GL150TS-1FCG1152I M2GL150TS-1FCG1152M M2GL150TS-1FCS536 M2GL150TS-1FCS536I M2GL150TS-1FCSG536 M2GL150TS-1FCSG536I M2GL150TS-1FCV484 M2GL150TS-1FCV484I M2GL150TS-1FCV484M M2GL150TS-1FCVG484 M2GL150TS-1FCVG484I M2GL150TS-1FCVG484IX323 M2GL150TS-FC1152 M2GL150TS-FC1152I M2GL150TS-FCG1152 M2GL150TS-FCG1152I M2GL150TS-FCS536 M2GL150TS-FCS536I M2GL150TS-FCSG536 M2GL090T-1FGG676I M2GL090T-1FGG676IX418 M2GL090T-FCS325 M2GL090T-FCS325I M2GL090-1FG676IX259 M2GL090-1FG676IX417 M2GL090-1FG676IX441 M2GL090-1FGG484 M2GL090-1FGG484I M2GL090-1FGG484IX417 M2GL090-1FGG484T1 M2GL090-1FGG676 M2GL090-1FGG676I M2GL090-1FGG676IX259 M2GL090-1FGG676IX417 M2GL090-1FGG676IX441 M2GL090-FCS325 M2GL090-FCS325I M2GL090-FCSG325 M2GL090-FCSG325I M2GL090-FG484 M2GL090-FG484I M2GL090-FG484IX3

M2GL090-FG484IX417 M2GL090-FG484X416 M2GL090-FG484X456 M2GL090-FG676 M2GL090-FG676I M2GL090-FG676X416 M2GL090-FGG484 M2GL090-FGG484I M2GL090-FGG484IX417 M2GL090-FGG484IX418 M2GL090-FGG484X416 M2GL090-FGG484X418 M2GL090-FGG484X456 M2GL090-FGG484X505 M2GL090-FGG676 M2GL090-FGG676I M2GL090-FGG676X416 M2GL090-FGG676X456 M2GL090T-1FCS325 M2GL090T-1FCS325I M2GL090T-1FCSG325 M2GL090T-1FCSG325I M2GL090T-1FG484 M2GL090T-1FG484I M2GL090T-1FG484IX417 M2GL090T-1FG484M M2GL090T-1FG484MX418 M2GL090T-1FG484MX6 M2GL090T-1FG676 M2S150-1FCSG536 M2S150-1FCSG536I M2S150-1FCV484

# SmartFusion 2 Microcontroller Subsystem

## Introduction

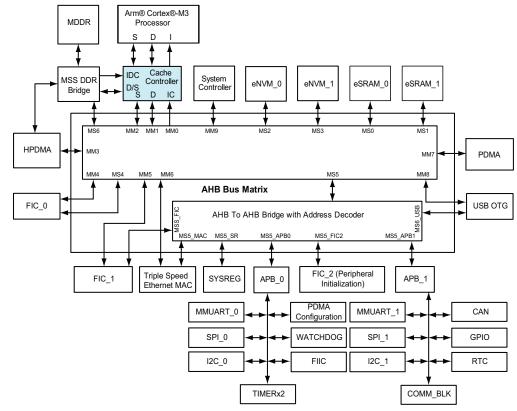

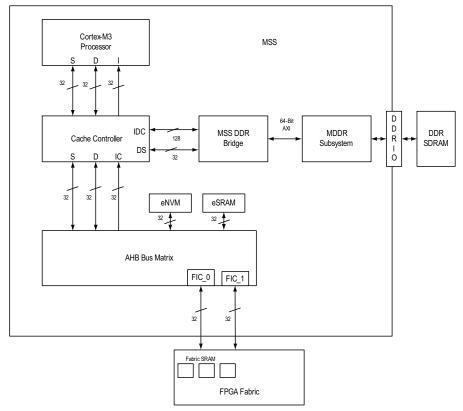

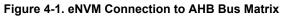

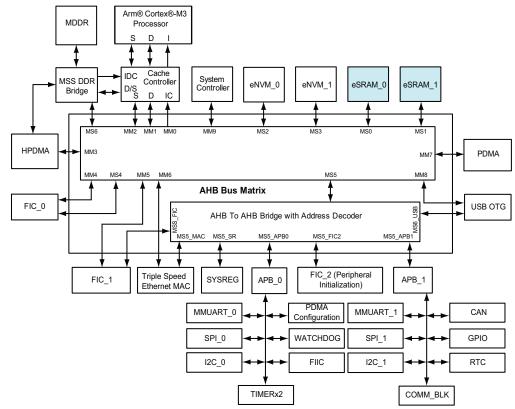

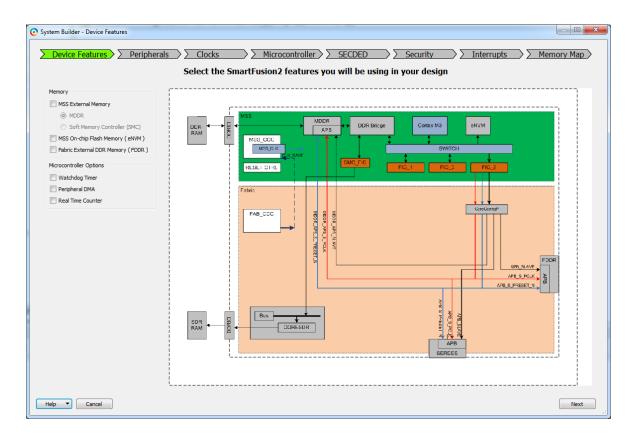

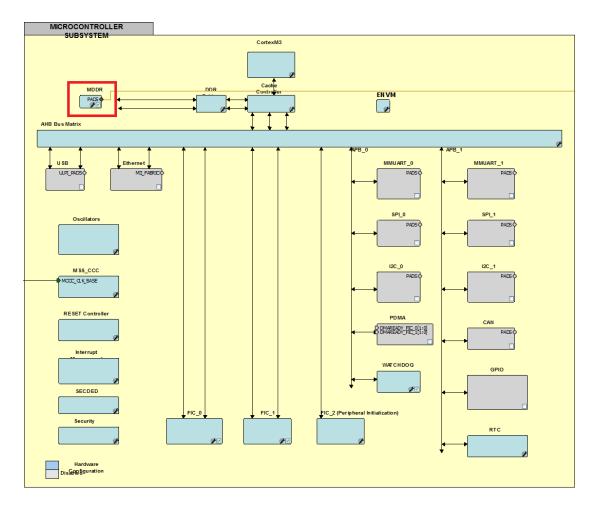

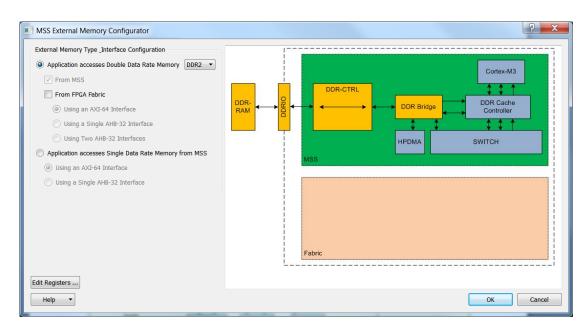

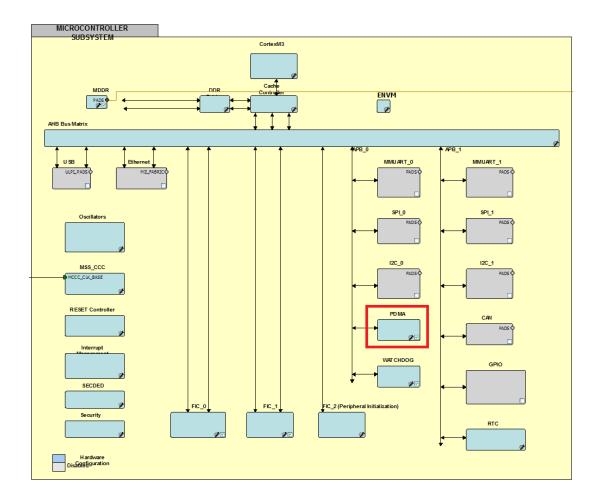

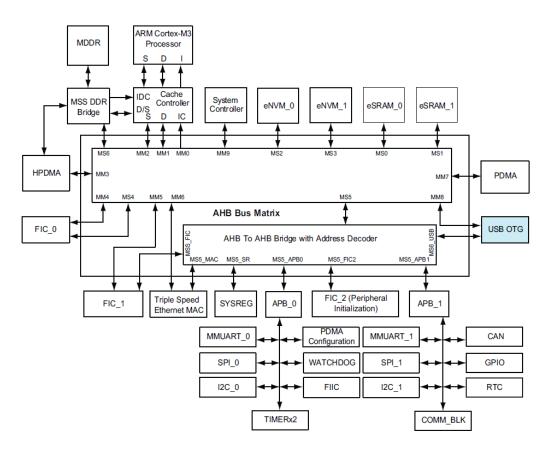

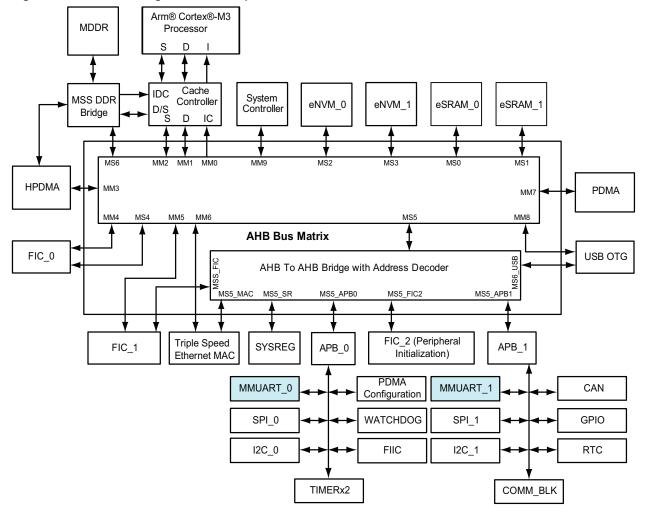

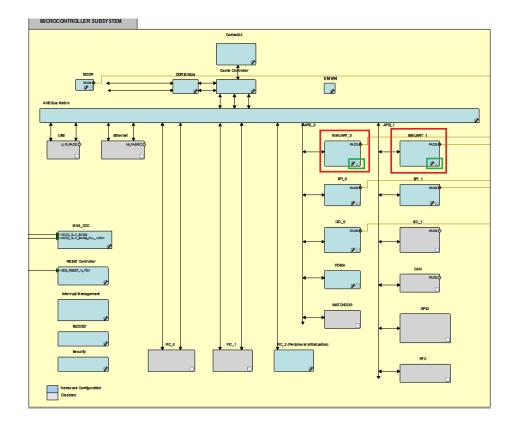

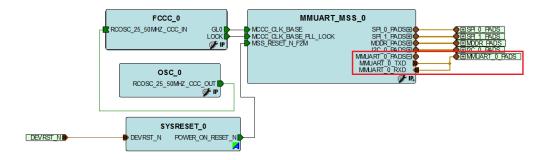

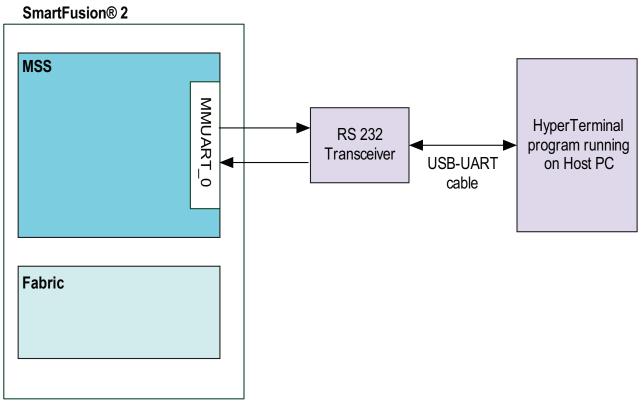

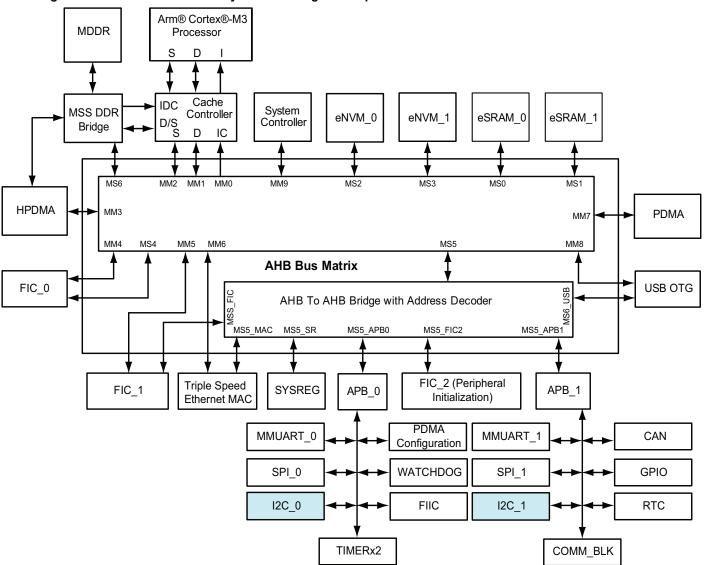

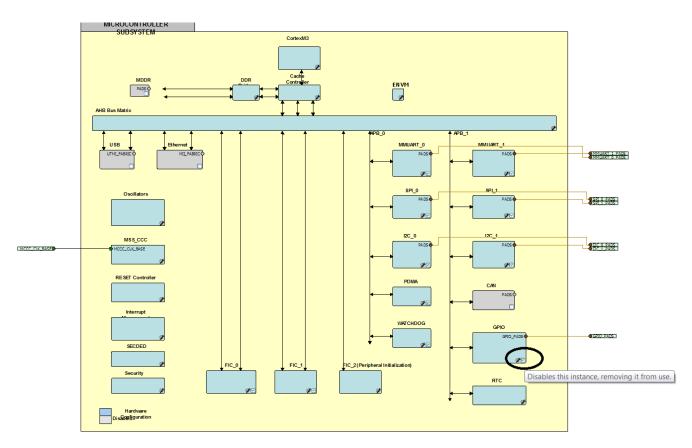

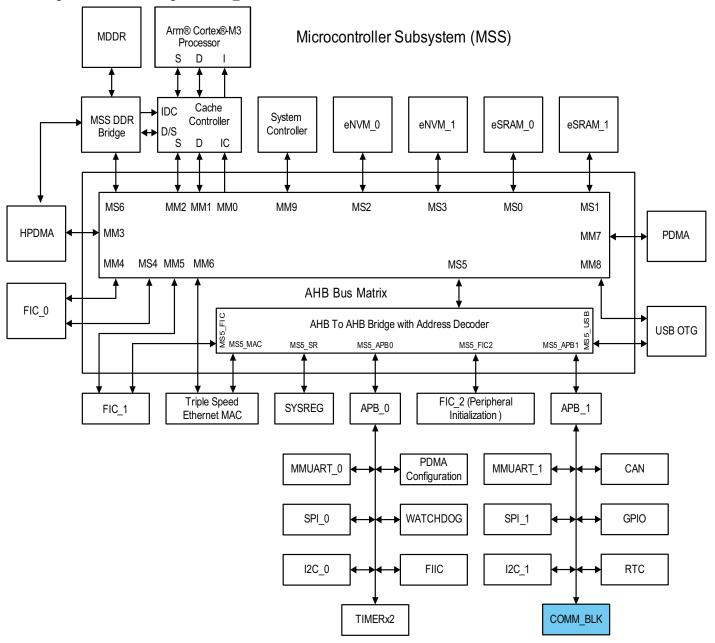

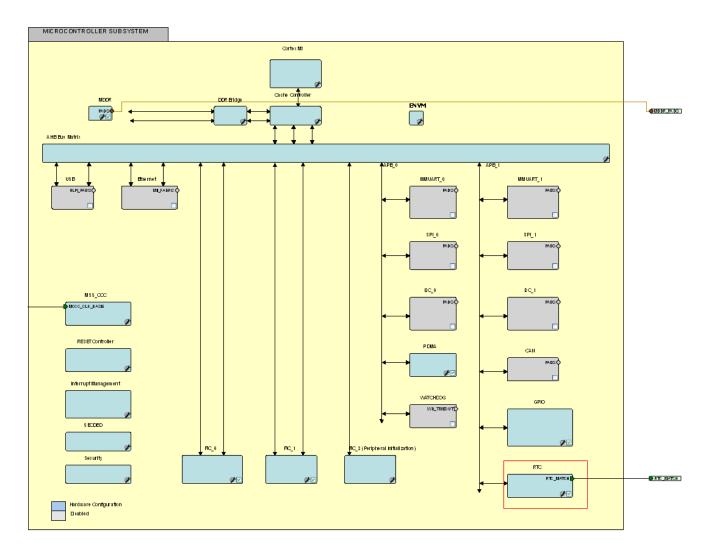

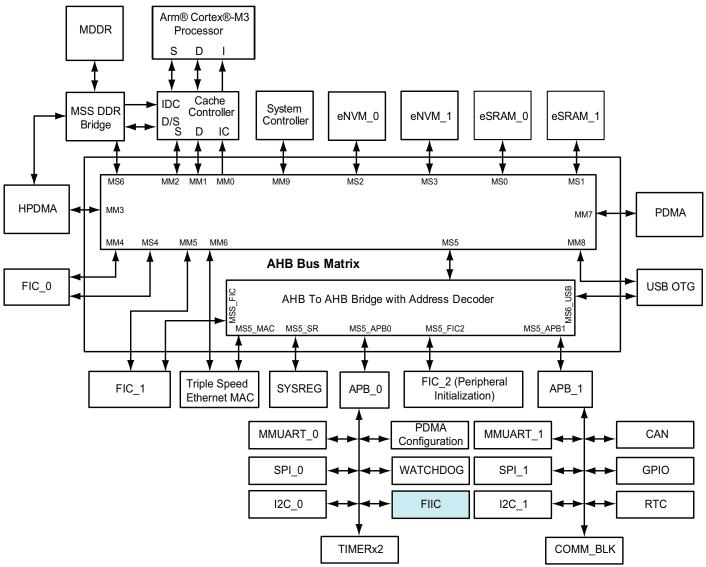

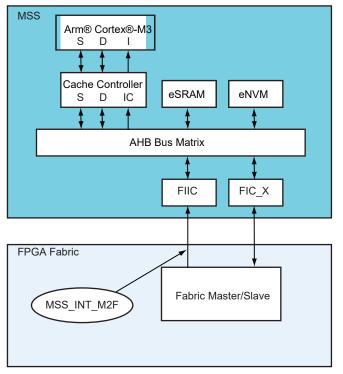

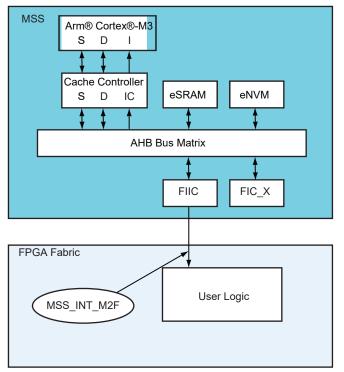

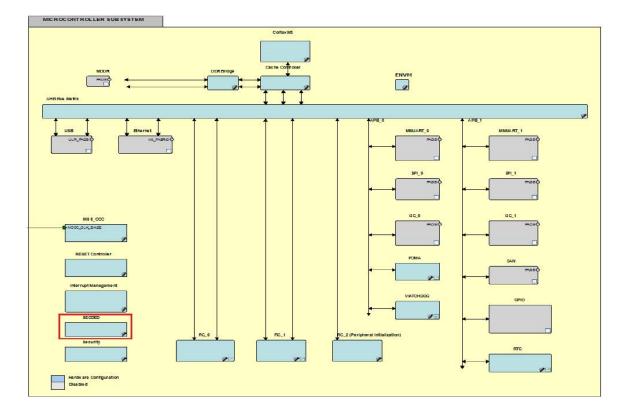

This user guide describes the SmartFusion<sup>®</sup> 2 system-on-chip (SoC) field programmable gate array (FPGA) devices hard peripheral interfaces and the Arm<sup>®</sup> Cortex<sup>®</sup>-M3 processor which are together called as Microcontroller Subsystem (MSS) and their use models.

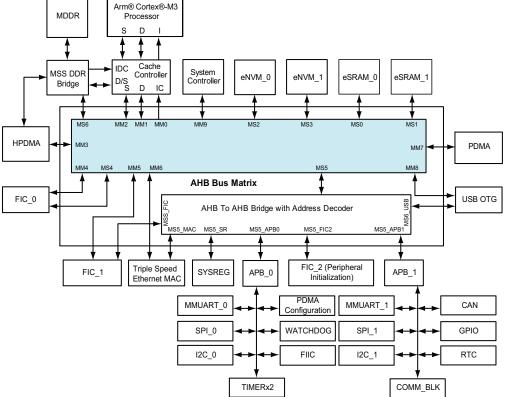

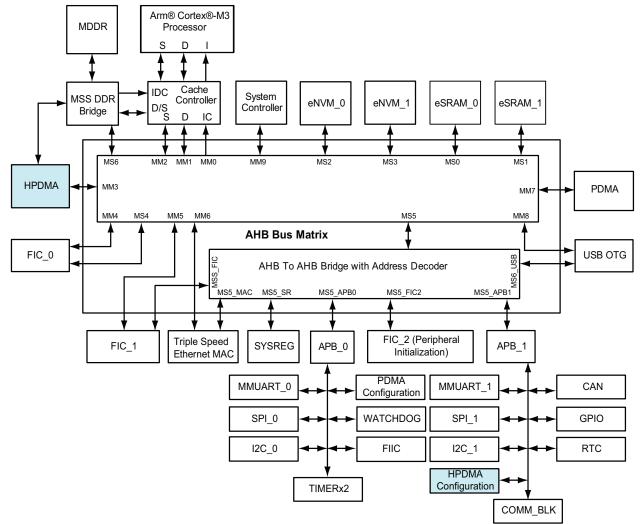

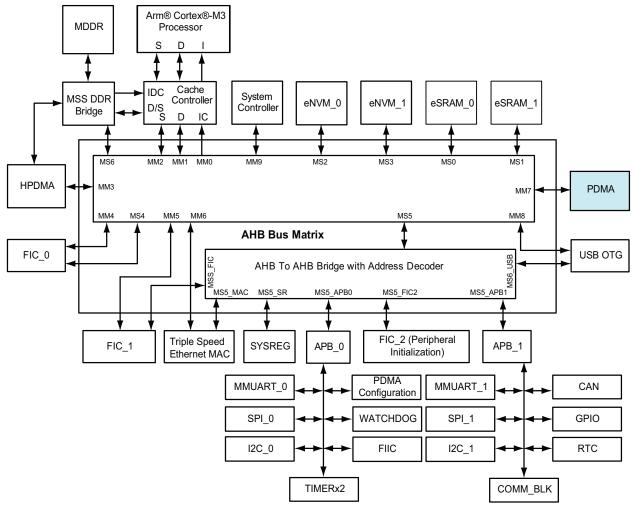

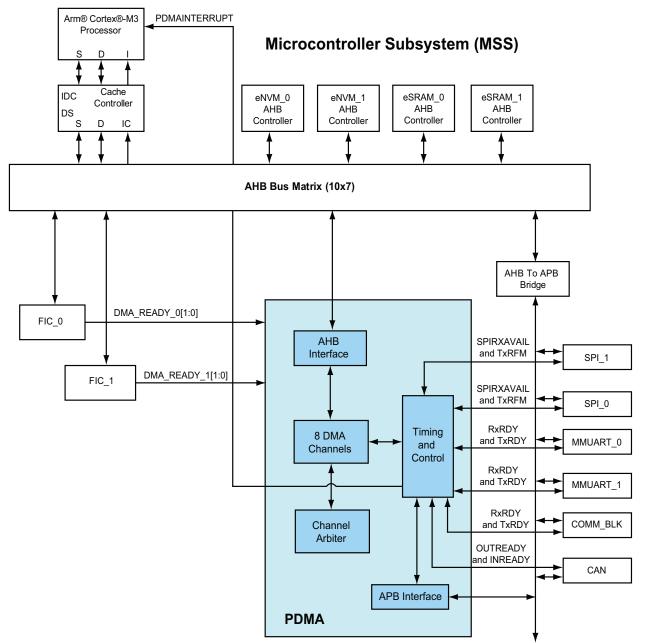

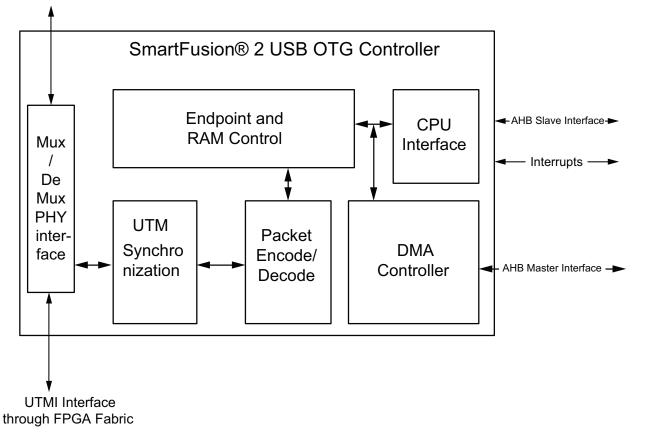

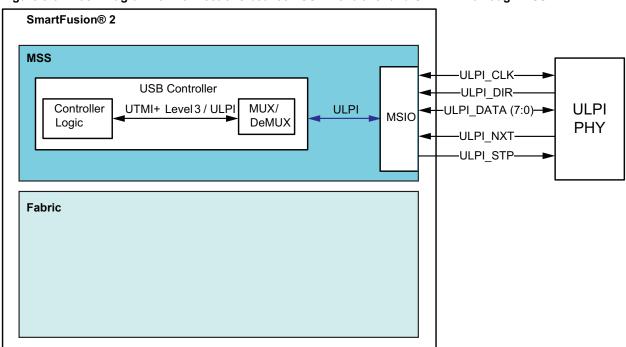

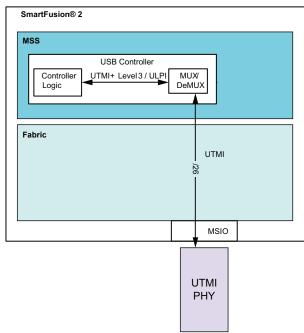

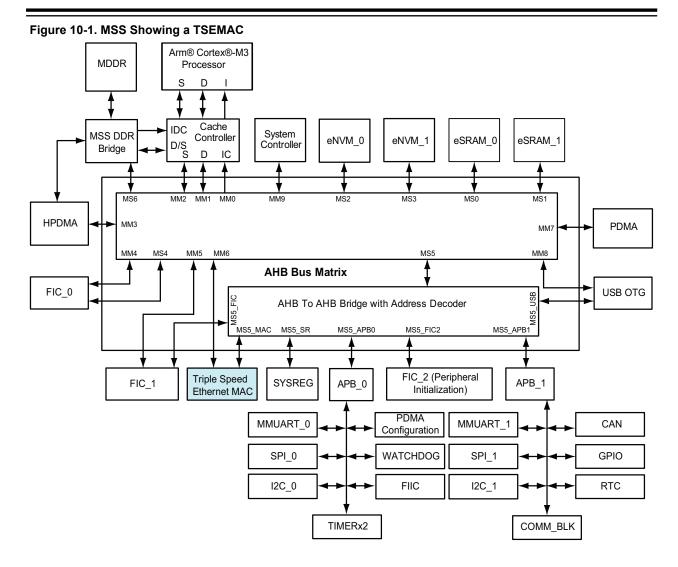

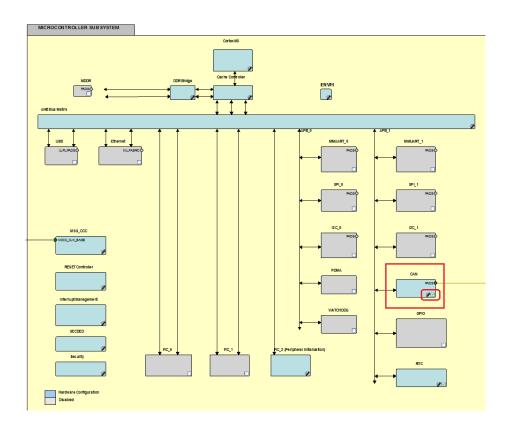

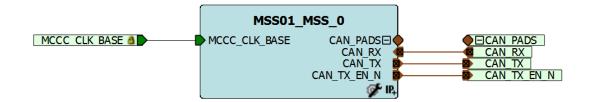

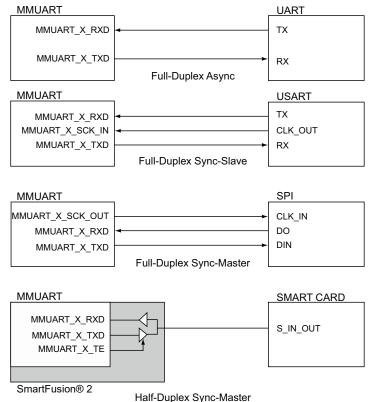

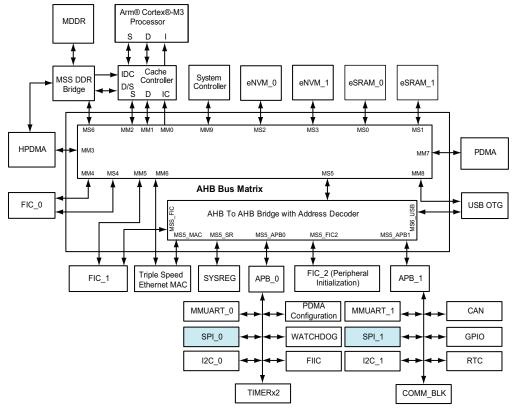

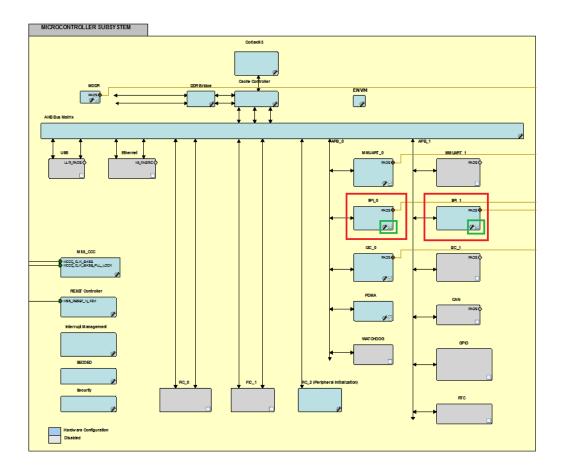

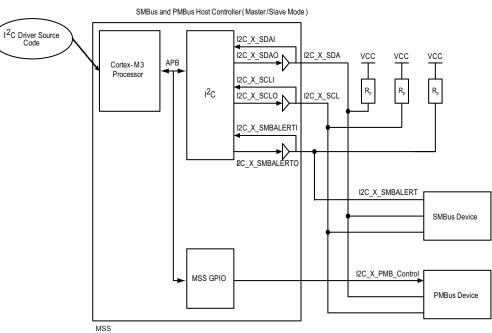

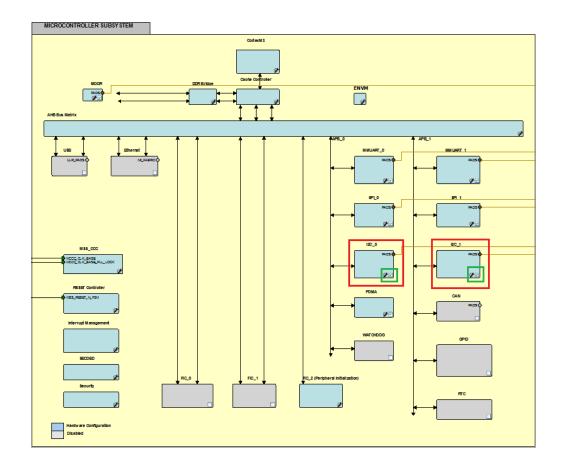

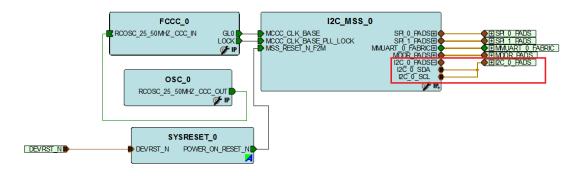

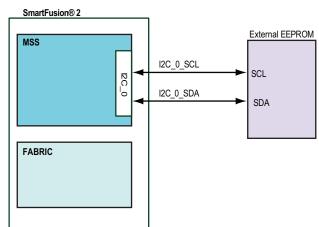

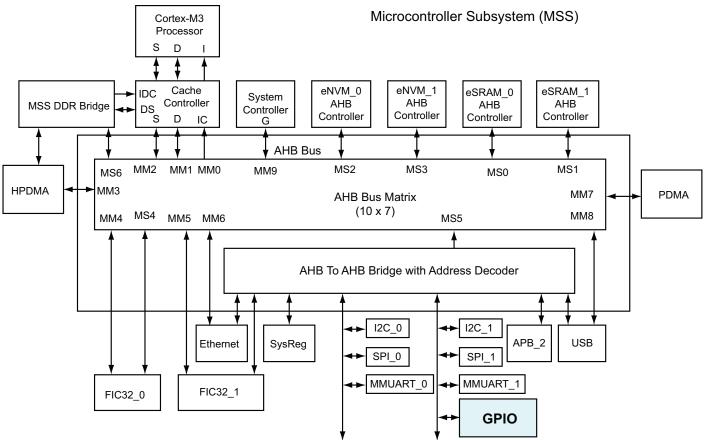

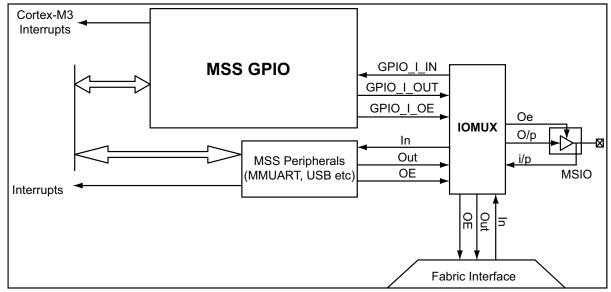

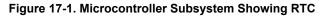

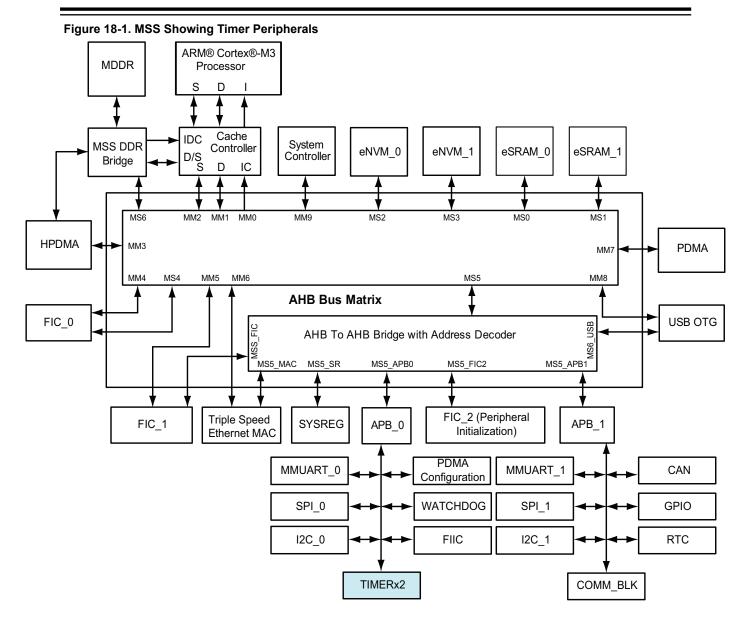

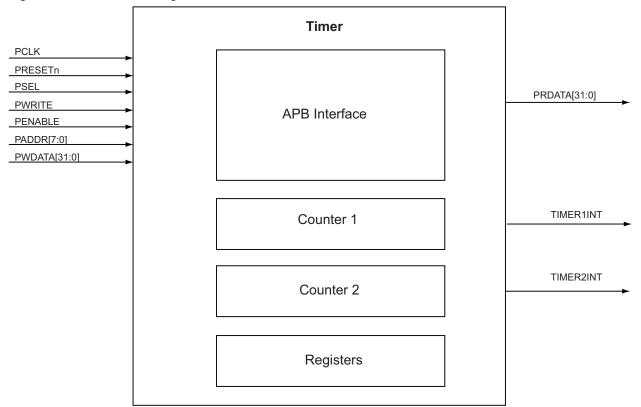

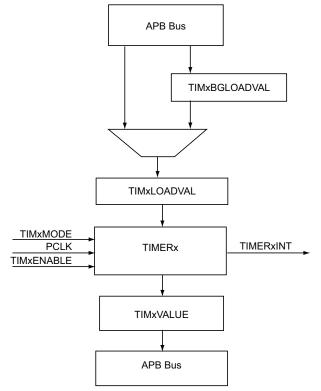

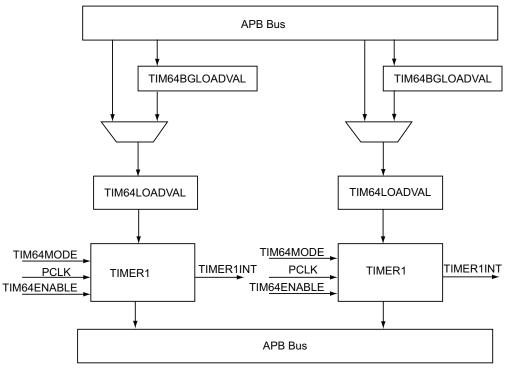

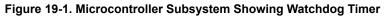

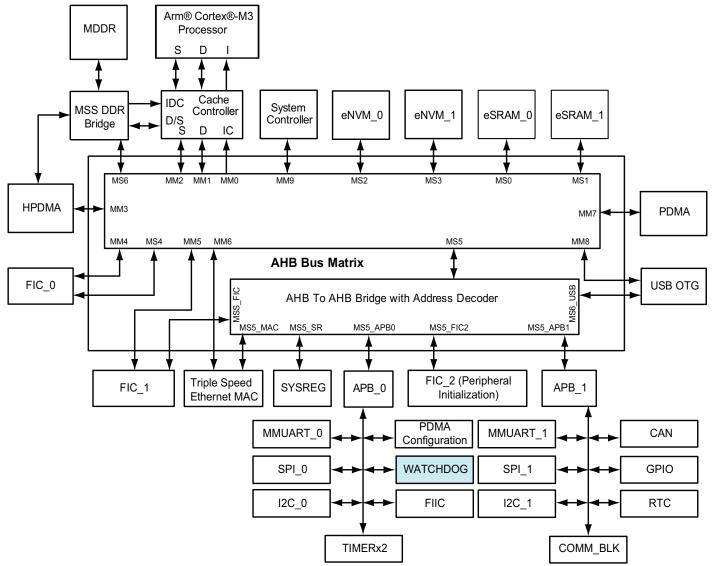

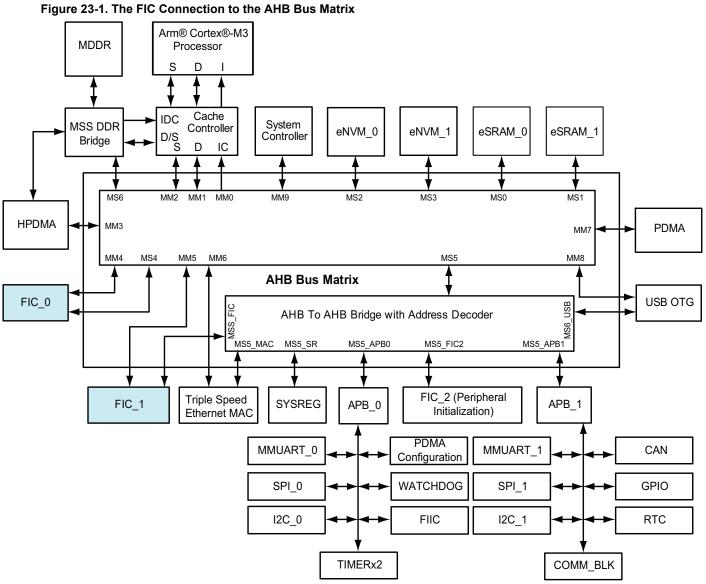

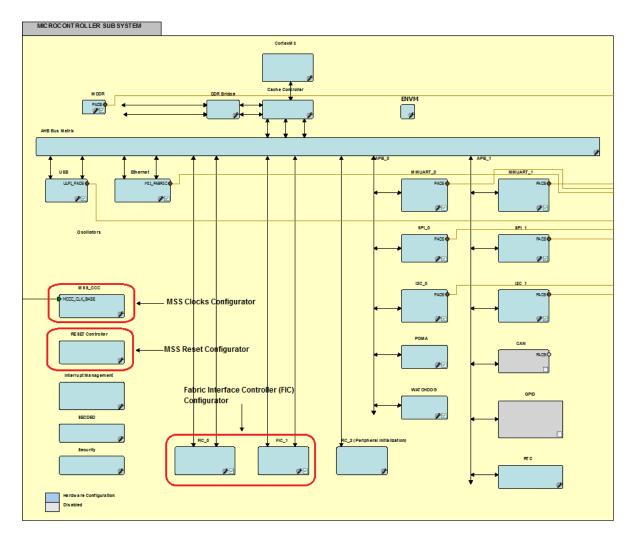

The MSS includes Cortex-M3 processor, cache controller, embedded NVM (eNVM), embedded SRAM (eSRAM), AHB bus matrix, high performance DMA (HPDMA), peripheral DMA (PDMA), Universal Serial Bus On-The-Go (USB OTG) controller, Triple Speed Ethernet MAC (EMAC), CAN controller, multi-mode universal asynchronous/ synchronous receiver/transmitter (MMUART), serial peripheral interface (SPI) controller, inter-integrated circuit controller (I<sup>2</sup>C), MSS general purpose input/output (GPIO), communications block, real-time counter (RTC) system, system timer, watchdog timer, reset controller, system register block, fabric interface interrupt controller (FIIC), fabric interface controller (FIC), and APB configuration interface.

This user guide describes features, functional description, configuration parameters, configuration options through the Libero<sup>®</sup> System-on-Chip (SoC) software and through Firmware, Firmware APIs, use models for the interfaces, links to the useful information/resources like application notes and other relevant documentations.

# **Table of Contents**

| Intr | oductio | on                                                         | 1   |

|------|---------|------------------------------------------------------------|-----|

| 1.   | Corte   | x-M3 Processor Overview and Debug Features                 | 6   |

|      | 1.1.    | Features                                                   | 6   |

|      | 1.2.    | Functional Description                                     | 7   |

|      | 1.3.    | Cortex-M3 Processor NVIC                                   | 7   |

|      | 1.4.    | Cortex-M3 Processor SysTick Timer                          |     |

|      | 1.5.    | Cortex-M3 Processor Debug Subsystem                        |     |

|      | 1.6.    | Cortex-M3 Processor Port Descriptions                      |     |

|      | 1.7.    | How to Use the Cortex-M3 Processor and the Debug Subsystem | 15  |

| 2.   | Corte   | x-M3 Processor (Reference Material)                        | 17  |

|      | 2.1.    | System Level Interface                                     | 18  |

|      | 2.2.    | Integrated Configurable Debug                              |     |

|      | 2.3.    | Cortex-M3 Processor Features and Benefits Summary          | 18  |

|      | 2.4.    | Cortex-M3 Processor Core Peripherals                       |     |

|      | 2.5.    | Cortex-M3 Processor Description                            | 19  |

|      | 2.6.    | Cortex-M3 Processor Instruction Set                        | 42  |

|      | 2.7.    | Cortex-M3 Processor Peripherals                            |     |

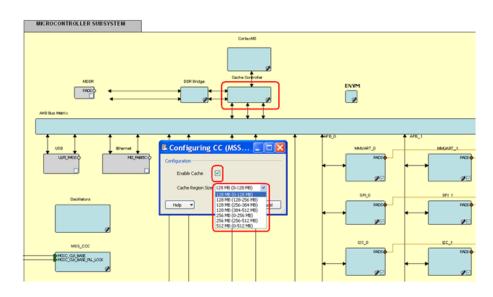

| 3.   | Cach    | e Controller                                               | 122 |

|      | 3.1.    | Features                                                   | 122 |

|      | 3.2.    | Functional Description                                     |     |

|      | 3.3.    | How to Use Cache Controller                                |     |

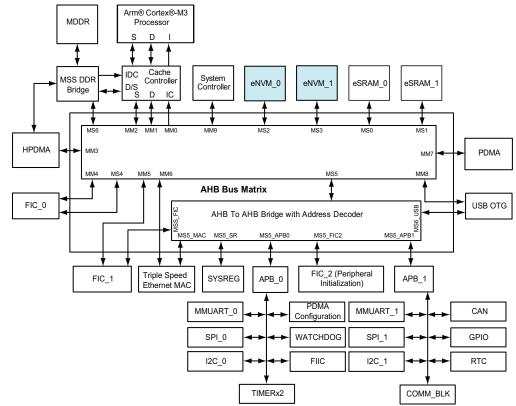

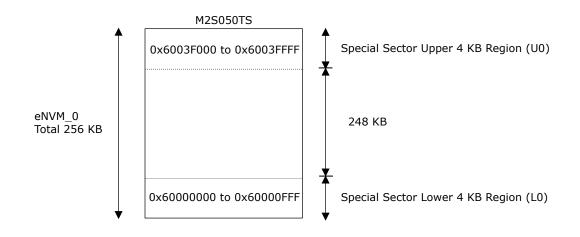

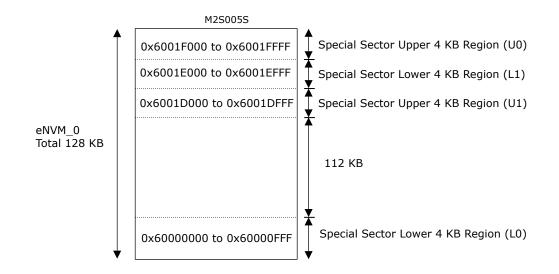

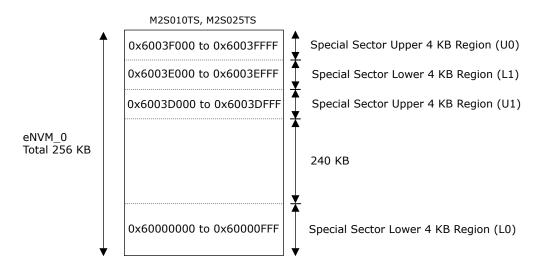

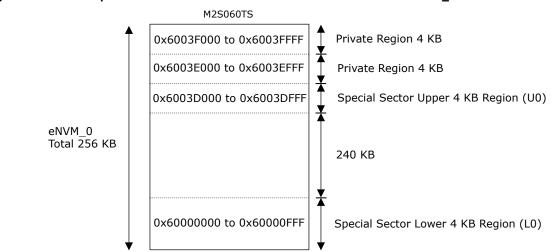

| 4.   | Embe    | edded NVM (eNVM) Controllers                               | 133 |

|      | 4.1.    | Features                                                   | 133 |

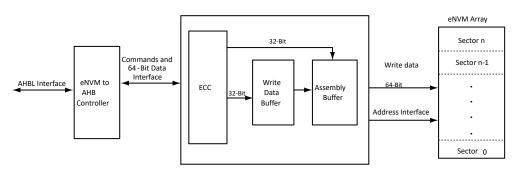

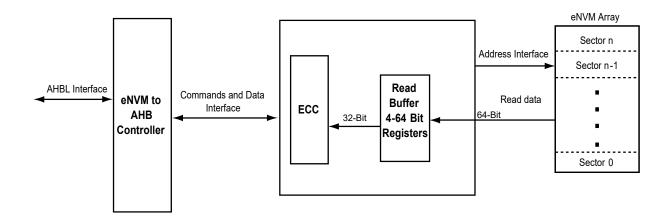

|      | 4.2.    | Functional Description                                     | 133 |

|      | 4.3.    | Security                                                   |     |

|      | 4.4.    | How to Use eNVM                                            |     |

|      | 4.5.    | SYSREG Control Registers                                   | 162 |

|      | 4.6.    | eNVM Control Registers                                     |     |

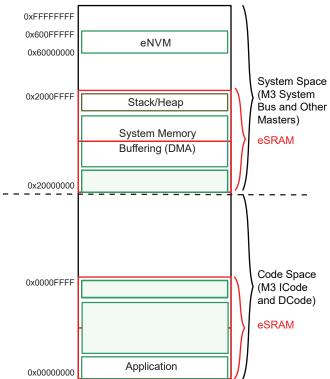

| 5.   | Embe    | edded SRAM (eSRAM) Controllers                             | 174 |

|      | 5.1.    | Features                                                   |     |

|      | 5.2.    | Functional Description                                     | 175 |

|      | 5.3.    | How to Use eSRAM                                           | 179 |

|      | 5.4.    | SYSREG Control Registers                                   | 183 |

| 6.   | AHB     | Bus Matrix                                                 |     |

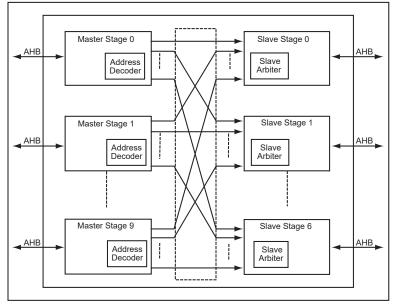

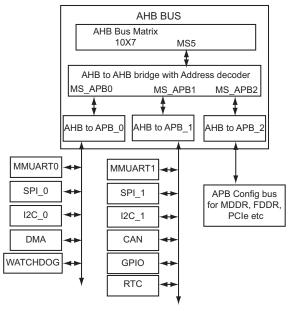

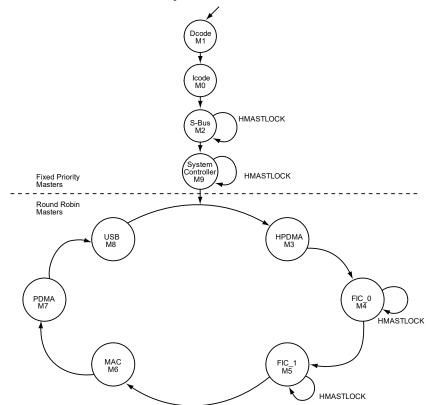

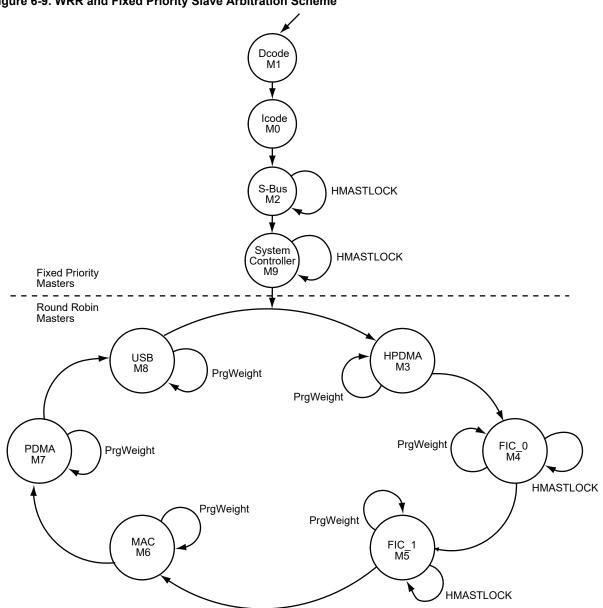

|      | 6.1.    | Functional Description                                     |     |

|      | 6.2.    | How to Use AHB Bus Matrix                                  |     |

|      | 6.3.    | Register Map                                               |     |

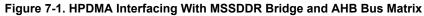

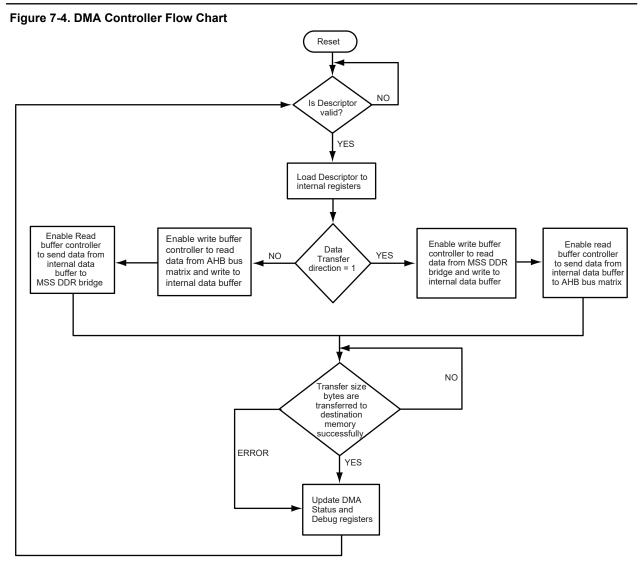

| 7.   | High    | Performance DMA Controller                                 | 220 |

|      | 7.1.    | Features                                                   |     |

|      | 7.2.    | Functional Description                                     |     |

|      |         | -                                                          |     |

|     | 7.3. How      | to Use HPDMA                      | 225  |

|-----|---------------|-----------------------------------|------|

|     | 7.4. HPD      | MA Controller Register Map        | 228  |

|     | 7.5. SYSI     | REG Control Register              | 246  |

| 8.  | Peripheral [  | DMA                               | 248  |

| -   | •             | ures                              |      |

|     |               | ctional Description               |      |

|     |               | to Use the PDMA                   |      |

|     |               | IA Register Map                   |      |

|     |               | REG Control Registers             |      |

| 9.  | Universal S   | Serial Bus On-The-Go Controller   | 269  |

|     | 9.1. Feat     | ures                              | 269  |

|     |               | ctional Description               |      |

|     |               | to Use USB OTG Controller         |      |

|     |               |                                   |      |

| 10. |               | AC                                |      |

|     |               | ures                              |      |

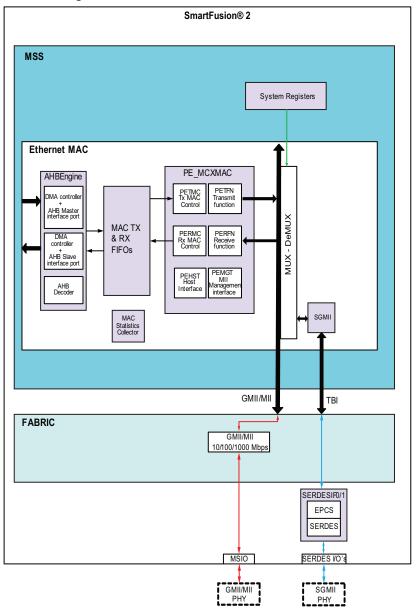

|     |               | ctional Description               |      |

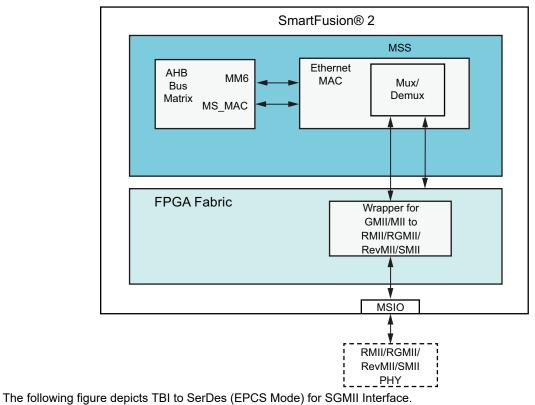

|     |               | MAC PHY Interfaces                |      |

|     |               | AC Operation                      |      |

|     |               | to Use TSEMAC                     |      |

|     |               | REG Control Register for EMAC     |      |

|     |               | AC Configuration Register Summary |      |

|     |               | AC Register Bit Definitions       |      |

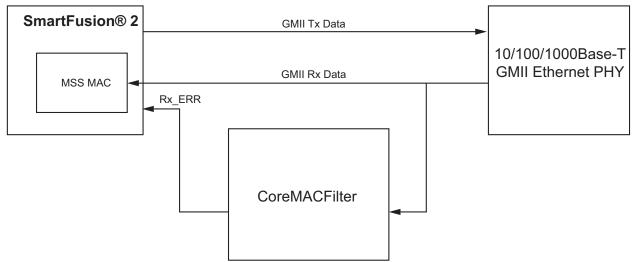

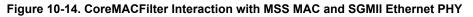

|     | 10.9. Core    | MACFilter Overview                | 421  |

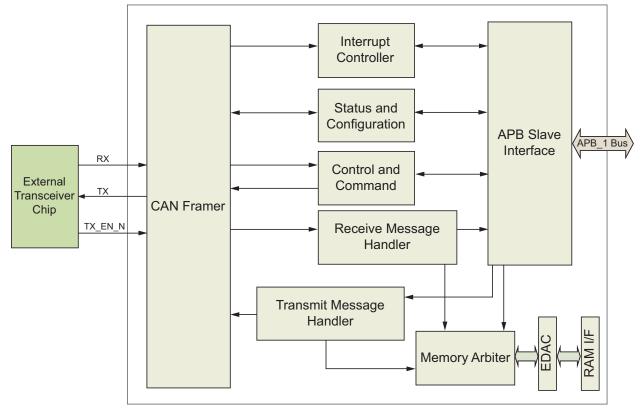

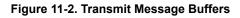

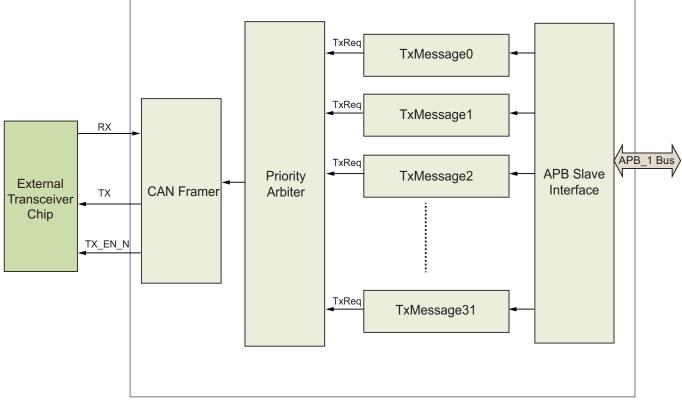

| 11. | CAN Contro    | oller                             | 423  |

|     | 11.1. Feat    | ures                              | 423  |

|     | 11.2. Func    | ctional Description               | 424  |

|     |               | I Controller Configuration        |      |

|     |               | to Use the MSS CAN Controller     |      |

|     |               | Cases                             |      |

|     | 11.6. CAN     | I Controller Register Map         | 437  |

| 12. | MMUART P      | Peripherals                       | 457  |

|     | 12.1. Feat    | ures                              | 457  |

|     | 12.2. Func    | ctional Description               | 458  |

|     | 12.3. How     | to Use MMUART                     | 474  |

|     | 12.4. MMU     | JART Register Map                 | 479  |

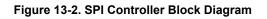

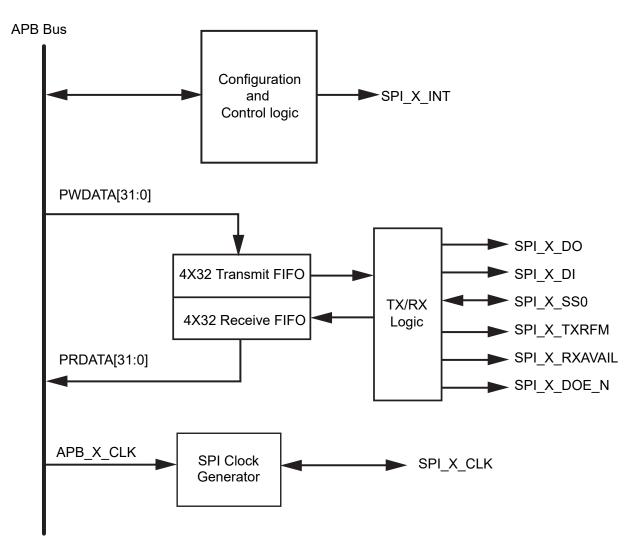

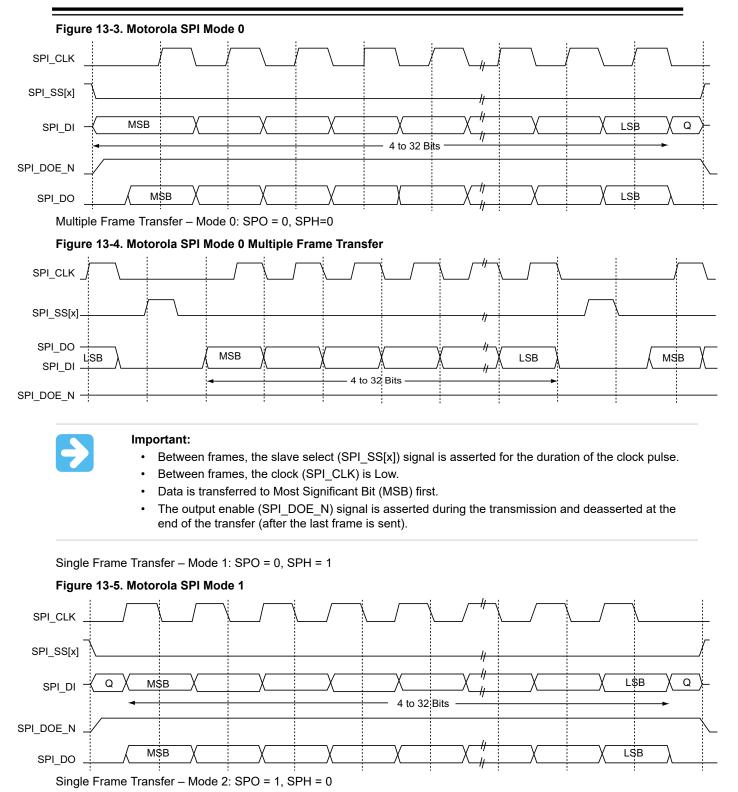

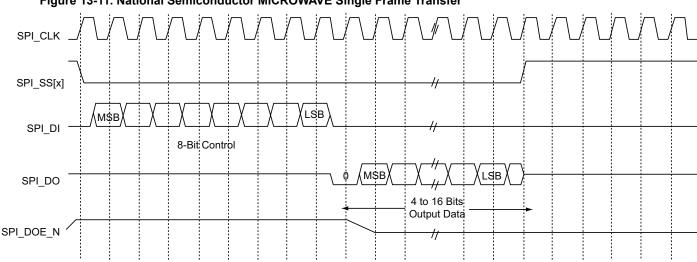

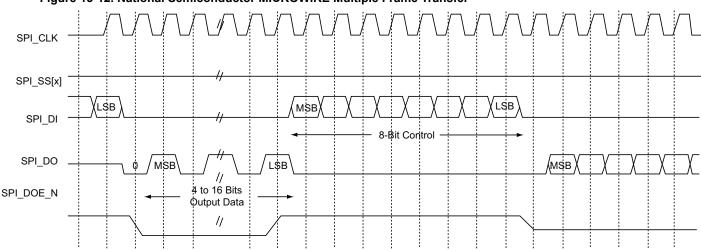

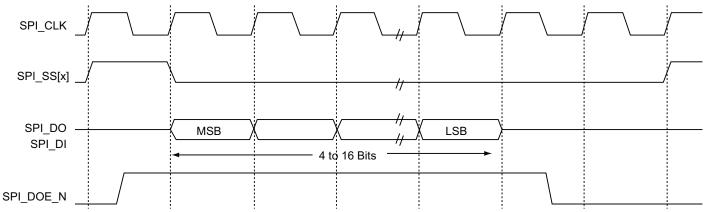

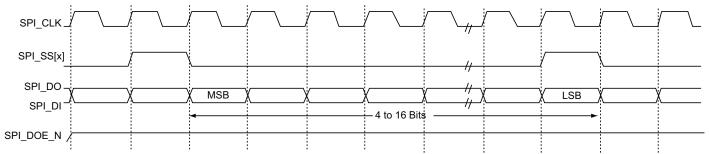

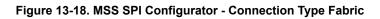

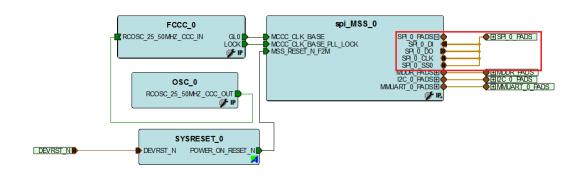

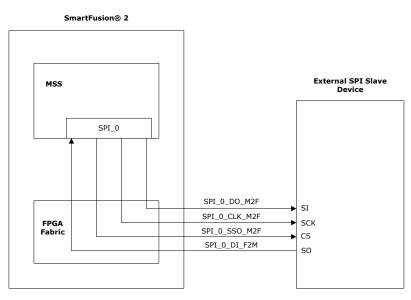

| 13. | Serial Perip  | heral Interface Controller        | 496  |

|     | 13.1. Feat    | ures                              | 496  |

|     | 13.2. Func    | ctional Description               | 496  |

|     |               | to Use SPI                        |      |

|     | 13.4. SPI F   | Register Map                      | 518  |

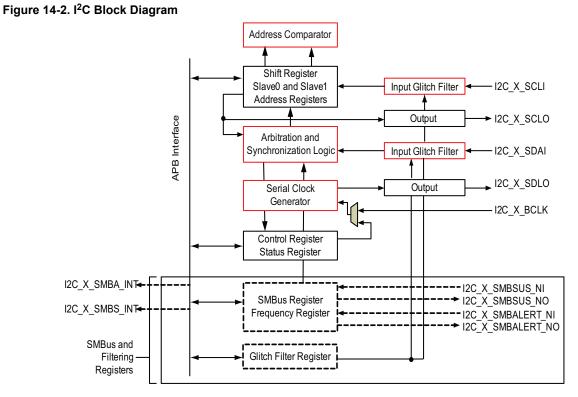

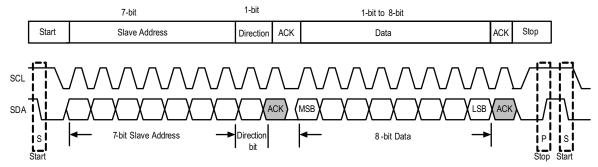

| 14  | Inter-Integra | ated Circuit Peripherals          | 530  |

|     |               | ures                              |      |

|     |               |                                   | 0000 |

|     | 14.2. Functional Description                 | 531 |

|-----|----------------------------------------------|-----|

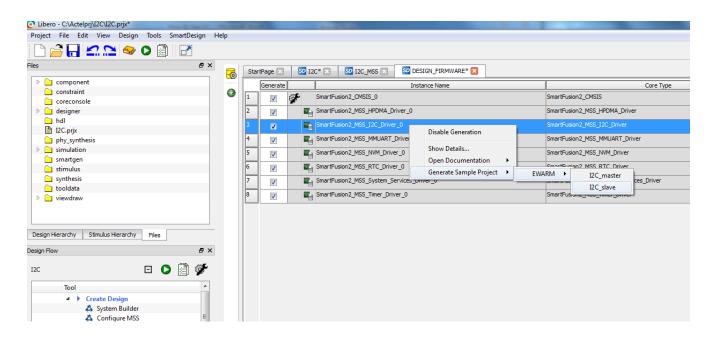

|     | 14.3. How to Use I <sup>2</sup> C            | 536 |

|     | 14.4. I <sup>2</sup> C Register Map          | 542 |

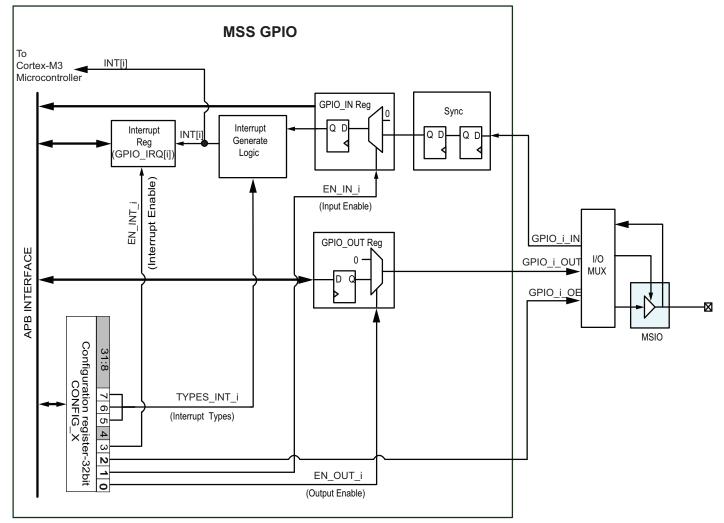

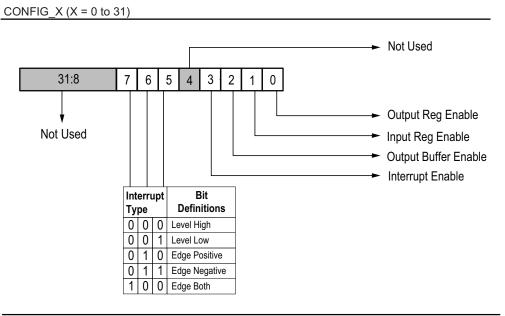

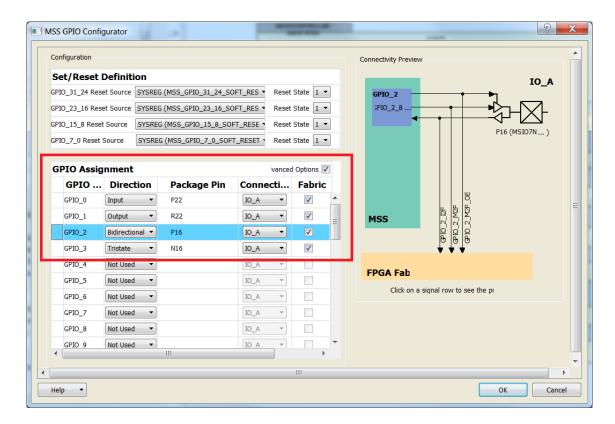

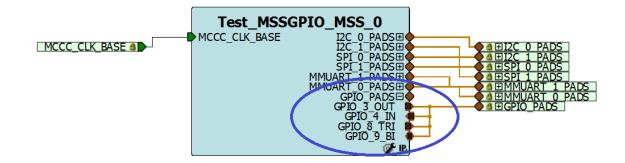

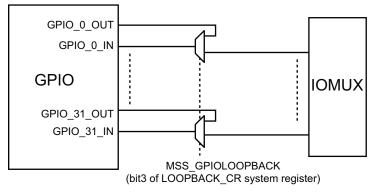

| 15. | MSS GPIO                                     | 555 |

|     | 15.1. Features                               |     |

|     | 15.2. MSS GPIO Functional Description        |     |

|     | 15.3. MSS GPIO Usage                         |     |

|     | 15.4. GPIO Register Map                      |     |

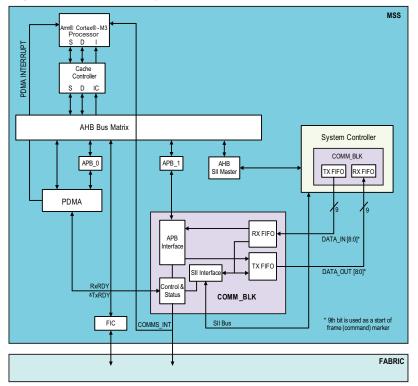

| 16. | Communication Block                          | 583 |

|     | 16.1. Features                               |     |

|     | 16.2. Functional Description                 |     |

|     | 16.3. How to Use the Communication Block     |     |

|     | 16.4. COMM_BLK Configuration Registers       |     |

|     | 16.5. COMM_BLK Register Interface Details    |     |

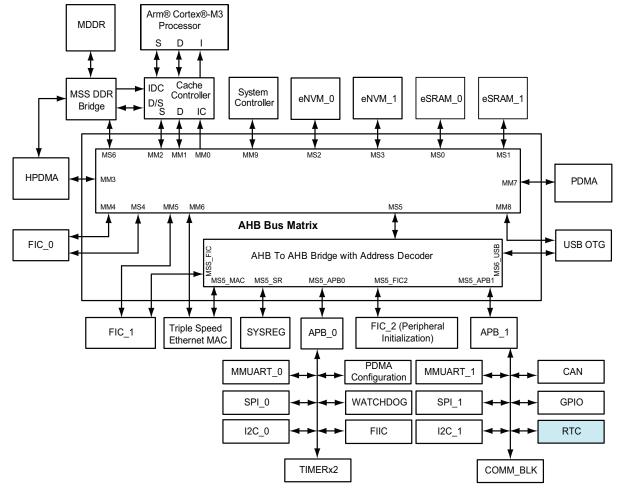

| 17. | RTC System                                   |     |

|     | 17.1. Features                               |     |

|     | 17.2. Functional Description                 |     |

|     | 17.3. How to Use RTC.                        | 595 |

|     | 17.4. RTC Register Map                       |     |

|     | 17.5. SYSREG Control Registers               | 604 |

| 18. | System Timer                                 |     |

|     | 18.1. Features                               |     |

|     | 18.2. Functional Description                 |     |

|     | 18.3. How to Use Timer                       |     |

|     | 18.4. Timer Register Map                     |     |

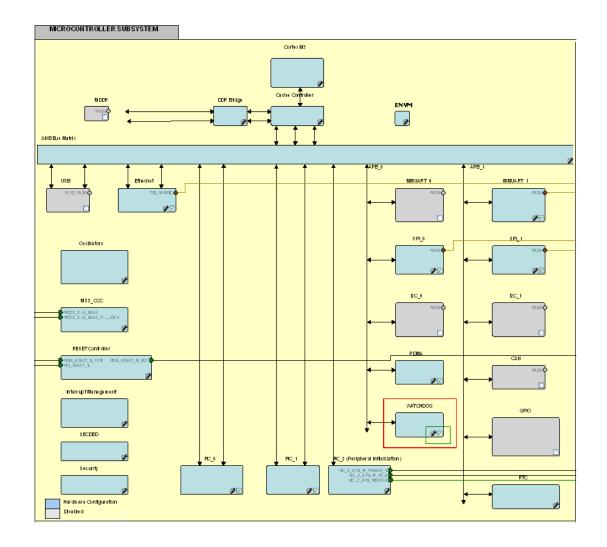

| 19. | Watchdog Timer                               |     |

|     | 19.1. Features                               |     |

|     | 19.2. Functional Description                 |     |

|     | 19.3. How to Use the Watchdog Timer          |     |

|     | 19.4. Watchdog Timer Register Map            |     |

|     | 19.5. SYSREG Control Registers               |     |

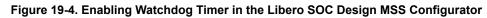

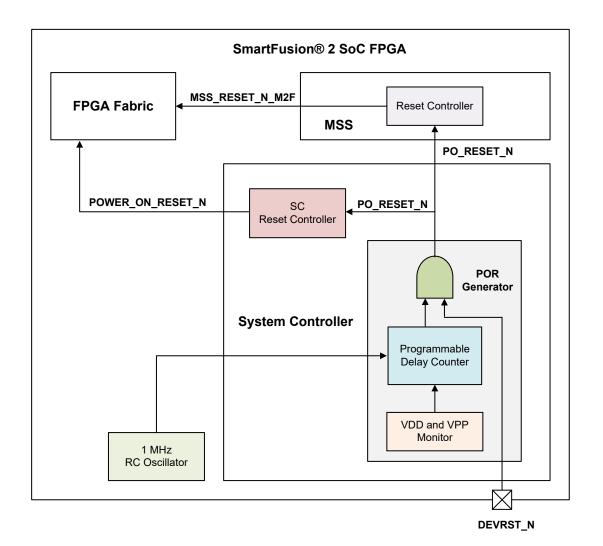

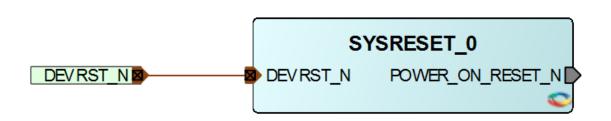

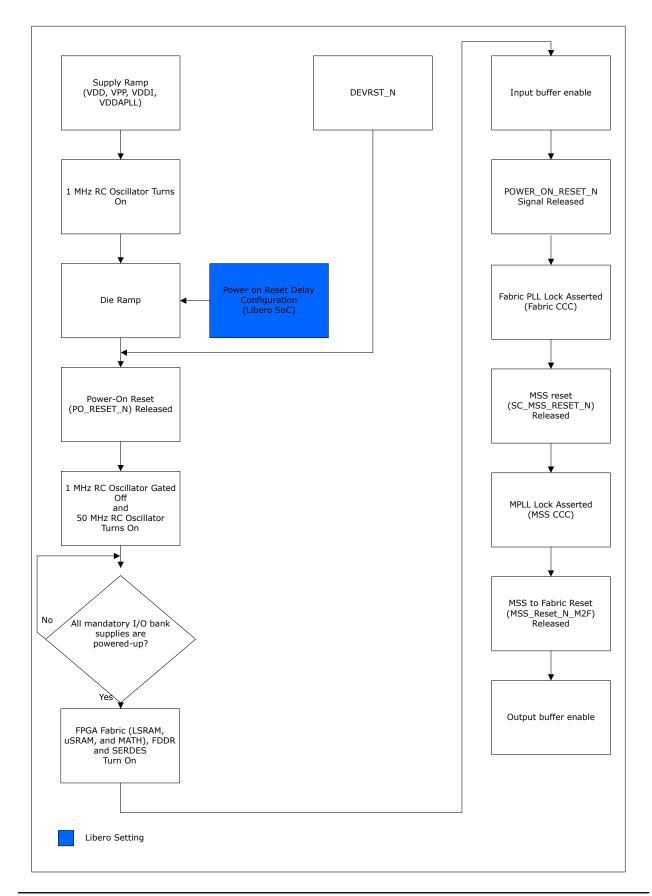

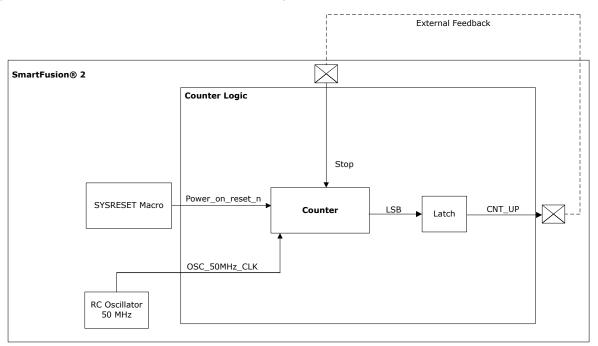

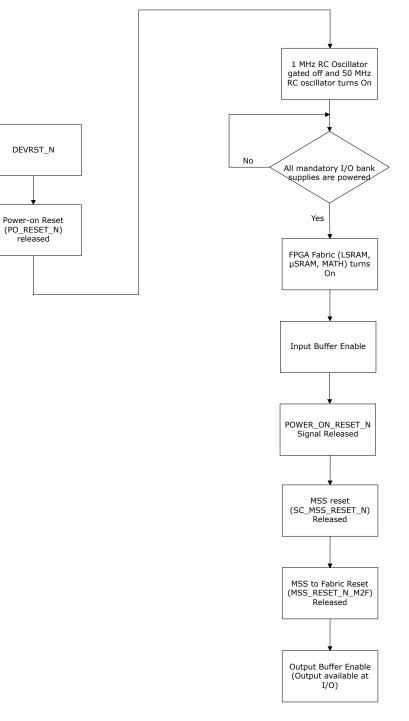

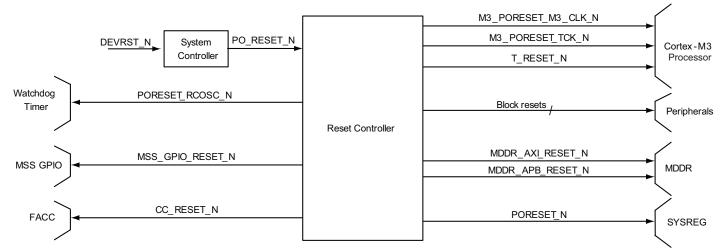

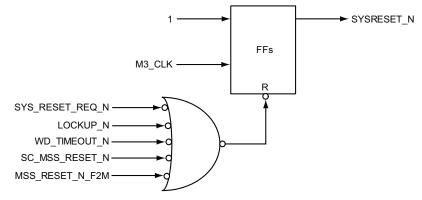

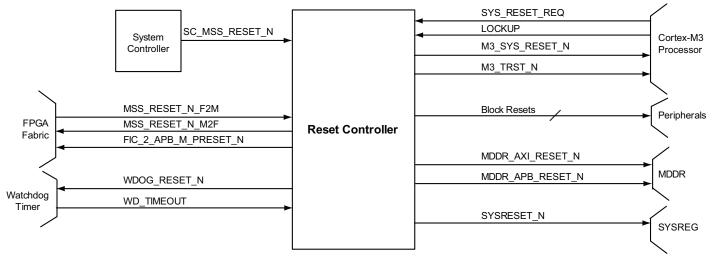

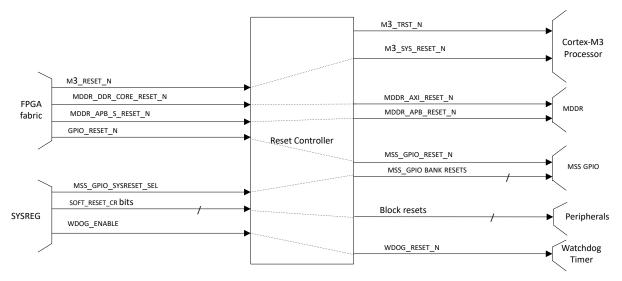

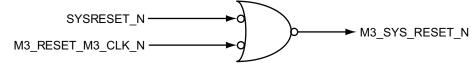

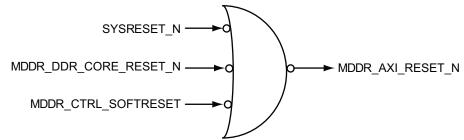

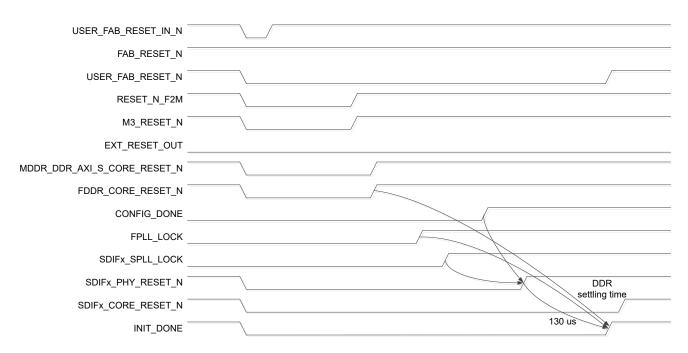

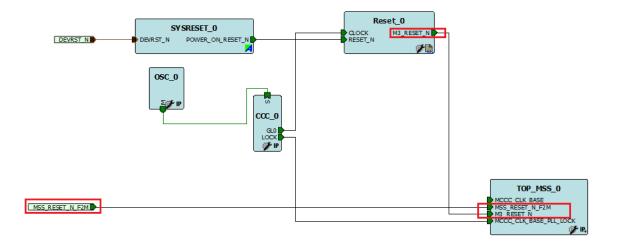

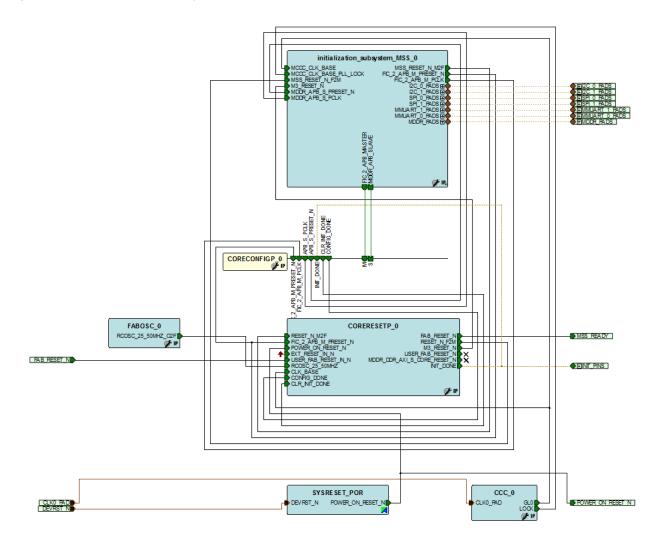

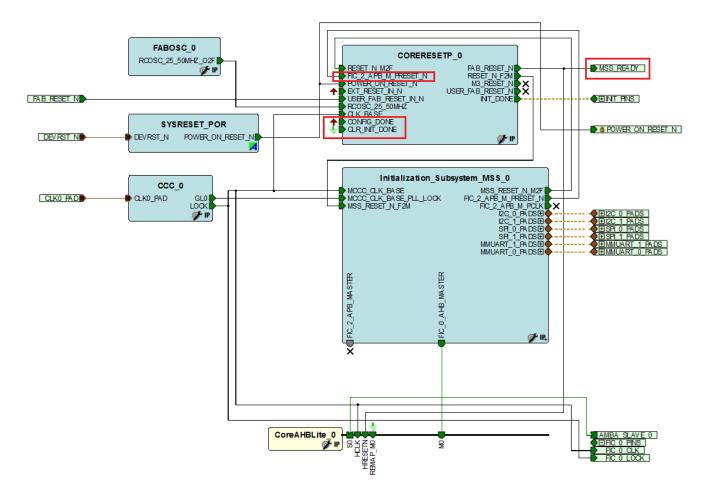

| 20. | Reset Controller                             |     |

|     | 20.1. Functional Description                 |     |

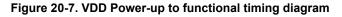

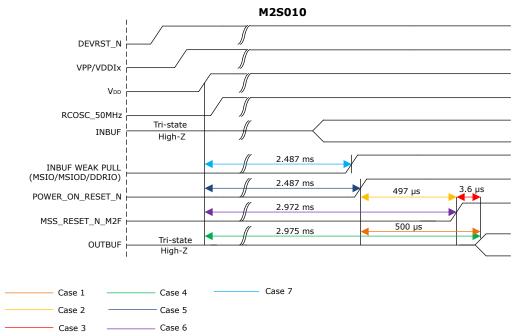

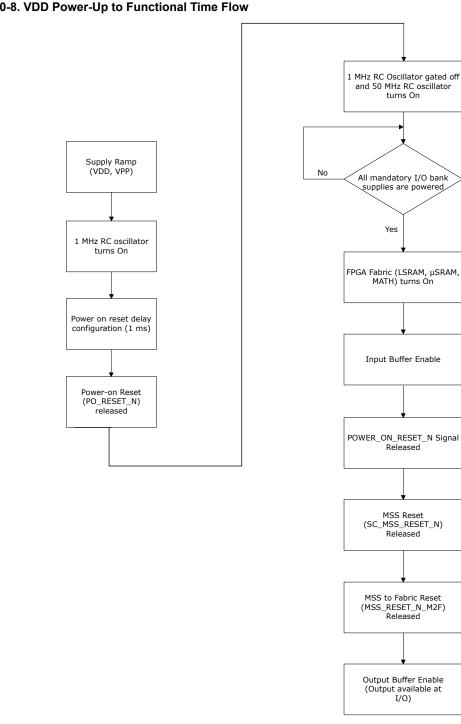

|     | 20.2. Power-Up to Functional Time Data       |     |

|     | 20.3. CoreResetP Soft Reset Controller       |     |

|     | 20.4. How to Use the Reset Controller        |     |

|     | 20.5.       SYSREG Control Registers.        |     |

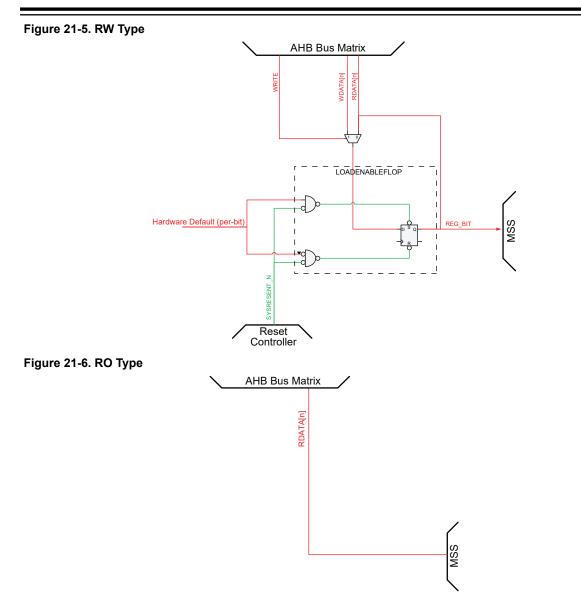

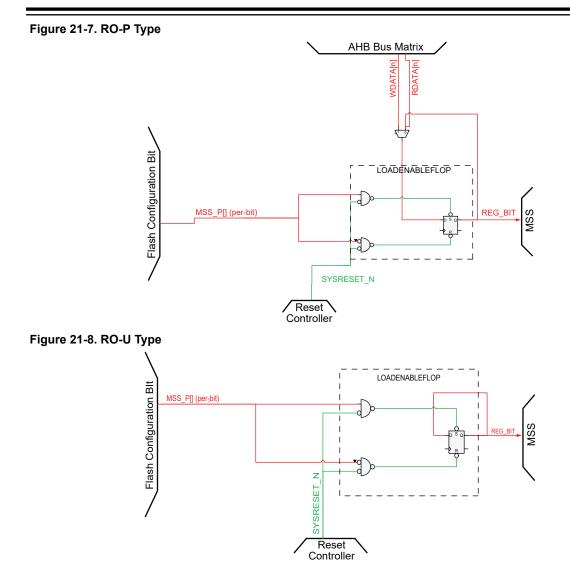

| 21. | System Register Block                        |     |

|     | 21.1. SYSREG Block Register Write Protection |     |

|     | 21.2. Register Types                         |     |

|     | 21.3. Register Lock Bits Configuration       |     |

|     | 21.4. Register Map                           |     |

|     |                                              |     |

|     | 21.5. Register Details                            |       |  |  |  |  |

|-----|---------------------------------------------------|-------|--|--|--|--|

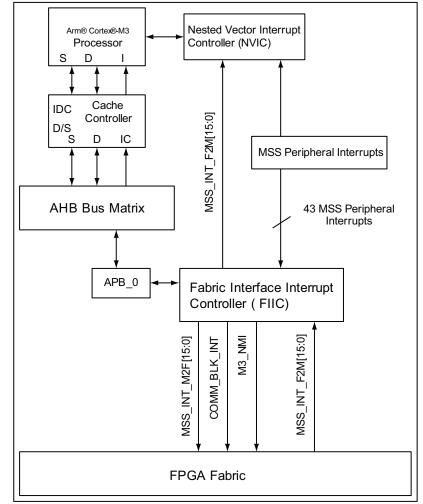

| 22. | 2. Fabric Interface Interrupt Controller          |       |  |  |  |  |

|     | 22.1. Features                                    |       |  |  |  |  |

|     | 22.2. Functional Description                      |       |  |  |  |  |

|     | 22.3. How to Use FIIC                             |       |  |  |  |  |

|     | 22.4. FIIC Controller Registers                   |       |  |  |  |  |

|     | 22.5. FIIC Controller Register Bit Definitions    |       |  |  |  |  |

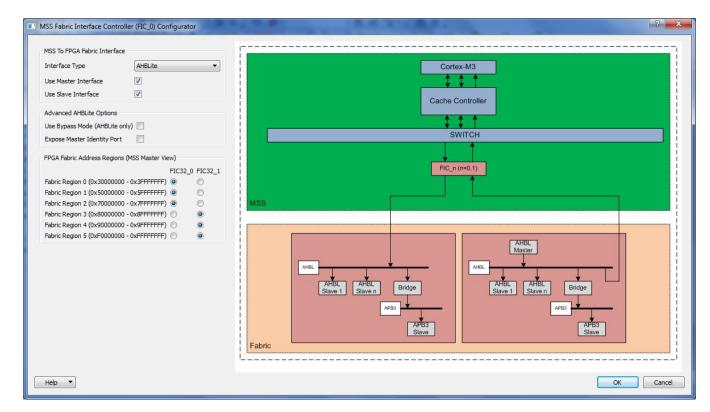

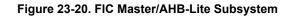

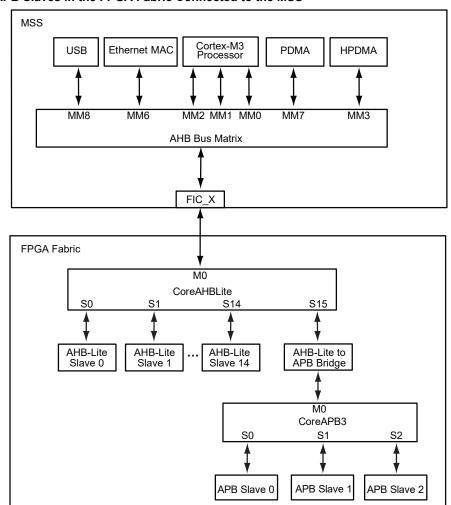

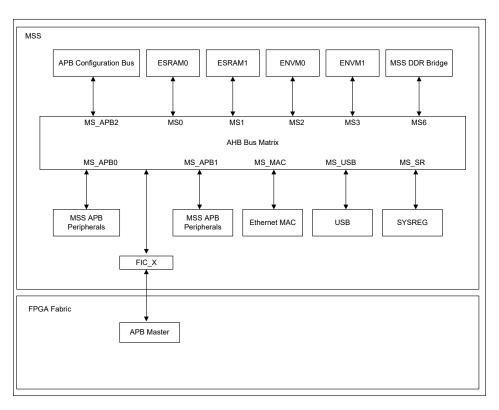

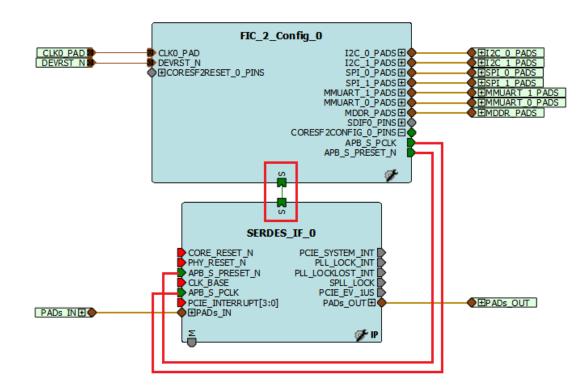

| 23. | 3. Fabric Interface Controller                    |       |  |  |  |  |

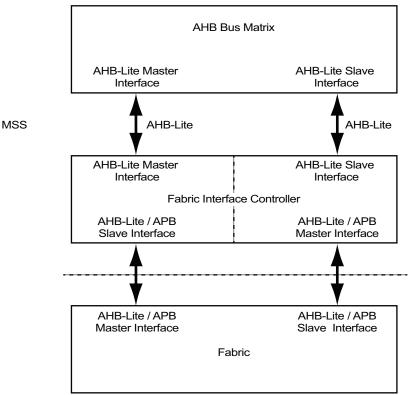

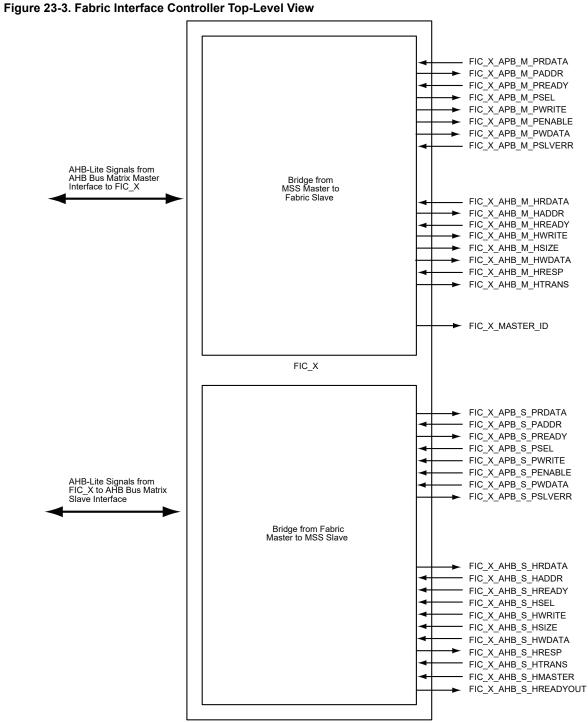

|     | 23.1. Functional Description                      |       |  |  |  |  |

|     | 23.2. Advanced AHB-Lite Options                   |       |  |  |  |  |

|     | 23.3. FIC Interface Port List                     |       |  |  |  |  |

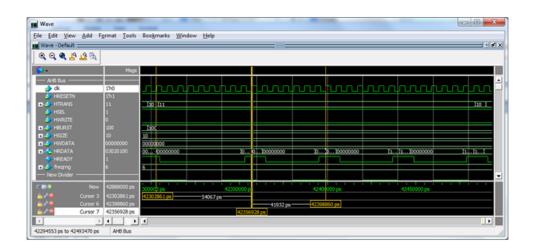

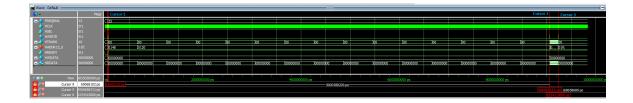

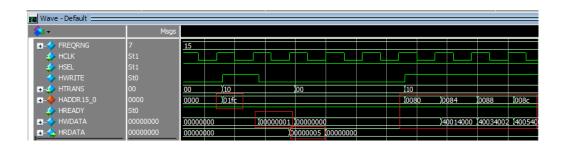

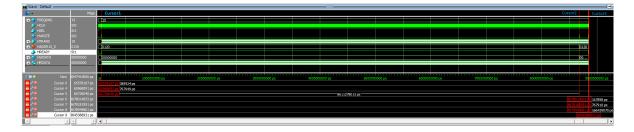

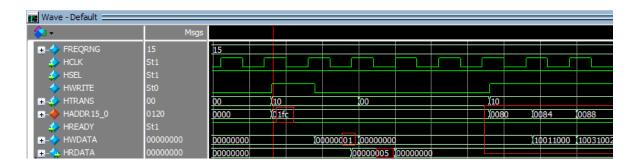

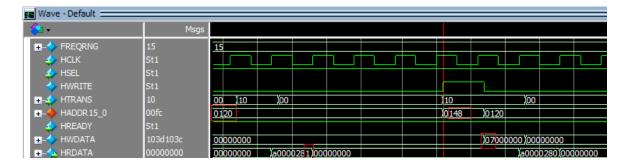

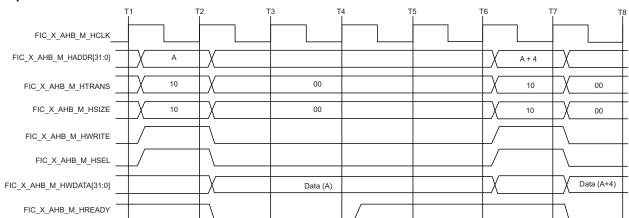

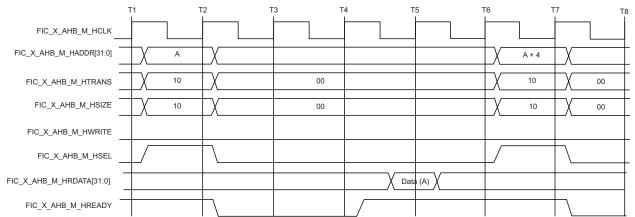

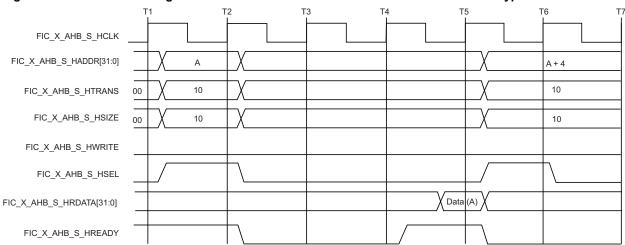

|     | 23.4. Timing Diagrams                             |       |  |  |  |  |

|     | 23.5. Implementation Considerations               |       |  |  |  |  |

|     | 23.6. Fabric Interface Clocks                     |       |  |  |  |  |

|     | 23.7. How to Use FIC                              |       |  |  |  |  |

|     | 23.8. Reference Documents                         |       |  |  |  |  |

|     | 23.9. SYSREG Control Registers for FIC_0 and FIC_ | _1781 |  |  |  |  |

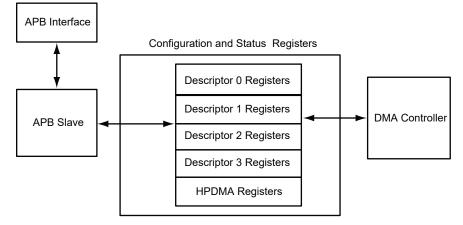

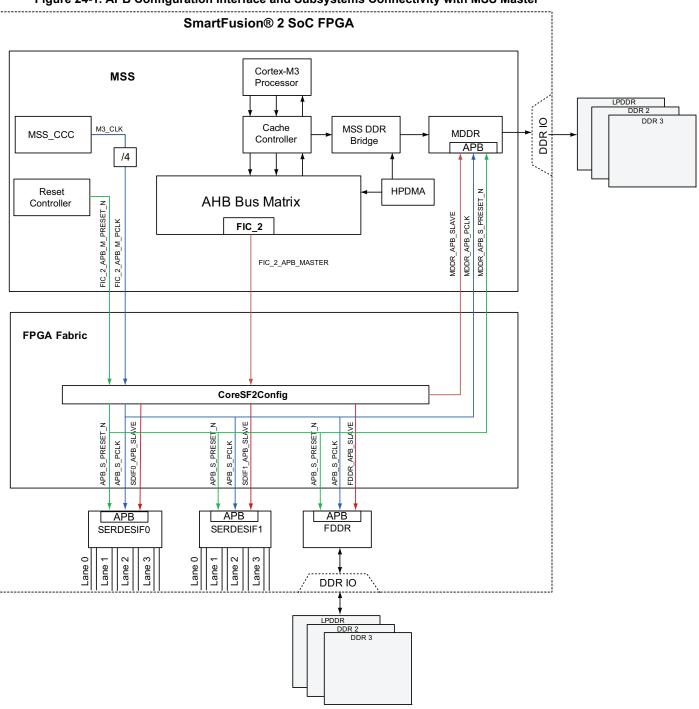

| 24. | 4. APB Configuration Interface                    |       |  |  |  |  |

|     | 24.1. Functional Block Diagram Description        |       |  |  |  |  |

|     | 24.2. How to Use                                  |       |  |  |  |  |

| 05  |                                                   |       |  |  |  |  |

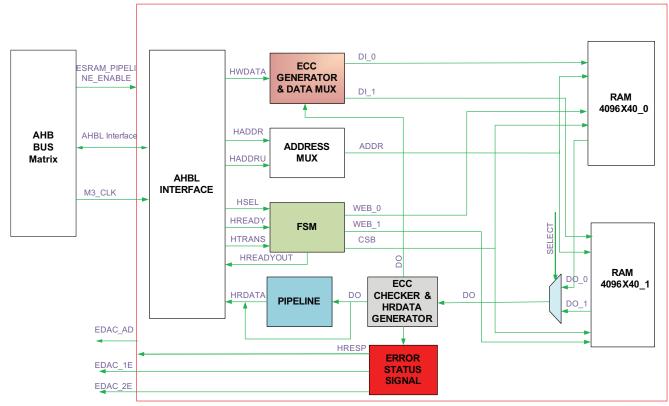

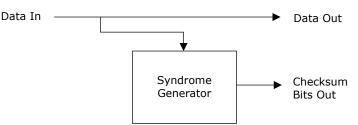

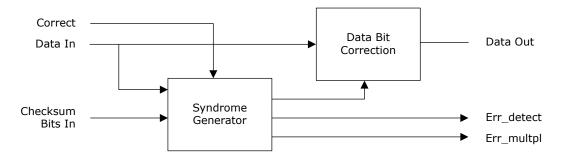

| 25. | 5. Error Detection and Correction Controllers     |       |  |  |  |  |

|     | 25.1. Functional Description                      |       |  |  |  |  |

|     | 25.2. Configuration                               |       |  |  |  |  |

|     | 25.3. How to Use EDAC                             |       |  |  |  |  |

| 26. | 6. Revision History                               |       |  |  |  |  |

| Mic | licrochip FPGA Support                            |       |  |  |  |  |

| Mic | licrochip Information                             |       |  |  |  |  |

|     | The Microchip Website                             |       |  |  |  |  |

|     | Product Change Notification Service               |       |  |  |  |  |

|     | Customer Support                                  |       |  |  |  |  |

|     | Microchip Devices Code Protection Feature         |       |  |  |  |  |

|     | Legal Notice                                      |       |  |  |  |  |

|     | Trademarks                                        |       |  |  |  |  |

|     | Quality Management System                         |       |  |  |  |  |

|     | Worldwide Sales and Service                       |       |  |  |  |  |

# 1. Cortex-M3 Processor Overview and Debug Features

The Arm<sup>®</sup> Cortex<sup>®</sup>-M3 processor is a low power consumption processor that features low gate count, low interrupt latency, and low-cost debug. It is intended for deeply embedded applications that require optimal interrupt response features. This processor implements the Arm v7-M architecture and is shown in Figure 1-1. The SmartFusion<sup>®</sup> 2 SoC FPGA device uses the R2P1 version of the Cortex-M3 core. This chapter highlights the Cortex-M3 processor and debug subsystem customizations made specific to SmartFusion 2.

For more details on the internals like programming model, exception model, instruction set, the Cortex-M3 specific peripherals such as SysTick timer, memory protection unit, and others, refer to the 2. Cortex-M3 Processor (Reference Material). The following manuals are available at the ARM Info center:

- Cortex-M3 Technical Reference Manual

- ARM v7-M Architecture Reference Manual

- ARM v7-M Architecture Application Level Reference Manual

The Definitive Guide to the Arm Cortex-M3 by Joseph Yiu is recommended as additional reading (ISBN: 978-0-7506-8534-4).

### 1.1 Features

The Arm Cortex-M3 processor supports the following features:

- A 32-bit processor core with low gate count and low latency interrupt processing

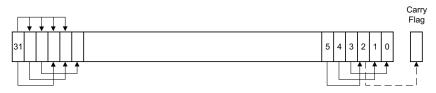

- A RISC processor, with 3-stage pipeline Harvard architecture, pipeline core incorporating branch speculation, single cycle multiplication, and hardware division, giving a Dhrystone benchmark of 1.25 DMIPS/MHz.

- A Nested Vectored Interrupt Controller (NVIC) that closely integrates with the processor core to achieve low latency interrupt processing.

- A memory protection unit (MPU) is included. This facilitates the protected memory regions creation and setting access rights for the protected regions.

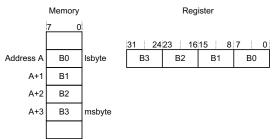

- A Cortex-M3 processor, which is configured for SmartFusion 2 MSS, and uses only little-endian.

- An auxiliary control register is included

- Multiple high-performance bus interfaces that are connected through an advanced high-performance bus (AHB)

- A debug solution with the optional ability to:

- Implement breakpoints and code patches

- Implement watchpoints, tracing, and system profiling

- Support print style debugging

- Bridge to a trace port analyzer

Manufacturers of the Cortex-M3 processor integrated circuits are permitted some latitude in configuring a particular implementation of the Cortex-M3 processor delivered by Arm. The following features are implementation specifics in the SmartFusion 2 device:

- MPU: This helps in creating protected and protected regions of memory

- Flash patch break point (FPB)

- Data watchpoint and trace (DWT) unit

- Instrumental trace macrocell (ITM)

- Embedded trace macrocell (ETM)

- Power-mode saving:

- HCLK is gated off when in SLEEPING or SLEEPDEEP mode

SLEEPING and SLEEPDEEP signals are available at the FPGA fabric interface sleep mode extension

handshake signals are available at the FPGA fabric interface.

- Not all registers in the register bank are reset

- Endianness: little endian only

- Auxiliary control register is included

• Wake-up interrupt controller (WIC) is not included

For more details of these configurations and optional features, see 2. Cortex-M3 Processor (Reference Material).

### 1.2 Functional Description

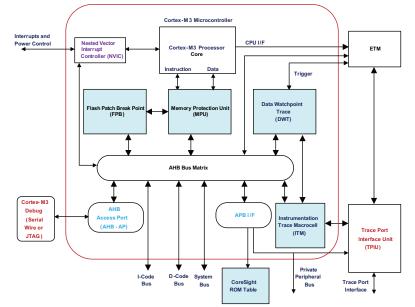

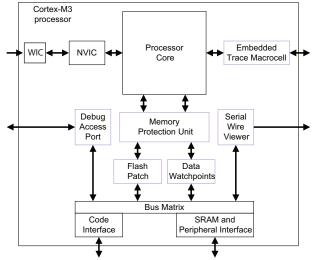

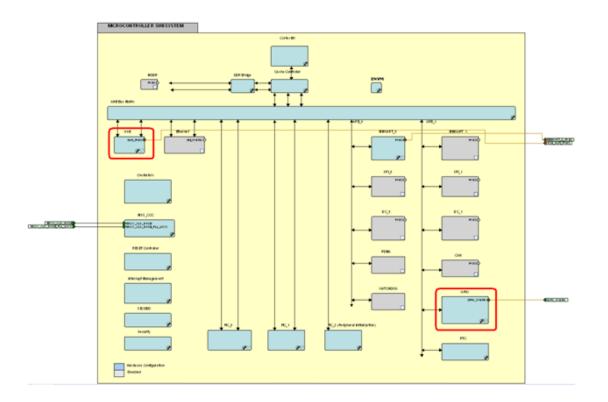

The following figure shows the Cortex-M3 processor, core peripherals, and debug subsystem implementations used in SmartFusion 2.

Figure 1-1. Cortex-M3 Processor R2P1 Block Diagram as Implemented in the SmartFusion 2 SoC FPGA

The following topics are covered in detail in the sub-sections:

- Cortex-M3 Processor NVIC

- Cortex-M3 Processor SysTick Timer

- Cortex-M3 Processor Debug Subsystem

- Data Watch Point (DWP) and Trace

- Instrumentation Trace Macrocell

- Embedded Trace Macrocell

**Important:** The Cortex-M3 operating frequency is dependent on device speed grade (up to 166 MHz). See the SmartFusion 2 Specifications-MSS Clock Frequency section from IGLOO 2 FPGA and SmartFusion 2 SoC FPGA Datasheet for more information.

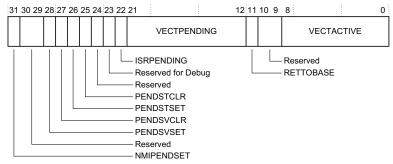

## 1.3 Cortex-M3 Processor NVIC

The Cortex-M3 processor contains an NVIC, which is responsible for:

- · Facilitating low-latency exception and interrupt handling

- Controlling power management

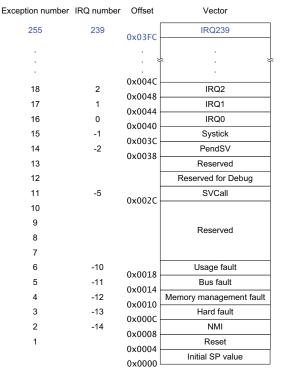

The following table lists the 11 exceptions that NVIC supports. The NVIC also supports up to 83 dynamically reprioritizable external interrupts, each with up to 16 levels of priority (see Table 1-2). The NVIC maintains knowledge of stacked (nested) interrupts to enable tail-chaining of interrupts. In MSS, the NVIC is configured to have 16 levels of priority (4 msb in BASEPRI register) are implemented, so BASEPRI register [7-4] are used for the priority setting and [3-0] are read as zeros. The following table lists exceptions. The detailed description of these exceptions can be found in the ARM Cortex-M3 Technical Reference Manual.

| Cortex-M3<br>Exceptions     | Position in<br>Interrupt Vector<br>Table | Priority     | Description                                                                                                                                                                                                         |

|-----------------------------|------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset                       | 1 (zero position is stack pointer)       | -3           | Invoked on power-up and reset                                                                                                                                                                                       |

| Non-maskable exception      | 2                                        | -2           | Non-maskable interrupt (NMI)—watchdog timeout interrupt                                                                                                                                                             |

| HardFault                   | 3                                        | -1           | Hard fault interrupt: all fault conditions if the corresponding fault handler is not enabled                                                                                                                        |

| Memory management exception | 4                                        | Configurable | Memory management interrupt: memory management fault; MPU violation or access to illegal locations.                                                                                                                 |

| Bus fault exception         | 5                                        | Configurable | Bus fault interrupt: bus error; occurs when the AHB<br>interface receives an error response from a bus slave<br>(also called prefetch abort if it is an instruction fetch or<br>data abort if it is a data access). |

| UsageFault                  | 6                                        | Configurable | Usage fault interrupt: exceptions resulting from a program error or trying to access a coprocessor (the Cortex-M3 does not support a coprocessor).                                                                  |

| SVCall                      | 11                                       | Configurable | Supervisory call interrupt                                                                                                                                                                                          |

| Debug monitor               | 12                                       | Configurable | Debug monitor interrupt: breakpoints, watchpoints, or external debug requests                                                                                                                                       |

| PendSV                      | 14                                       | Configurable | Pend supervisory interrupt                                                                                                                                                                                          |

| SysTick                     | 15                                       | Configurable | System tick timer interrupt                                                                                                                                                                                         |

Table 1-1. Cortex-M3 Processor Exceptions

The interrupt sources listed in the following table are connected to the NVIC of the Cortex-M3 processor in the MSS.

Table 1-2. Cortex-M3 Processor Interrupts

| Cortex-M3<br>Interrupt | Signal          | Source   | Description                                                                                                                                          |

|------------------------|-----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|

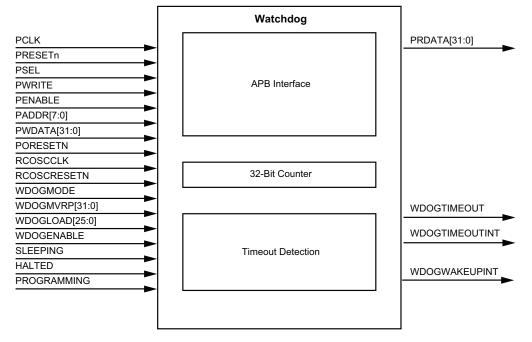

| INTNMI                 | WDOGTIMEOUTINT  | WATCHDOG | This interrupt is asserted (if enabled) if the counter reaches zero and interrupt rather than reset generation has been selected on counter timeout. |

| INTISR[0]              | WDOGWAKEUPINT   | WATCHDOG | This interrupt is asserted (if enabled) on crossing the WDOGMVRP level when the SLEEPING input is asserted.                                          |

| INTISR[1]              | RTC_WAKEUP_INTR | RTC      | RTC match/wake up interrupt from RTC block                                                                                                           |

| INTISR[2]              | SPIINT0         | SPI_0    | Interrupt from SPI 0                                                                                                                                 |

| INTISR[3]              | SPIINT1         | SPI_1    | Interrupt from SPI 1                                                                                                                                 |

| INTISR[4]              | I2C_INT0        | I2C_0    | Interrupt from I2C 0                                                                                                                                 |

| INTISR[5]              | I2C_SMBALERT0   | I2C_0    | Interrupt from I2C 0                                                                                                                                 |

| INTISR[6]              | I2C_SMBSUS0     | I2C_0    | Interrupt from I2C 0                                                                                                                                 |

| INTISR[7]              | I2C_INT1        | I2C_1    | Interrupt from I2C 1                                                                                                                                 |

| INTISR[8]              | I2C_SMBALERT1   | I2C_1    | Interrupt from I2C 1                                                                                                                                 |

| INTISR[9]              | I2C_SMBSUS1     | I2C_1    | Interrupt from I2C 1                                                                                                                                 |

| INTISR[10]             | MMUART0_INTR    | MMUART_0 | Interrupt from MMUART 0                                                                                                                              |

| INTISR[11]             | MMUART1_INTR    | MMUART_1 | Interrupt from MMUART 1                                                                                                                              |

| INTISR[12]             | MAC_INT         | MAC      | Interrupt from Ethernet MAC                                                                                                                          |

# Cortex-M3 Processor Overview and Debug Featu...

| continued              |                         |            |                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|------------------------|-------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Cortex-M3<br>Interrupt | Signal                  | Source     | Description                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| INTISR[13]             | PDMAINTERRUPT           | PDMA       | Interrupt from peripheral DMA block                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| INTISR[14]             | TIMER1_INTR             | TIMER      | Timer1 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| INTISR[15]             | TIMER2_INTR             | TIMER      | Timer2 interrupt                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| INTISR[16]             | CAN_INTR                | CAN        | Interrupt from CAN                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| INTISR[17]             | ENVM_INT0               | ENVMTOAHB0 | Asserted on an eNVM_0 basis at the completion of PROGRAM, ECC ERROR, etc.                                                                                                                                                                                                                                                                                                                                                                |  |

| INTISR[18]             | ENVM_INT1               | ENVMTOAHB1 | Asserted on an eNVM_1 basis at the completion of PROGRAM, ECC ERROR, etc.                                                                                                                                                                                                                                                                                                                                                                |  |

| INTISR[19]             | COMM_BLK_INTR           | COMBLK     | Communication block interrupt                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| INTISR[20]             | USB_MC_INT              | USB        | CPU interrupts                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| INTISR[21]             | USB_DMA_INT             | USB        | Core's DMA engine performs data transfer between endpoint memories and system memory via AHB master port. DMA controller-interrupt.                                                                                                                                                                                                                                                                                                      |  |

| INTISR[22]             | MSSDDR_PLL_LOCK_INT     | SYSREG     | Interrupt indicating that MSSDDR PLL has achieved lock.                                                                                                                                                                                                                                                                                                                                                                                  |  |

| INTISR[23]             | MSSDDR_PLL_LOCKLOST_INT | SYSREG     | Interrupt indicating that MSSDDR PLL has lost lock.                                                                                                                                                                                                                                                                                                                                                                                      |  |

| INTISR[24]             | SW_ERRORINTERRUPT       | SYSREG     | If set, it indicates to the Cortex-M3 processor that:<br>– One of the masters of the switch attempted an access that resulted in<br>either an error termination by the slave (or possibly the switch itself) or                                                                                                                                                                                                                          |  |

|                        |                         |            | <ul> <li>Was decoded as an access to unimplemented address space or o. If the<br/>master attempted an access while disabled or</li> </ul>                                                                                                                                                                                                                                                                                                |  |

|                        |                         |            | <ul> <li>In the case of the fabric master, attempted to access the protected region<br/>of memory space</li> </ul>                                                                                                                                                                                                                                                                                                                       |  |

|                        |                         |            | This signal is set by ORing the fields of SW_ERRORSTATUS. It is cleared by writing 1 to the SW_CLEARSTATUS bit.                                                                                                                                                                                                                                                                                                                          |  |

| INTISR[25]             | CACHE_ERRINTR           | SYSREG     | If asserted, indicates that the interrupt is coming from CACHE. This interrupt is generated in the SysReg by ORing of the various interrupts from the CACHE block: CC_HRESPERRINT0, CC_HRESPERRINT1, CC_HRESPERRINT2, CC_HRESPERRINT3.                                                                                                                                                                                                   |  |

| INTISR[26]             | DDRB_INTR               | SYSREG     | If asserted, indicates that the interrupt is coming from DDRBRDIGE module.<br>Interrupts from MSS DDR Bridge module: DDRB_ERROR and<br>DDRB_LOCKTIMEOUT.<br>These interrupts are ORed in the SysReg and fed to the Cortex-M3<br>processor.                                                                                                                                                                                               |  |

| INTISR[27]             | HPD_XFR_CMP_INT         | HPDMA      | It is asserted when any HPDMA completes a descriptor transfer. Once<br>asserted, it remains asserted until cleared by means of writing 1 to the<br>bit in the control register of the Descriptor-N (0, 1, 2, 3). If HPDMA<br>completes more than one descriptor transfers before the interrupt is<br>serviced then this bit remains asserted until all the descriptors have had<br>Clr_D <n>_Xfr_cmp_int written to 1.</n>               |  |

| INTISR[28]             | HPD_XFR_ERR_INT         | HPDMA      | It is asserted when any HPDMA completes a descriptor transfer with error.<br>Once asserted, it remains asserted until cleared by means of writing 1 to the<br>bit in the control register of the Descriptor-N (0, 1, 2, 3). If HPDMA completes<br>more than one descriptor with errors before the interrupt is serviced then this<br>bit remains asserted until all the descriptors have had Clr_D <n>_Xfr_err_int<br/>written to 1.</n> |  |

| INTISR[29]             | ECCINTR                 | SYSREG     | It is asserted when an ECC error has been detected in ESRAM0, ESRAM1, MAC, CAN, MDDR, and USB. This is generated by ORing ECC interrupts from these modules.                                                                                                                                                                                                                                                                             |  |

# Cortex-M3 Processor Overview and Debug Featu...

| continued              |                      |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|------------------------|----------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Cortex-M3<br>Interrupt | Signal               | Source      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| INTISR[30]             | MDDR_IO_CALIB_INT    | SYSREG      | The interrupt is generated when MDDR calibration is finished. For the calibration after reset, this would be followed by locking the codes directly. However, for in-between runs during functional DDR operation, the assertion of interrupt does not guarantee lock as the state machine would wait for the ideal time (DRAM self-refresh) for locking. This can be used by the firmware to insert an ideal time, and provides an indication of availability of locked codes. |  |  |

| INTISR[31]             | FAB_PLL_LOCK_INT     | SYSREG      | Interrupt indicating that MSSDDR PLL has achieved lock                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| INTISR[32]             | FAB_PLL_LOCKLOST_INT | SYSREG      | Interrupt indicating that MSSDDR PLL has lost lock                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| INTISR[33]             | FIC64_INT            | SYSREG      | This interrupt will be generated by FIC64 when one of the following conditions is true:<br>Write error for HPDMA or switch WCBs (from DDR_AXI_INTF)<br>Simultaneous read and write accesses by HPDMA and switch for same address<br>Lock time out condition                                                                                                                                                                                                                     |  |  |

| INTISR[34]             | F2H_INTERRUPT[0]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[35]             | F2H_INTERRUPT[1]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[36]             | F2H_INTERRUPT[2]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[37]             | F2H_INTERRUPT[3]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[38]             | F2H_INTERRUPT[4]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[39]             | F2H_INTERRUPT[5]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[40]             | F2H_INTERRUPT[6]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[41]             | F2H_INTERRUPT[7]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[42]             | F2H_INTERRUPT[8]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[43]             | F2H_INTERRUPT[9]     | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[44]             | F2H_INTERRUPT[10]    | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[45]             | F2H_INTERRUPT[11]    | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[46]             | F2H_INTERRUPT[12]    | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[47]             | F2H_INTERRUPT[13]    | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[48]             | F2H_INTERRUPT[14]    | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[49]             | F2H_INTERRUPT[15]    | FPGA fabric | Interrupt from the FPGA fabric                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| INTISR[50]             | GPIO_INT[0]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[51]             | GPIO_INT[1]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[52]             | GPIO_INT[2]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[53]             | GPIO_INT[3]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[54]             | GPIO_INT[4]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[55]             | GPIO_INT[5]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[56]             | GPIO_INT[6]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[57]             | GPIO_INT[7]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[58]             | GPIO_INT[8]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[59]             | GPIO_INT[9]          | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[60]             | GPIO_INT[10]         | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[61]             | GPIO_INT[11]         | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[62]             | GPIO_INT[12]         | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[63]             | GPIO_INT[13]         | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[64]             | GPIO_INT[14]         | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[65]             | GPIO_INT[15]         | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| INTISR[66]             | GPIO_INT[16]         | GPIO        | Interrupt from GPIO                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

## Cortex-M3 Processor Overview and Debug Featu...

| continued              |              |        |                     |  |  |

|------------------------|--------------|--------|---------------------|--|--|

| Cortex-M3<br>Interrupt | Signal       | Source | Description         |  |  |

| INTISR[67]             | GPIO_INT[17] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[68]             | GPIO_INT[18] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[69]             | GPIO_INT[19] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[70]             | GPIO_INT[20] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[71]             | GPIO_INT[21] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[72]             | GPIO_INT[22] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[73]             | GPIO_INT[23] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[74]             | GPIO_INT[24] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[75]             | GPIO_INT[25] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[76]             | GPIO_INT[26] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[77]             | GPIO_INT[27] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[78]             | GPIO_INT[28] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[79]             | GPIO_INT[29] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[80]             | GPIO_INT[30] | GPIO   | Interrupt from GPIO |  |  |

| INTISR[81]             | GPIO_INT[31] | GPIO   | Interrupt from GPIO |  |  |

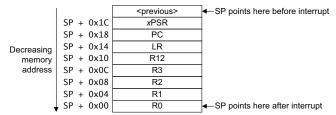

## 1.4 Cortex-M3 Processor SysTick Timer

The processor has a 24-bit system timer, SysTick, that counts down from the reload value to zero, reloads, that is, wraps to the value in the SYST\_RVR register on the next clock edge, and then counts down on subsequent clocks. The SysTick timer is used to generate a periodic interrupt to the Cortex-M3 processor. The SysTick can be polled by the software or it can be configured to generate an interrupt. The SysTick interrupt has its own entry in the vector table and therefore its own handler.

## 1.5 Cortex-M3 Processor Debug Subsystem

#### 1.5.1 Cortex-M3 Processor Debug Port

The debug port uses a serial wire (SW) JTAG debug port (SWJ-DP). This enables either the JTAG or the SW protocol to be used for debugging. The SWJ-DP defaults to JTAG mode at power-up and can be switched to SW by applying a specific sequence to the debug pins.

The trace port interface unit (TPIU) is configured to support ITM debug trace and ETM debug trace. Serial wire mode is used for the TPIU output data and this is overlaid on the JTAG TDO port. One implication of this is that instrumentation trace cannot be used along with JTAG-based debugging. SW debugging and ITM can be used together.

The Cortex-M3 processor provides the following debug Interfaces:

- SWJ-DP: JTAG is the industry-standard interface used to download and debug programs on a target processor, as well as for other functions. It offers access to all of the Cortex-M3 processor CoreSight<sup>®</sup> debug capabilities.

- SW-DP: The serial wire debug (SWD) mode is an alternative to the standard JTAG interface. SWD uses two

pins to provide the same debug functionality as JTAG with no performance penalty, and introduces data trace

capabilities with the serial wire viewer (SWV). The SWD interface pins are overlaid with the JTAG signals,

allowing standard target connectors to be used.

- TCLK: SWCLK (serial wire clock)

- TMS: SWDIO (serial wire debug data input/output)

- DO: SWO (output pin for SWV, refer to the next section).

- SWV: It provides real-time data trace information from various sources within the Cortex-M3 processor device. This is output via the single serial wire output (SWO) pin while your system processor continues running at full speed. SWV can only be used with the SWD interface.

• ETM: The embedded trace macrocell provides high bandwidth instruction trace via four dedicated trace pins.

#### 1.5.2 Cortex-M3 Processor Trace System

The debug system of the Cortex-M3 processor is based on the CoreSight architecture. The CoreSight-based designs enable the memory and peripheral registers to be examined even when the CPU is running. It also includes the following trace capabilities:

- Data trace, generating events to record data reads/writes, exceptions/interrupts, and PC (program counter) sampling information.

- · Software trace, supporting output of debug messages (for example, printf) to the host.

- Instruction trace, collecting a sequence of every executed instruction continuously for a selected portion of your application.

Trace data can be useful for debugging issues and collecting statistics:

- Locating errors that have irregular symptoms

- Analyzing dynamic system behavior

- · Optimizing performance bottlenecks

- Counting code coverage statistics

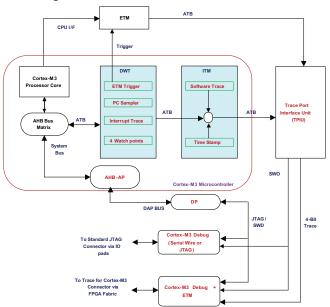

Trace results are generated in the form of packets, which can be of various lengths. The trace components transfer the packets using the advanced trace bus (ATB) to the TPIU, which formats the packets into the trace interface protocol (TIP). The data is then captured by an external trace capture device such as a trace port analyzer (TPA).

The main components of the Cortex-M3 processor that can be a trace source:

- DWT, for data trace

- ITM, for software trace

- ETM, for full instruction trace

DWT, ITM, and ETM generate trace data in the form of packets and transfer them through the ATB to the TPIU.

The TPIU has two operation modes:

- Clocked mode, using up to 4-bit (1-, 2- or 4-bit) parallel data outputs

- SWV mode, using the single-bit SWO format. Instruction trace from ETM must use the parallel trace port, while packets of data trace and software trace normally use SWO (called SWO trace) but can also be multiplexed with the ETM trace stream through the parallel trace port.

The following figure shows the diagram of a Cortex-M3 processor trace system. JTAG/SWD, SWO, and the 4-bit parallel trace port can be deployed into a 20-pin Cortex Debug + ETM connector on the target.

**Important:** The TDO signal of JTAG is multiplexed with SWO, so that SWO trace is not accessible when the DP is in a JTAG configuration. Only the SWD interface can be used together with SWO.

#### Figure 1-2. Trace System Block Diagram

The following table shows pin multiplexing details for JTAG, SWD, and ETM modes of the debug section. For more details on pin information, refer to the DS0115: SmartFusion2 Pin Descriptions Datasheet.

#### Table 1-3. Signal Multiplexing

| FPGA Pin             | JTAG Mode | SWD Mode | ETM Mode       |