### **Product Change Notification / SYST-01FITH395**

Date:

02-Dec-2021

### **Product Category:**

Analog to Digital Converters

### **PCN Type:**

Document Change

### **Notification Subject:**

Data Sheet - MCP3911 3.3V Two-Channel Analog Front End Data Sheet Document Revision

#### **Affected CPNs:**

SYST-01FITH395\_Affected\_CPN\_12022021.pdf SYST-01FITH395\_Affected\_CPN\_12022021.csv

### **Notification Text:**

SYST-01FITH395

Microchip has released a new Product Documents for the MCP3911 3.3V Two-Channel Analog Front End Data Sheet of devices. If you are using one of these devices please read the document located at MCP3911 3.3V Two-Channel Analog Front End Data Sheet.

Notification Status: Final

#### **Description of Change:**

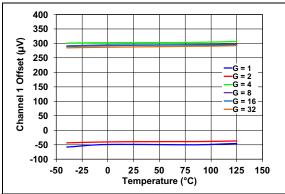

The following is the list of modifications: 1. Updated Figures 2-31, 2-32, 2-33.

Impacts to Data Sheet: See above details.

Reason for Change: To Improve Productivity

Change Implementation Status: Complete

Date Document Changes Effective: 02 Dec 2021

NOTE: Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

| Attachments:                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCP3911 3.3V Two-Channel Analog Front End Data Sheet                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                             |

| Please contact your local Microchip sales office with questions or concerns regarding this notification.                                                                                                                                                                                    |

| Terms and Conditions:                                                                                                                                                                                                                                                                       |

| If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section. |

| If you wish to <u>change your PCN profile</u> , <u>including opt out</u> , please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.                              |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                             |

# MCP3911

## 3.3V Two-Channel Analog Front End

#### **Features**

- Two Synchronous Sampling 16/24-bit Resolution Delta-Sigma A/D Converters

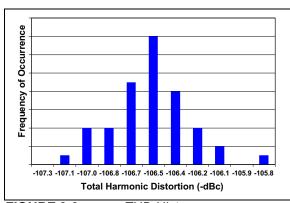

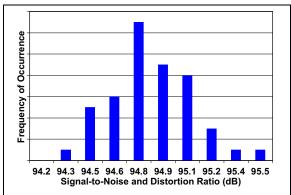

- 94.5 dB SINAD, -106.5 dBc Total Harmonic Distortion (THD) (up to 35<sup>th</sup> harmonic), 111 dB SFDR for Each Channel

- 2.7V-3.6V AV<sub>DD</sub>, DV<sub>DD</sub>

- · Programmable Data Rate Up to 125 ksps:

- 4 MHz Maximum Sampling Frequency

- · Oversampling Ratio Up to 4096

- Ultra Low-Power Shutdown Mode with <2 µA

- · -122 dB Crosstalk Between the Two Channels

- Low-Drift 1.2V Internal Voltage Reference: 7 ppm/°C

- · Differential Voltage Reference Input Pins

- High-Gain Programmable Gain Amplifier (PGA) on Each Channel (up to 32V/V)

- Phase Delay Compensation with 1 µs Time Resolution

- Separate Modulator Output Pins for Each Channel

- Separate Data Ready Pin for Easy Synchronization

- Individual 24-Bit Digital Offset and Gain Error Correction for Each Channel

- High-Speed 20 MHz SPI Interface with Mode 0,0 and 1,1 Compatibility

- Continuous Read/Write Modes for Minimum Communication

- Low-Power Consumption (8.9 mW at 3.3V, 5.6 mW at 3.3V in Low-Power mode, typical)

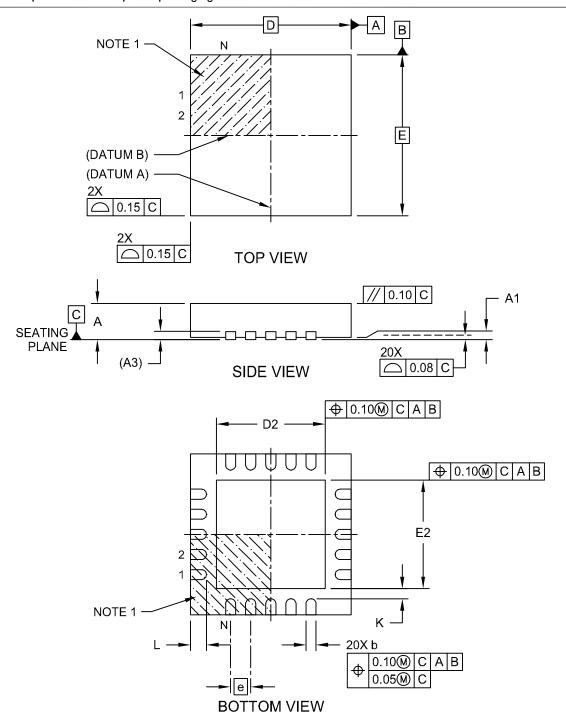

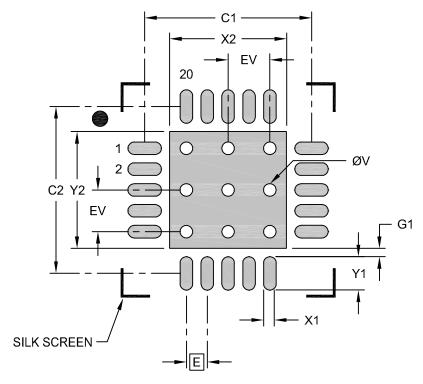

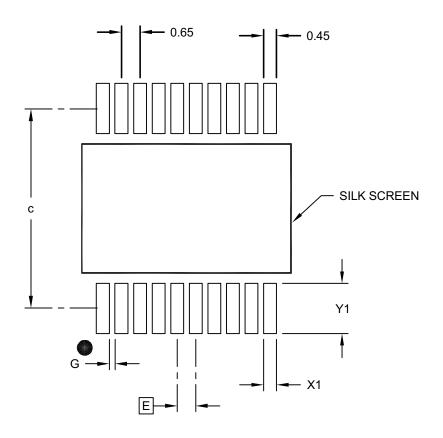

- Available in Small 20-Lead QFN and SSOP Packages, Pin-to-Pin Compatible with MCP3901

- Extended Temperature Range: -40°C to +125°C

#### **Applications**

- · Energy Metering and Power Measurement

- Automotive

- · Portable Instrumentation

- · Medical and Power Monitoring

- Audio/Voice Recognition

#### **Description**

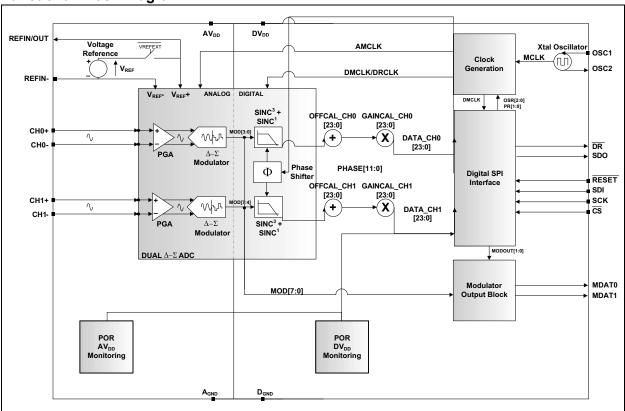

The MCP3911 is a 2.7V to 3.6V dual channel Analog Front End (AFE) containing two synchronous sampling Delta-Sigma Analog-to-Digital Converters (ADC), two PGAs, phase delay compensation block, low-drift internal voltage reference, modulator output block, Digital Offset and Gain Error Calibration registers and high-speed 20 MHz SPI compatible serial interface.

The MCP3911 ADCs are fully configurable with features, such as: 16/24-bit resolution, Oversampling Ratio (OSR) from 32 to 4096, gain from 1x to 32x, independent shutdown and Reset, dithering and autozeroing. The communication is largely simplified with the one-byte long commands, including various continuous Read/Write modes that can be accessed by the Direct Memory Access (DMA) of an MCU with a separate Data Ready pin that can be directly connected to an Interrupt Request (IRQ) input of an MCU.

The MCP3911 is capable of interfacing a large variety of voltage and current sensors, including shunts, current transformers, Rogowski coils and Hall effect sensors.

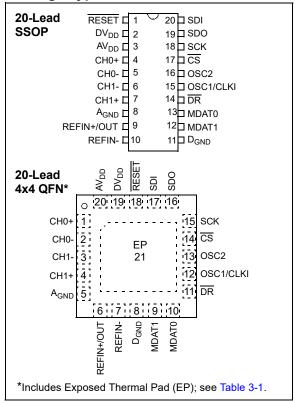

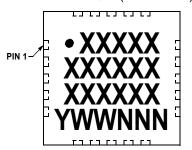

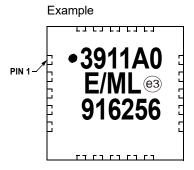

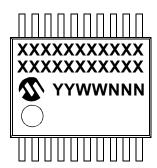

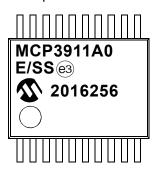

#### **Package Type**

#### **Functional Block Diagram**

# 1.0 ELECTRICAL CHARACTERISTICS

#### **Absolute Maximum Ratings†**

| V <sub>DD</sub>                                    | 0.3V to 4.0V                   |

|----------------------------------------------------|--------------------------------|

| Digital inputs and outputs w.r.t. A <sub>GND</sub> | 0.3V to 4.0V                   |

| Analog input w.r.t. A <sub>GND</sub>               | 2V to +2V                      |

| V <sub>REF</sub> input w.r.t. A <sub>GND</sub>     | 0.6V to V <sub>DD</sub> + 0.6V |

| Storage temperature                                | 65°C to +150°C                 |

| Ambient temp. with power applied                   | 65°C to +125°C                 |

| Soldering temperature of leads (10 second          | nds)+300°C                     |

| ESD on the analog inputs (HBM,MM)                  | 4.0 kV, 300V                   |

| ESD on all other pins (HBM,MM)                     | 4.0 kV, 300V                   |

**† Notice**: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operational listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

#### 1.1 Electrical Specifications

#### TABLE 1-1: ANALOG SPECIFICATIONS TARGET

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at AV<sub>DD</sub> = DV<sub>DD</sub> = 2.7V to 3.6V; MCLK = 4 MHz; PRE[1:0] = 00; OSR = 256; GAIN = 1; VREFEXT = 0; CLKEXT = 1; AZ\_FREQ = 0; DITHER[1:0] = 11; BOOST[1:0] = 10;  $V_{CM} = 0V$ ;  $V_{CM} =$

| Characteristic                                                     | Sym                    | Min       | Тур | Max       | Units | Conditions                                              |

|--------------------------------------------------------------------|------------------------|-----------|-----|-----------|-------|---------------------------------------------------------|

| ADC Performance                                                    |                        |           |     |           |       |                                                         |

| Resolution (No Missing Codes)                                      |                        | 24        | _   | _         | bits  | OSR = 256 or greater                                    |

| Sampling Frequency                                                 | f <sub>S</sub> (DMCLK) | _         | 1   | 4         | MHz   | For maximum condition,<br>BOOST[1:0] = 11               |

| Output Data Rate                                                   | f <sub>D</sub> (DRCLK) | _         | 4   | 125       | ksps  | For maximum condition,<br>BOOST[1:0] = 11, OSR = 32     |

| Analog Input Absolute<br>Voltage on CH0+, CH0-,<br>CH1+, CH1- Pins | CH0+/-                 | -1        |     | +1        | V     | All analog input channels, measured to A <sub>GND</sub> |

| Analog Input<br>Leakage Current                                    | I <sub>IN</sub>        | _         | ±1  | _         | nA    | RESET[1:0] = 11,<br>MCLK running continuously           |

| Differential Input<br>Voltage Range                                | (CHn+ – CHn-)          | -600/GAIN | _   | +600/GAIN | mV    | $V_{REF}$ = 1.2V,<br>proportional to $V_{REF}$          |

| Offset Error                                                       | V <sub>OS</sub>        | -2        | 0.2 | +2        | mV    | Note 4                                                  |

| Offset Error Drift                                                 |                        |           | 0.5 | _         | μV/°C |                                                         |

| Gain Error                                                         | GE                     | -6        | _   | +6        | %     | Note 4                                                  |

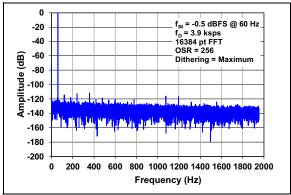

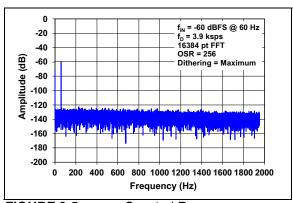

- Note 1: This specification implies that the ADC output is valid over this entire differential range and that there is no distortion or instability across this input range. Dynamic performance specified at -0.5 dB below the maximum signal range, V<sub>IN</sub> = 1.2 V<sub>PP</sub> = 424 mV<sub>RMS</sub>, V<sub>REF</sub> = 1.2V at 50/60 Hz. See Section 4.0, Terminologies and Formulas for definition. This parameter is established by characterization and is not 100% tested. See performance graphs for other than default settings provided here.

- 2: For these operating currents, the following Configuration bit settings apply: SHUTDOWN[1:0] = 00, RESET[1:0] = 00, VREFEXT = 0, CLKEXT = 0.

- **3:** For these operating currents, the following Configuration bit settings apply: SHUTDOWN[1:0] = 11, VREFEXT = 1, CLKEXT = 1.

- 4: Applies to all gains. Offset and gain errors depend on PGA gain setting; see Section 2.0, Typical Performance Curves for typical performance.

- 5: Outside of this range, the ADC accuracy is not specified. An extended input range of ±2V can be applied continuously to the part with no damage.

- 6: For proper operation and optimizing ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-2 as a function of the BOOST and PGA settings chosen. MCLK can take larger values as long as the prescaler settings (PRE[1:0]) limit AMCLK = MCLK/PRESCALE in the defined range in Table 5-2.

#### TABLE 1-1: ANALOG SPECIFICATIONS TARGET (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at AV<sub>DD</sub> = DV<sub>DD</sub> = 2.7V to 3.6V; MCLK = 4 MHz; PRE[1:0] = 00; OSR = 256; GAIN = 1; VREFEXT = 0; CLKEXT = 1; AZ\_FREQ = 0; DITHER[1:0] = 11; BOOST[1:0] = 10;  $V_{CM} = 0V$ ;  $V_{CM} =$

| Characteristic                                | Sym             | Min | Тур    | Max  | Units  | Conditions                                                      |

|-----------------------------------------------|-----------------|-----|--------|------|--------|-----------------------------------------------------------------|

| Gain Error Drift                              |                 |     | 1      |      | ppm/°C |                                                                 |

| Integral Nonlinearity                         | INL             | _   | 5      | _    | ppm    |                                                                 |

| Differential Input                            | Z <sub>IN</sub> | 232 | _      | _    | kΩ     | G = 1, proportional to 1/AMCLK                                  |

| Impedance                                     |                 | 142 |        |      | kΩ     | G = 2, proportional to 1/AMCLK                                  |

|                                               | ·               | 72  | _      | _    | kΩ     | G = 4, proportional to 1/AMCLK                                  |

|                                               | ·               | 38  | _      | _    | kΩ     | G = 8, proportional to 1/AMCLK                                  |

|                                               |                 | 36  | _      |      | kΩ     | G = 16, proportional to 1/AMCLK                                 |

|                                               | ·               | 33  | _      | _    | kΩ     | G = 32, proportional to 1/AMCLK                                 |

| Signal-to-Noise and Distortion Ratio (Note 1) | SINAD           | 92  | 94.5   | _    | dB     |                                                                 |

| Total Harmonic Distortion (Note 1)            | THD             | _   | -106.5 | -103 | dBc    | Includes the first 35 harmonics                                 |

| Signal-to-Noise Ratio (Note 1)                | SNR             | 92  | 95     | _    | dB     |                                                                 |

| Spurious-Free Dynamic<br>Range (Note 1)       | SFDR            | _   | 111    | _    | dBFS   |                                                                 |

| Crosstalk (50, 60 Hz)                         | CTALK           | _   | -122   | _    | dB     |                                                                 |

| AC Power Supply Rejection                     | AC PSRR         | _   | -73    | _    | dB     | $AV_{DD} = DV_{DD} = 3.3V + 0.6V_{PP,}$<br>50/60 Hz, 100/120 Hz |

| DC Power<br>Supply Rejection                  | DC PSRR         | _   | -73    | _    | dB     | $AV_{DD} = DV_{DD} = 2.7V \text{ to } 3.6V$                     |

| DC Common-Mode<br>Rejection                   | DC CMRR         | _   | -105   | _    | dB     | V <sub>CM</sub> from -1V to +1V                                 |

- Note 1: This specification implies that the ADC output is valid over this entire differential range and that there is no distortion or instability across this input range. Dynamic performance specified at -0.5 dB below the maximum signal range, V<sub>IN</sub> = 1.2 V<sub>PP</sub> = 424 mV<sub>RMS</sub>, V<sub>REF</sub> = 1.2V at 50/60 Hz. See Section 4.0, Terminologies and Formulas for definition. This parameter is established by characterization and is not 100% tested. See performance graphs for other than default settings provided here.

- 2: For these operating currents, the following Configuration bit settings apply: SHUTDOWN[1:0] = 00, RESET[1:0] = 00, VREFEXT = 0, CLKEXT = 0.

- **3:** For these operating currents, the following Configuration bit settings apply: SHUTDOWN[1:0] = 11, VREFEXT = 1, CLKEXT = 1.

- 4: Applies to all gains. Offset and gain errors depend on PGA gain setting; see Section 2.0, Typical Performance Curves for typical performance.

- 5: Outside of this range, the ADC accuracy is not specified. An extended input range of ±2V can be applied continuously to the part with no damage.

- 6: For proper operation and optimizing ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-2 as a function of the BOOST and PGA settings chosen. MCLK can take larger values as long as the prescaler settings (PRE[1:0]) limit AMCLK = MCLK/PRESCALE in the defined range in Table 5-2.

TABLE 1-1: ANALOG SPECIFICATIONS TARGET (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at AV<sub>DD</sub> = DV<sub>DD</sub> = 2.7V to 3.6V; MCLK = 4 MHz; PRE[1:0] = 00; OSR = 256; GAIN = 1; VREFEXT = 0; CLKEXT = 1; AZ\_FREQ = 0; DITHER[1:0] = 11; BOOST[1:0] = 10;  $V_{CM} = 0V$ ;  $V_{CM} =$

| Characteristic                                                                | Sym                  | Min                      | Тур | Max                      | Units      | Conditions                                                      |

|-------------------------------------------------------------------------------|----------------------|--------------------------|-----|--------------------------|------------|-----------------------------------------------------------------|

| Internal Voltage Reference                                                    | !                    |                          |     |                          |            |                                                                 |

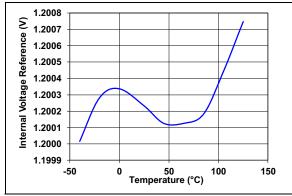

| Tolerance                                                                     | $V_{REF}$            | 1.176                    | 1.2 | 1.224                    | V          | VREFEXT = 0, T <sub>A</sub> = +25°C only                        |

| Temperature Coefficient                                                       | TCV <sub>REF</sub>   | _                        | 7   | _                        | ppm/°C     | $T_A = -40$ °C to +125°C,<br>VREFEXT = 0                        |

| Output Impedance                                                              | ZOUTV <sub>REF</sub> | _                        | 2   | _                        | <b>k</b> Ω | VREFEXT = 0                                                     |

| Internal Voltage Reference<br>Operating Current                               | $AI_{DD}V_{REF}$     | _                        | 25  | _                        | μA         | VREFEXT = 0,<br>SHUTDOWN[1:0] = 11                              |

| Voltage Reference Input                                                       |                      |                          |     |                          |            |                                                                 |

| Input Capacitance                                                             |                      | _                        | _   | 10                       | pF         |                                                                 |

| Differential Input Voltage<br>Range (V <sub>REF</sub> + – V <sub>REF</sub> -) | $V_{REF}$            | 1.1                      |     | 1.3                      | <b>V</b>   | VREFEXT = 1                                                     |

| Absolute Voltage on REFIN+ Pin                                                | V <sub>REF</sub> +   | V <sub>REF</sub> - + 1.1 | _   | V <sub>REF</sub> - + 1.3 | V          | VREFEXT = 1                                                     |

| Absolute Voltage on REFIN- Pin                                                | V <sub>REF</sub> -   | -0.1                     | _   | +0.1                     | V          | REFIN- should be connected to A <sub>GND</sub> when VREFEXT = 0 |

| Master Clock Input                                                            |                      |                          |     | •                        |            |                                                                 |

| Master Clock Input<br>Frequency Range                                         | f <sub>MCLK</sub>    | _                        |     | 20                       | MHz        | CLKEXT = 1 (Note 6)                                             |

| Crystal Oscillator<br>Operating Frequency<br>Range                            | f <sub>XTAL</sub>    | 1                        | _   | 20                       | MHz        | CLKEXT = 0 (Note 6)                                             |

| Analog Master Clock                                                           | AMCLK                | _                        | _   | 16                       | MHz        | Note 6                                                          |

| Power Supply                                                                  |                      |                          |     | •                        |            |                                                                 |

| Operating Voltage, Analog                                                     | $AV_DD$              | 2.7                      | 1   | 3.6                      | <b>V</b>   |                                                                 |

| Operating Voltage, Digital                                                    | $DV_DD$              | 2.7                      | _   | 3.6                      | V          |                                                                 |

| Operating Current,                                                            | $I_{DD,A}$           | _                        | 1.5 | 2.3                      | mA         | BOOST[1:0] = 00                                                 |

| Analog (Note 2)                                                               |                      | _                        | 1.8 | 2.8                      | mA         | BOOST[1:0] = 01                                                 |

|                                                                               |                      | _                        | 2.5 | 3.5                      | mA         | BOOST[1:0] = 10                                                 |

|                                                                               |                      | _                        | 4.4 | 6.25                     | mA         | BOOST[1:0] = 11                                                 |

- Note 1: This specification implies that the ADC output is valid over this entire differential range and that there is no distortion or instability across this input range. Dynamic performance specified at -0.5 dB below the maximum signal range, V<sub>IN</sub> = 1.2 V<sub>PP</sub> = 424 mV<sub>RMS</sub>, V<sub>REF</sub> = 1.2V at 50/60 Hz. See Section 4.0, Terminologies and Formulas for definition. This parameter is established by characterization and is not 100% tested. See performance graphs for other than default settings provided here.

- 2: For these operating currents, the following Configuration bit settings apply: SHUTDOWN[1:0] = 00, RESET[1:0] = 00, VREFEXT = 0, CLKEXT = 0.

- **3:** For these operating currents, the following Configuration bit settings apply: SHUTDOWN[1:0] = 11, VREFEXT = 1, CLKEXT = 1.

- **4:** Applies to all gains. Offset and gain errors depend on PGA gain setting; see **Section 2.0**, **Typical Performance Curves** for typical performance.

- 5: Outside of this range, the ADC accuracy is not specified. An extended input range of ±2V can be applied continuously to the part with no damage.

- **6:** For proper operation and optimizing ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-2 as a function of the BOOST and PGA settings chosen. MCLK can take larger values as long as the prescaler settings (PRE[1:0]) limit AMCLK = MCLK/PRESCALE in the defined range in Table 5-2.

#### TABLE 1-1: ANALOG SPECIFICATIONS TARGET (CONTINUED)

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at AV<sub>DD</sub> = DV<sub>DD</sub> = 2.7V to 3.6V; MCLK = 4 MHz; PRE[1:0] = 00; OSR = 256; GAIN = 1; VREFEXT = 0; CLKEXT = 1; AZ\_FREQ = 0; DITHER[1:0] = 11; BOOST[1:0] = 10;  $V_{CM} = 0V$ ;  $V_{CM} =$

| Characteristic             | Sym                | Min | Тур | Max | Units | Conditions                             |

|----------------------------|--------------------|-----|-----|-----|-------|----------------------------------------|

| Operating Current, Digital | I <sub>DD,D</sub>  | _   | 0.2 | 0.3 |       | MCLK = 4 MHz,<br>proportional to MCLK  |

|                            |                    |     | 0.7 | _   |       | MCLK = 16 MHz,<br>proportional to MCLK |

| Shutdown Current, Analog   | I <sub>DDS,A</sub> | _   | _   | 1   | μΑ    | AV <sub>DD</sub> pin only (Note 3)     |

| Shutdown Current, Digital  | I <sub>DDS,D</sub> | _   | _   | 1   | μA    | DV <sub>DD</sub> pin only (Note 3)     |

- Note 1: This specification implies that the ADC output is valid over this entire differential range and that there is no distortion or instability across this input range. Dynamic performance specified at -0.5 dB below the maximum signal range, V<sub>IN</sub> = 1.2 V<sub>PP</sub> = 424 mV<sub>RMS</sub>, V<sub>REF</sub> = 1.2V at 50/60 Hz. See Section 4.0, Terminologies and Formulas for definition. This parameter is established by characterization and is not 100% tested. See performance graphs for other than default settings provided here.

- 2: For these operating currents, the following Configuration bit settings apply: SHUTDOWN[1:0] = 00, RESET[1:0] = 00, VREFEXT = 0, CLKEXT = 0.

- **3:** For these operating currents, the following Configuration bit settings apply: SHUTDOWN[1:0] = 11, VREFEXT = 1, CLKEXT = 1.

- 4: Applies to all gains. Offset and gain errors depend on PGA gain setting; see Section 2.0, Typical Performance Curves for typical performance.

- 5: Outside of this range, the ADC accuracy is not specified. An extended input range of ±2V can be applied continuously to the part with no damage.

- 6: For proper operation and optimizing ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-2 as a function of the BOOST and PGA settings chosen. MCLK can take larger values as long as the prescaler settings (PRE[1:0]) limit AMCLK = MCLK/PRESCALE in the defined range in Table 5-2.

#### 1.2 Serial Interface Characteristics

#### TABLE 1-2: SERIAL DC CHARACTERISTICS

| <b>Electrical Specifications:</b> Unless otherwise indicated, all parameters apply at $DV_{DD} = 2.7$ to 3.6V; $T_A = -40$ °C to $+125$ °C; $C_{LOAD} = 30$ pF; applies to all digital I/Os. |                  |                      |     |                      |       |                                                                                                                                      |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------|-----|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Characteristics                                                                                                                                                                              | Sym              | Min                  | Тур | Max                  | Units | Test Conditions                                                                                                                      |  |  |

| High-Level Input Voltage                                                                                                                                                                     | $V_{IH}$         | 0.7 DV <sub>DD</sub> | _   | _                    | V     | Schmitt Triggered                                                                                                                    |  |  |

| Low-Level Input Voltage                                                                                                                                                                      | $V_{IL}$         |                      | 1   | 0.3 DV <sub>DD</sub> | V     | Schmitt Triggered                                                                                                                    |  |  |

| Input Leakage Current                                                                                                                                                                        | I <sub>LI</sub>  |                      | _   | ±1                   | μΑ    | $\overline{\text{CS}} = \text{DV}_{\text{DD}},$<br>$V_{\text{IN}} = D_{\text{GND}} \text{ to DV}_{\text{DD}}$                        |  |  |

| Output leakage Current                                                                                                                                                                       | I <sub>LO</sub>  |                      | _   | ±1                   | μA    | $\overline{\text{CS}} = \text{DV}_{\text{DD}},$<br>$\text{V}_{\text{OUT}} = \text{D}_{\text{GND}} \text{ or } \text{DV}_{\text{DD}}$ |  |  |

| Hysteresis of Schmitt<br>Trigger Inputs                                                                                                                                                      | V <sub>HYS</sub> |                      | 200 |                      | mV    | DV <sub>DD</sub> = 3.3V only (Note 2)                                                                                                |  |  |

| Low-Level Output Voltage                                                                                                                                                                     | $V_{OL}$         |                      | 1   | 0.4                  | >     | $I_{OL}$ = +2.1 mA, $DV_{DD}$ = 3.3V                                                                                                 |  |  |

| High-Level Output Voltage                                                                                                                                                                    | $V_{OH}$         | $DV_{DD} - 0.5$      |     | _                    | ٧     | $I_{OH}$ = -2.1 mA, DV <sub>DD</sub> = 3.3V                                                                                          |  |  |

| Internal Capacitance (all inputs and outputs)                                                                                                                                                | C <sub>INT</sub> | _                    | _   | 7                    | pF    | T <sub>A</sub> = +25°C, SCK = 1.0 MHz,<br>DV <sub>DD</sub> = 3.3V ( <b>Note 1</b> )                                                  |  |  |

- **Note 1:** This parameter is periodically sampled and not 100% tested.

- 2: This parameter is established by characterization and not production tested.

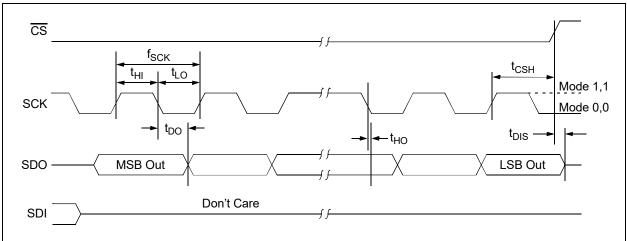

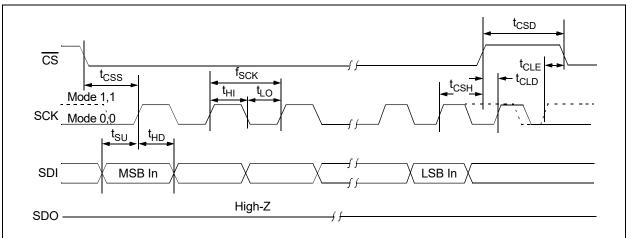

TABLE 1-3: SERIAL AC CHARACTERISTICS

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at DV<sub>DD</sub> = 2.7 to 3.6V,  $T_A = -40$ °C to +125°C, GAIN = 1,  $C_{LOAD} = 30$  pF.

| Characteristics                                   | Sym                 | Min | Тур     | Max           | Units | Test Conditions |

|---------------------------------------------------|---------------------|-----|---------|---------------|-------|-----------------|

| Serial Clock Frequency                            | f <sub>SCK</sub>    | _   | _       | 20            | MHz   |                 |

| CS Setup Time                                     | t <sub>CSS</sub>    | 25  | _       | _             | ns    |                 |

| CS Hold Time                                      | t <sub>CSH</sub>    | 50  | _       | _             | ns    |                 |

| CS Disable Time                                   | t <sub>CSD</sub>    | 50  | _       | _             | ns    |                 |

| Data Setup Time                                   | t <sub>SU</sub>     | 5   | _       | _             | ns    |                 |

| Data Hold Time                                    | $t_{HD}$            | 10  | _       |               | ns    |                 |

| Serial Clock High Time                            | t <sub>HI</sub>     | 20  | _       |               | ns    |                 |

| Serial Clock Low Time                             | $t_{LO}$            | 20  | _       |               | ns    |                 |

| Serial Clock Delay Time                           | $t_{CLD}$           | 50  | _       | _             | ns    |                 |

| Serial Clock Enable Time                          | t <sub>CLE</sub>    | 50  | _       |               | ns    |                 |

| Output Valid from SCK Low                         | t <sub>DO</sub>     | _   | _       | 25            | ns    |                 |

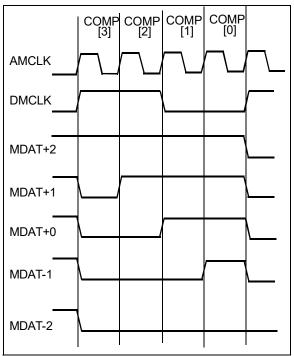

| Modulator Output<br>Valid from AMCLK High         | t <sub>DOMDAT</sub> | _   | _       | 1/(2 x AMCLK) | S     |                 |

| Output Hold Time                                  | t <sub>HO</sub>     | 0   | _       |               | ns    | Note 1          |

| Output Disable Time                               | t <sub>DIS</sub>    |     | _       | 25            | ns    | Note 1          |

| Reset Pulse Width (RESET)                         | t <sub>MCLR</sub>   | 100 | _       |               | ns    |                 |

| Data Transfer Time to DR (Data Ready)             | t <sub>DODR</sub>   |     | _       | 25            | ns    | Note 2          |

| Modulator Mode Entry to<br>Modulator Data Present | t <sub>MODSU</sub>  |     | _       | 100           | ns    |                 |

| Data Ready Pulse Low Time                         | t <sub>DRP</sub>    | _   | 1/DMCLK | <u> </u>      | μs    |                 |

- Note 1: This parameter is periodically sampled and not 100% tested.

- 2: This parameter is established by characterization and not production tested.

#### TABLE 1-4: TEMPERATURE SPECIFICATIONS

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at AV<sub>DD</sub> = 2.7 to 3.6V;  $DV_{DD} = 2.7 \text{ to } 3.6V.$ **Parameters** Sym Min Тур Max Units **Conditions Temperature Ranges Operating Temperature Range** °C  $T_A$ -40 +125 Note 1  $\mathsf{T}_\mathsf{A}$ Storage Temperature Range -65 +150 °C **Thermal Package Resistances** Thermal Resistance, 20-Lead QFN °C/W  $\theta_{JA}$ 43 Thermal Resistance, 20-Lead SSOP  $\theta_{J\underline{A}}$ 87.3 °C/W

Note 1: The internal junction temperature (T<sub>J</sub>) must not exceed the absolute maximum specification of +150°C.

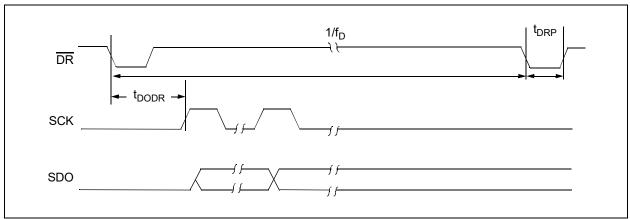

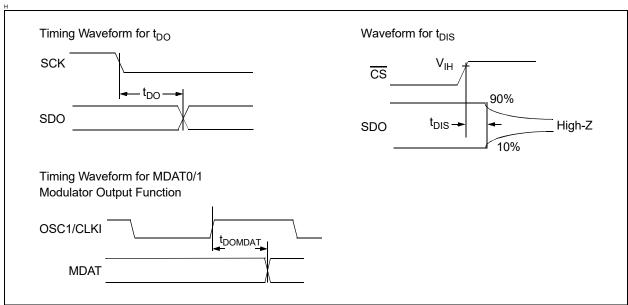

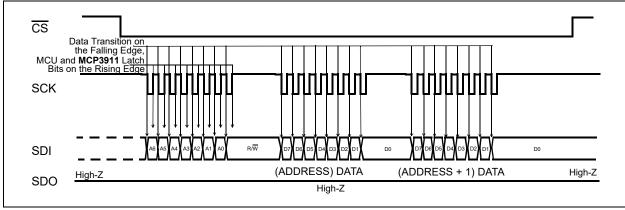

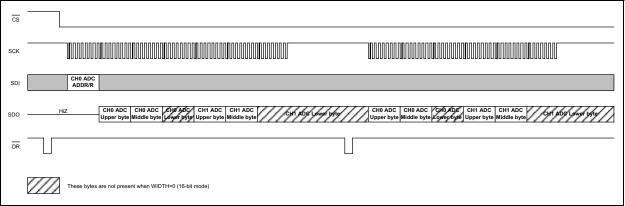

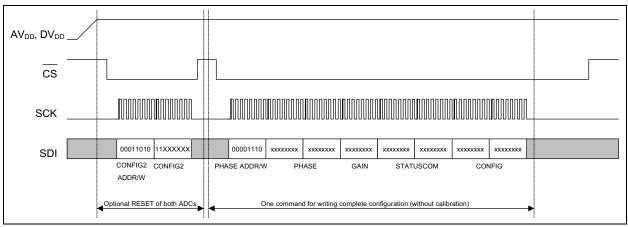

FIGURE 1-1: Serial Output Timing Diagram.

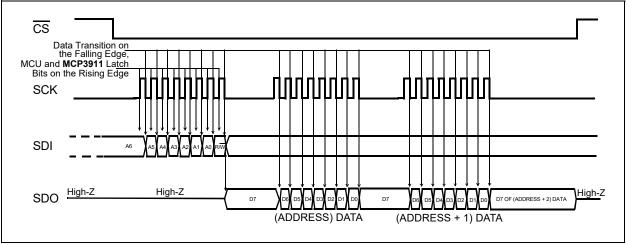

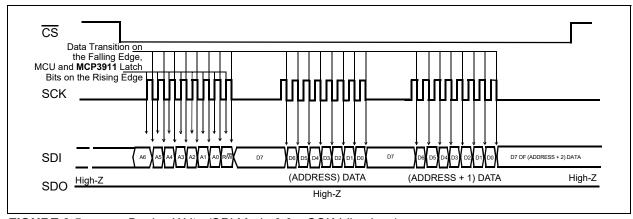

FIGURE 1-2: Serial Input Timing Diagram.

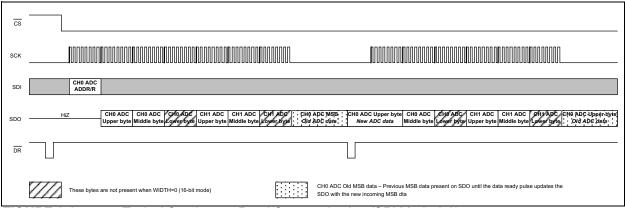

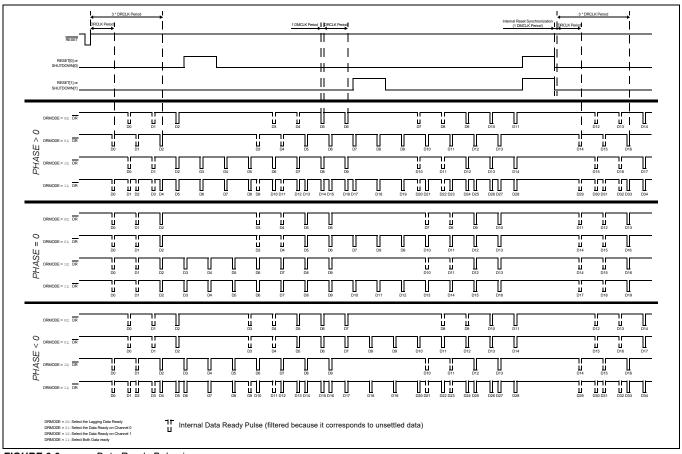

FIGURE 1-3: Data Ready Pulse/Sampling Timing Diagram.

FIGURE 1-4: Timing Diagrams (Continued).

| M | IC | <b>P</b> 3 | 9            | 1 | 1 |

|---|----|------------|--------------|---|---|

|   | •  |            | $\mathbf{v}$ |   |   |

NOTES:

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

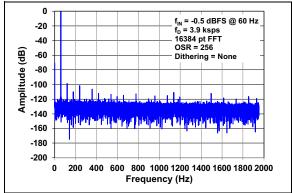

FIGURE 2-1: Spectral Response.

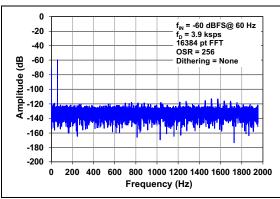

FIGURE 2-2: Spectral Response.

FIGURE 2-3: THD Histogram.

FIGURE 2-4: Spectral Response.

FIGURE 2-5: Spectral Response.

FIGURE 2-6: SINAD Histogram.

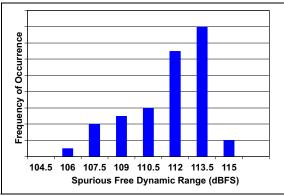

**FIGURE 2-7:** Spurious-Free Dynamic Range Histogram.

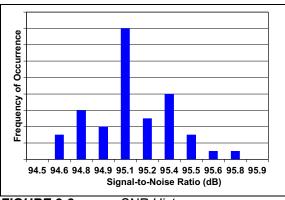

FIGURE 2-8: SNR Histogram.

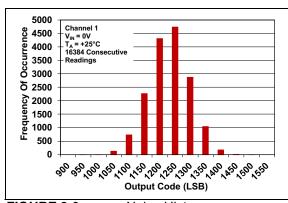

FIGURE 2-9: Noise Histogram.

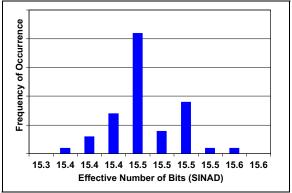

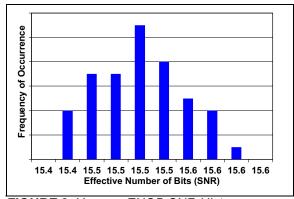

FIGURE 2-10: ENOB SINAD Histogram.

FIGURE 2-11: ENOB SNR Histogram.

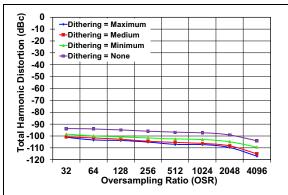

FIGURE 2-12: THD vs. OSR.

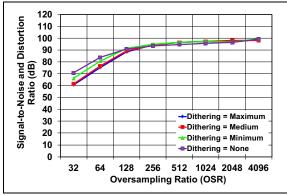

FIGURE 2-13: SINAD vs. OSR.

FIGURE 2-14: SNR vs.OSR.

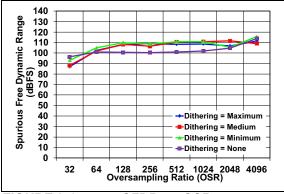

FIGURE 2-15: SFDR vs. OSR.

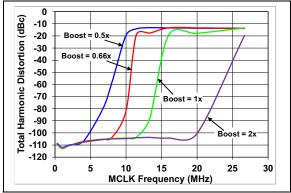

FIGURE 2-16: THD vs. MCLK.

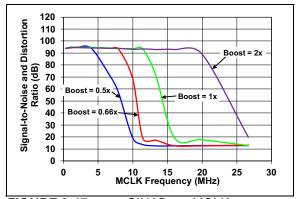

FIGURE 2-17: SINAD vs. MCLK.

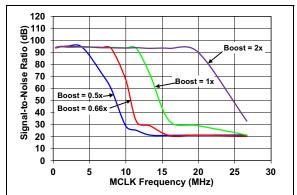

FIGURE 2-18: SNR vs. MCLK.

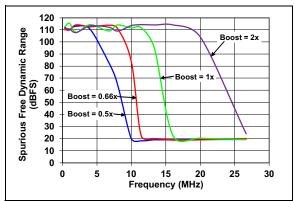

FIGURE 2-19: SFDR vs. MCLK.

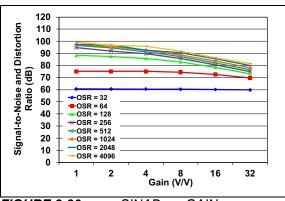

FIGURE 2-20: SINAD vs. GAIN.

FIGURE 2-21: SINAD vs. GAIN (Dithering Off).

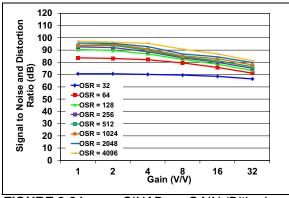

FIGURE 2-22: SINAD vs. GAIN vs. AZ Speed Chart.

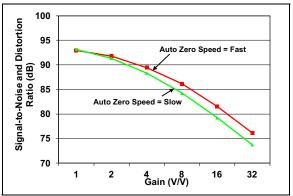

FIGURE 2-23: THD vs. Input Signal Amplitude.

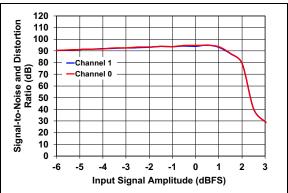

FIGURE 2-24: SINAD vs. Input Signal Amplitude.

FIGURE 2-25: SNR vs. Input Signal Amplitude.

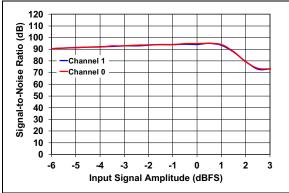

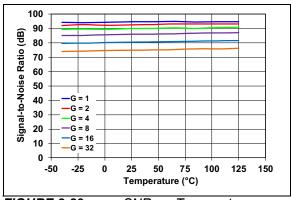

FIGURE 2-28: SINAD vs. Temperature.

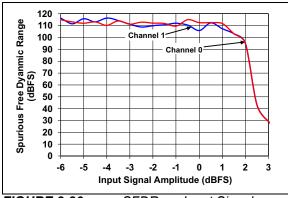

**FIGURE 2-26:** SFDR vs. Input Signal Amplitude.

FIGURE 2-29: SNR vs. Temperature.

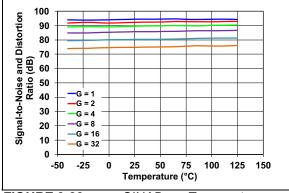

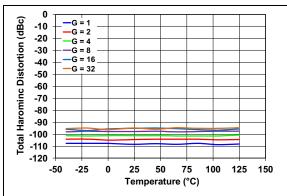

FIGURE 2-27: THD vs. Temperature.

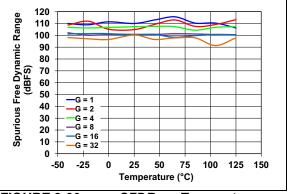

FIGURE 2-30: SFDR vs. Temperature.

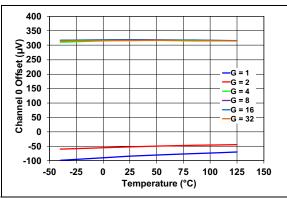

FIGURE 2-31: Channel 0 Offset vs. Temperature.

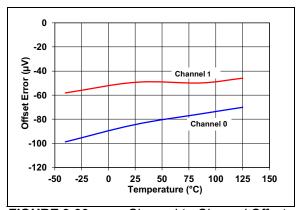

FIGURE 2-32: Channel 1 Offset vs. Temperature.

**FIGURE 2-33:** Channel-to-Channel Offset Match vs. Temperature.

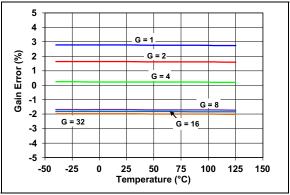

FIGURE 2-34: Gain Error vs. Temperature.

**FIGURE 2-35:** Internal Voltage Reference vs. Temperature.

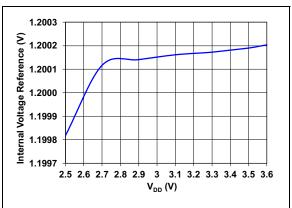

**FIGURE 2-36:** Internal Voltage Reference vs. Supply Voltage.

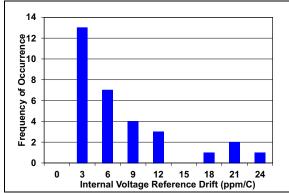

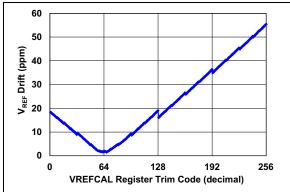

**FIGURE 2-37:** V<sub>REF</sub> Drift Data Histogram Chart.

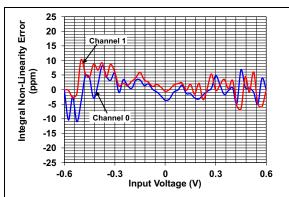

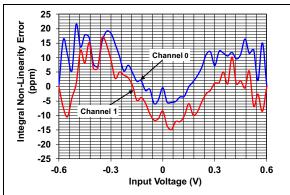

FIGURE 2-38: Integral Nonlinearity (Dithering Maximum).

FIGURE 2-39: Integral Nonlinearity (Dithering Off).

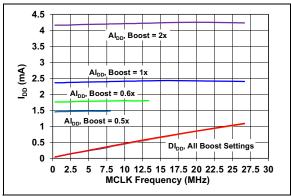

**FIGURE 2-40:** Operating Current vs. MCLK,  $V_{DD} = 3.3V$ .

**FIGURE 2-41:** Operating Current vs. MCLK,  $V_{DD} = 2.7V$ .

| N  | 10 | F | 3 | 9 | 1 | 1 |

|----|----|---|---|---|---|---|

| IV |    | , | • | J |   |   |

NOTES:

#### 3.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| Pin No.<br>SSOP | Pin No.<br>QFN | Symbol           | Function                                                                     |

|-----------------|----------------|------------------|------------------------------------------------------------------------------|

| 1               | 18             | RESET            | Master Reset Logic Input Pin                                                 |

| 2               | 19             | DV <sub>DD</sub> | Digital Power Supply Pin                                                     |

| 3               | 20             | $AV_DD$          | Analog Power Supply Pin                                                      |

| 4               | 1              | CH0+             | Noninverting Analog Input Pin for Channel 0                                  |

| 5               | 2              | CH0-             | Inverting Analog Input Pin for Channel 0                                     |

| 6               | 3              | CH1-             | Inverting Analog Input Pin for Channel 1                                     |

| 7               | 4              | CH1+             | Noninverting Analog Input Pin for Channel 1                                  |

| 8               | 5              | $A_{GND}$        | Analog Ground Pin, Return Path for Internal Analog Circuitry                 |

| 9               | 6              | REFIN+/OUT       | Noninverting Voltage Reference Input and Internal Reference Output Pin       |

| 10              | 7              | REFIN-           | Inverting Voltage Reference Input Pin                                        |

| 11              | 8              | $D_GND$          | Digital Ground Pin, Return Path for Internal Digital Circuitry               |

| 12              | 9              | MDAT1            | Modulator Data Output Pin for Channel 1                                      |

| 13              | 10             | MDAT0            | Modulator Data Output Pin for Channel 0                                      |

| 14              | 11             | DR               | Data Ready Signal Output Pin                                                 |

| 15              | 12             | OSC1/CLKI        | Oscillator Crystal Connection Pin or External Clock Input Pin                |

| 16              | 13             | OSC2             | Oscillator Crystal Connection Pin                                            |

| 17              | 14             | <u>cs</u>        | Serial Interface Chip Select Pin                                             |

| 18              | 15             | SCK              | Serial Interface Clock Input Pin                                             |

| 19              | 16             | SDO              | Serial Interface Data Input Pin                                              |

| 20              | 17             | SDI              | Serial Interface Data Input Pin                                              |

| _               | 21             | EP               | Exposed Thermal Pad. Must be connected to A <sub>GND</sub> or left floating. |

#### 3.1 Master Reset (RESET)

This pin is active-low and places the entire chip in a Reset state when active.

When  $\overline{RESET}$  =  $D_{GND}$ , all registers are reset to their default value and no communication can take place. No clock is distributed inside the part, except in the input structure, if MCLK is applied (if Idle, no clock is distributed). This state is equivalent to a POR state.

Since the default state of the ADCs is on, the analog power consumption when  $\overline{RESET} = D_{GND}$  is equivalent to  $\overline{RESET} = V_{DD}$ . Only the digital power consumption is largely reduced because this current consumption is essentially dynamic and is reduced drastically when there is no running clock.

All the analog biases are enabled during a Reset so that the part is fully operational just after a RESET rising edge, if the MCLK is applied during the rising edge. If not applied, there is a small time after RESET when the conversion may not be accurate, corresponding to the start-up of the charge pump of the input structure.

This input is Schmitt triggered.

### 3.2 Digital $V_{DD}$ (DV<sub>DD</sub>)

${\rm DV_{DD}}$  is the power supply pin for the digital circuitry within the MCP3911. For specified operation, this pin requires appropriate bypass capacitors and should be maintained between 2.7V and 3.6V.

#### 3.3 Analog $V_{DD}$ (AV<sub>DD</sub>)

${\rm AV_{DD}}$  is the power supply pin for the analog circuitry within the MCP3911. For specified operation, this pin requires appropriate bypass capacitors and should be maintained between 2.7V and 3.6V.

# 3.4 ADC Differential Analog inputs (CHn+/CHn-)

The two fully differential analog voltage inputs for the Delta-Sigma ADCs are:

- · CH0- and CH0+

- CH1- and CH1+

The linear and specified region of the channels is dependent on the PGA gain. This region corresponds to a differential voltage range of  $\pm 600$  mV/GAIN with  $V_{REF} = 1.2V$ .

The maximum differential voltage is proportional to the  $V_{REF}$  voltage. The maximum absolute voltage, with respect to  $A_{GND}$ , for each CHn+/- input pin is  $\pm 1V$  with no distortion, and  $\pm 2V$  with no breaking after continuous voltage. This maximum absolute voltage is not proportional to the  $V_{REF}$  voltage.

### 3.5 Analog Ground (A<sub>GND</sub>)

$A_{GND}$  is the ground connection to the internal analog circuitry (see the **Functional Block Diagram**). To ensure accuracy and noise cancellation, this pin must be connected to the same ground as  $D_{GND}$ , preferably with a star connection. If an analog ground plane is available, it is recommended that this pin is tied to this Printed Circuit Board (PCB) plane. This plane should also reference all other analog circuitry in the system.

### 3.6 Noninverting Reference Input, Internal Reference Output (REFIN+/OUT)

This pin is the noninverting side of the differential voltage reference input for both ADCs or the internal voltage reference output.

When VREFEXT = 1, an external voltage reference source can be used and the internal voltage reference is disabled. When using an external differential voltage reference, it should be connected to its  $V_{REF}$ + pin. When using an external single-ended reference, it should be connected to this pin.

When VREFEXT = 0, the internal voltage reference is enabled and connected to this pin through a switch. If used as a voltage source, this voltage reference has a minimal drive capability, and thus needs proper buffering and bypass capacitances. A 0.1  $\mu$ F ceramic capacitor is sufficient in most cases.

If the voltage reference is only used as an internal  $V_{REF}$ , adding bypass capacitance on REFIN+/OUT is not necessary for keeping ADC accuracy. If left floating, a minimal 0.1  $\mu F$  ceramic capacitance can be connected to avoid EMI/EMC susceptibility issues due to the antenna created by the REFIN+/OUT pin.

#### 3.7 Inverting Reference Input (REFIN-)

This pin is the inverting side of the differential voltage reference input for both ADCs. When using an external differential voltage reference, it should be connected to its  $V_{REF}$ - pin. When using an external single-ended voltage reference, or when VREFEXT = 0 (default) and using the internal voltage reference, this pin should be directly connected to  $A_{GND}$ .

#### 3.8 Digital Ground Connection (D<sub>GND</sub>)

$D_{GND}$  is the ground connection to the internal digital circuitry (see **Functional Block Diagram**). To ensure optimal accuracy and noise cancellation,  $D_{GND}$  must be connected to the same ground as  $A_{GND}$ , preferably with a star connection. If a digital ground plane is available, it is recommended that this pin is tied to this PCB plane. This plane should also reference all other digital circuitry in the system.

# 3.9 Modulator Data Output Pin for Channel 1 and Channel 0 (MDAT1/MDAT0)

MDAT0 and MDAT1 are the output pins for the modulator serial bit streams of ADC Channels 0 and 1, respectively. These pins are high-impedance when their corresponding MODOUT bit is logic low. When the MODOUT[1:0] bits are enabled, the modulator bit stream of the corresponding channel is present on the pin and updated at the AMCLK frequency (see Section 5.4 "Modulator Output Block" for a complete description of the modulator outputs). These pins can be directly connected to an MCU or a DSP when a specific digital filtering is needed.

### 3.10 Data Ready Output (DR)

The Data Ready pin indicates that a new conversion result is ready to be read. The default state of this pin is high when  $\overline{DR}$ —HIZ = 1 and is high-impedance when  $\overline{DR}$ —HIZ = 0 (default). After each conversion is finished, a logic low pulse takes place on the Data Ready pin to indicate that the conversion result is ready as an interrupt. This pulse is synchronous with the master clock and has a defined and constant width.

The Data Ready pin is independent of the SPI interface and acts like an interrupt output. The Data Ready pin state is not latched and the pulse width (and period) are both determined by the MCLK frequency oversampling rate and internal clock prescale settings. The  $\overline{DR}$  pulse width is equal to one DMCLK period and the frequency of the pulses is equal to DRCLK (see Figure 1-3).

Note: This pin should not be left floating when the  $\overline{DR\_HIZ}$  bit is low; a 100 k $\Omega$  pull-up resistor connected to  $\overline{DV_{DD}}$  is recommended.

# 3.11 Oscillator and Master Clock Input Pins (OSC1/CLKI, OSC2)

OSC1/CLKI and OSC2 provide the Master Clock (MCLK) for the device. When CLKEXT = 0, a resonant crystal or clock source with a similar sinusoidal waveform must be placed across these pins to ensure proper operation. The typical clock frequency specified is 4 MHz. For proper operation and optimizing ADC accuracy, AMCLK should be limited to the maximum frequency defined in Table 5-3 as a function of the BOOST and PGA settings chosen. MCLK can take larger values as long as the prescaler settings (PRE[1:0]) limit AMCLK = MCLK/PRESCALE in the defined range in Table 5-3. For proper operation, appropriate load capacitance should be connected to these pins.

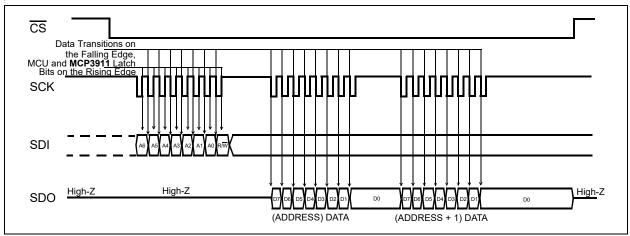

### 3.12 Chip Select (CS)

This pin is the SPI chip select that enables the serial communication. When this pin is high, no communication can take place. A chip select falling edge initiates the serial communication and a chip select rising edge terminates the communication. No communication can take place when  $\overline{\text{CS}}$  is low or when  $\overline{\text{RESET}}$  is low.

This input is Schmitt triggered.

#### 3.13 Serial Data Clock (SCK)

This is the serial clock pin for SPI communication.

Data are clocked into the device on the RISING edge and out of the device on the FALLING edge of SCK.

The MCP3911 interface is compatible with both SPI 0,0 and 1,1 modes. SPI modes can be changed during a  $\overline{\text{CS}}$  high time.

The maximum clock speed specified is 20 MHz.

This input is Schmitt triggered.

#### 3.14 Serial Data Output (SDO)

This is the SPI data output pin. Data are clocked out of the device on the FALLING edge of SCK.

This pin stays high-impedance during the first command byte. It also stays high-impedance during the whole communication for write commands and when the  $\overline{\text{CS}}$  pin is high or when the  $\overline{\text{RESET}}$  pin is low. This pin is active only when a read command is processed. Each read is processed by packet of eight bits.

#### 3.15 Serial Data Input (SDI)

This is the SPI data input pin. Data are clocked into the device on the RISING edge of SCK.

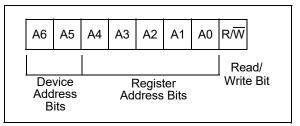

When  $\overline{CS}$  is low, this pin is used to communicate with a series of 8-bit commands.

The interface is half-duplex (inputs and outputs do not happen at the same time).

Each communication starts with a chip select falling edge, followed by an 8-bit command word entered through the SDI pin. Each command is either a read or write command. Toggling SDI during a read command has no effect.

This input is Schmitt triggered.

| M | IC | <b>P</b> 3 | 9            | 1 | 1 |

|---|----|------------|--------------|---|---|

|   | •  |            | $\mathbf{v}$ |   |   |

NOTES:

# 4.0 TERMINOLOGIES AND FORMULAS

This section defines the terms and formulas used throughout this data sheet. The following terms are defined:

- MCLK Master Clock

- AMCLK Analog Master Clock

- DMCLK Digital Master Clock

- DRCLK Data Rate Clock

- OSR Oversampling Ratio

- Offset Error

- Gain Error

- Integral Nonlinearity Error

- Signal-to-Noise Ratio (SNR)

- Signal-to-Noise Ratio and Distortion (SINAD)

- Total Harmonic Distortion (THD)

- Spurious-Free Dynamic Range (SFDR)

- MCP3911 Delta-Sigma Architecture

- Idle Tones

- Dithering

- Crosstalk

- PSRR

- CMRR

- ADC Reset Mode

- Hard Reset Mode (RESET = DGND)

- ADC Shutdown Mode

- Full Shutdown Mode

#### 4.1 MCLK - Master Clock

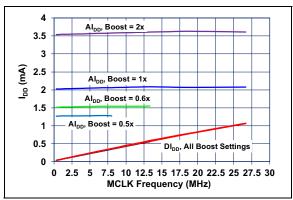

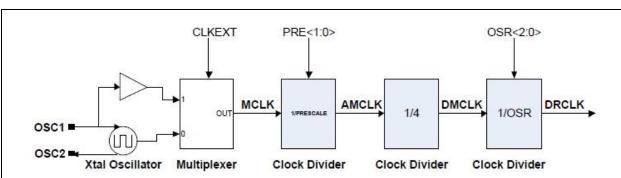

This is the fastest clock present in the device. This is the frequency of the crystal placed at the OSC1/OSC2 inputs when CLKEXT = 0 or the frequency of the clock input at the OSC1/CLKI when CLKEXT = 1. See Figure 4-1.

#### 4.2 AMCLK – Analog Master Clock

This is the clock frequency that is present on the analog portion of the device after prescaling has occurred via the CONFIG PRE[1:0] register bits. The analog portion includes the PGAs and the two Delta-Sigma modulators.

$$AMCLK = \frac{MCLK}{PRESCALE}$$

TABLE 4-1: MCP3911 OVERSAMPLING RATIO SETTINGS

| Config |       | Analog Master Clock      |  |

|--------|-------|--------------------------|--|

| PRE    | [1:0] | Prescale                 |  |

| 0      | 0     | AMCLK = MCLK/1 (default) |  |

| 0      | 1     | AMCLK = MCLK/2           |  |

| 1      | 0     | AMCLK = MCLK/4           |  |

| 1      | 1     | AMCLK = MCLK/8           |  |

FIGURE 4-1: Clock Sub-Circuitry.

#### 4.3 DMCLK - Digital Master Clock

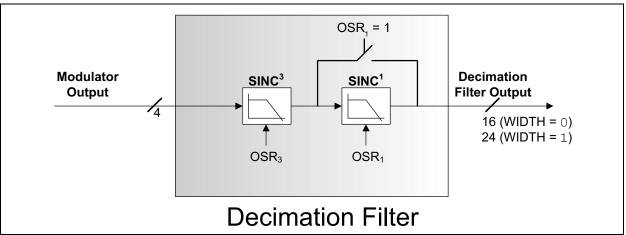

This is the clock frequency that is present on the digital portion of the device after prescaling and division by four. This is also the sampling frequency, which is the rate at which the modulator outputs are refreshed. Each period of this clock corresponds to one sample and one modulator output. See Figure 4-1.

#### **EQUATION 4-1:**

$$DMCLK = \frac{AMCLK}{4} = \frac{MCLK}{4 \times PRESCALE}$$

#### 4.4 DRCLK – Data Rate Clock

This is the output data rate (i.e., the rate at which the ADCs output new data). New data are signaled by a data ready pulse on the  $\overline{DR}$  pin.

This data rate is dependent on the OSR and the prescaler with the following formula:

#### **EQUATION 4-2:**

$$DRCLK = \frac{DMCLK}{OSR} = \frac{AMCLK}{4 \times OSR} = \frac{MCLK}{4 \times OSR \times PRESCALE}$$

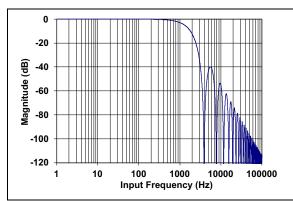

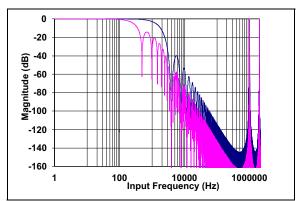

Since this is the output data rate and the decimation filter is a SINC (or notch) filter, there is a notch in the filter transfer function at each integer multiple of this rate.

The following table describes the various combinations of OSR and PRESCALE and their associated AMCLK, DMCLK and DRCLK rates.

TABLE 4-2: DEVICE DATA RATES IN FUNCTION OF MCLK, OSR AND PRESCALE, MCLK = 4 MHz

| PRE | [1:0] | 0 | SR[2: | 0] | OSR  | AMCLK  | DMCLK   | DRCLK       | DRCLK<br>(ksps) | SINAD<br>(dB) <sup>(1)</sup> | ENOB from<br>SINAD<br>(bits) <sup>(1)</sup> |

|-----|-------|---|-------|----|------|--------|---------|-------------|-----------------|------------------------------|---------------------------------------------|

| 1   | 1     | 1 | 1     | 1  | 4096 | MCLK/8 | MCLK/32 | MCLK/131072 | 0.035           | 98                           | 16                                          |

| 1   | 1     | 1 | 1     | 1  | 2048 | MCLK/8 | MCLK/32 | MCLK/65536  | 0.061           | 98                           | 16                                          |

| 1   | 1     | 1 | 1     | 1  | 1024 | MCLK/8 | MCLK/32 | MCLK/32768  | 0.122           | 97                           | 15.8                                        |

| 1   | 1     | 1 | 1     | 1  | 512  | MCLK/8 | MCLK/32 | MCLK/16384  | 0.244           | 96                           | 15.6                                        |

| 1   | 1     | 0 | 1     | 1  | 256  | MCLK/8 | MCLK/32 | MCLK/8192   | 0.488           | 95                           | 15.5                                        |

| 1   | 1     | 0 | 1     | 0  | 128  | MCLK/8 | MCLK/32 | MCLK/4096   | 0.976           | 90                           | 14.7                                        |

| 1   | 1     | 0 | 0     | 1  | 64   | MCLK/8 | MCLK/32 | MCLK/2048   | 1.95            | 83                           | 13.5                                        |

| 1   | 1     | 0 | 0     | 0  | 32   | MCLK/8 | MCLK/32 | MCLK/1024   | 3.9             | 70                           | 11.3                                        |

| 1   | 0     | 1 | 1     | 1  | 4096 | MCLK/4 | MCLK/16 | MCLK/65536  | 0.061           | 98                           | 16                                          |

| 1   | 0     | 1 | 1     | 1  | 2048 | MCLK/4 | MCLK/16 | MCLK/32768  | 0.122           | 98                           | 16                                          |

| 1   | 0     | 1 | 1     | 1  | 1024 | MCLK/4 | MCLK/16 | MCLK/16384  | 0.244           | 97                           | 15.8                                        |

| 1   | 0     | 1 | 1     | 1  | 512  | MCLK/4 | MCLK/16 | MCLK/8192   | 0.488           | 96                           | 15.6                                        |

| 1   | 0     | 0 | 1     | 1  | 256  | MCLK/4 | MCLK/16 | MCLK/4096   | 0.976           | 95                           | 15.5                                        |

| 1   | 0     | 0 | 1     | 0  | 128  | MCLK/4 | MCLK/16 | MCLK/2048   | 1.95            | 90                           | 14.7                                        |

| 1   | 0     | 0 | 0     | 1  | 64   | MCLK/4 | MCLK/16 | MCLK/1024   | 3.9             | 83                           | 13.5                                        |

| 1   | 0     | 0 | 0     | 0  | 32   | MCLK/4 | MCLK/16 | MCLK/512    | 7.8125          | 70                           | 11.3                                        |

| 0   | 1     | 1 | 1     | 1  | 4096 | MCLK/2 | MCLK/8  | MCLK/32768  | 0.122           | 98                           | 16                                          |

| 0   | 1     | 1 | 1     | 1  | 2048 | MCLK/2 | MCLK/8  | MCLK/16384  | 0.244           | 98                           | 16                                          |

| 0   | 1     | 1 | 1     | 1  | 1024 | MCLK/2 | MCLK/8  | MCLK/8192   | 0.488           | 97                           | 15.8                                        |

| 0   | 1     | 1 | 1     | 1  | 512  | MCLK/2 | MCLK/8  | MCLK/4096   | 0.976           | 96                           | 15.6                                        |

| 0   | 1     | 0 | 1     | 1  | 256  | MCLK/2 | MCLK/8  | MCLK/2048   | 1.95            | 95                           | 15.5                                        |

| 0   | 1     | 0 | 1     | 0  | 128  | MCLK/2 | MCLK/8  | MCLK/1024   | 3.9             | 90                           | 14.7                                        |

| 0   | 1     | 0 | 0     | 1  | 64   | MCLK/2 | MCLK/8  | MCLK/512    | 7.8125          | 83                           | 13.5                                        |

| 0   | 1     | 0 | 0     | 0  | 32   | MCLK/2 | MCLK/8  | MCLK/256    | 15.625          | 70                           | 11.3                                        |

| 0   | 0     | 1 | 1     | 1  | 4096 | MCLK   | MCLK/4  | MCLK/16384  | 0.244           | 98                           | 16                                          |

| 0   | 0     | 1 | 1     | 0  | 2048 | MCLK   | MCLK/4  | MCLK/8192   | 0.488           | 98                           | 16                                          |

| 0   | 0     | 1 | 0     | 1  | 1024 | MCLK   | MCLK/4  | MCLK/4096   | 0.976           | 97                           | 15.8                                        |

| 0   | 0     | 1 | 0     | 0  | 512  | MCLK   | MCLK/4  | MCLK/2048   | 1.95            | 96                           | 15.6                                        |

| 0   | 0     | 0 | 1     | 1  | 256  | MCLK   | MCLK/4  | MCLK/1024   | 3.9             | 95                           | 15.5                                        |

| 0   | 0     | 0 | 1     | 0  | 128  | MCLK   | MCLK/4  | MCLK/512    | 7.8125          | 90                           | 14.7                                        |

| 0   | 0     | 0 | 0     | 1  | 64   | MCLK   | MCLK/4  | MCLK/256    | 15.625          | 83                           | 13.5                                        |

| 0   | 0     | 0 | 0     | 0  | 32   | MCLK   | MCLK/4  | MCLK/128    | 31.25           | 70                           | 11.3                                        |

**Note 1:** For OSR = 32 and 64, DITHER = None. For OSR = 128 and higher, DITHER = Maximum. The SINAD values are given from GAIN = 1.

#### 4.5 OSR – Oversampling Ratio

This is the ratio of the sampling frequency to the output data rate. OSR = DMCLK/DRCLK. The default OSR is 256 or with MCLK = 4 MHz, PRESCALE = 1, AMCLK = 4 MHz,  $f_S$  = 1 MHz,  $f_D$  = 3.90625 ksps. The following bits in the CONFIG register are used to change the Oversampling Ratio (OSR).

TABLE 4-3: MCP3911 OVERSAMPLING RATIO SETTINGS

|   | CONFIG   |   | Oversampling Ratio (OSR) |  |

|---|----------|---|--------------------------|--|

|   | OSR[2:0] |   | (OOI)                    |  |

| 0 | 0        | 0 | 32                       |  |

| 0 | 0        | 1 | 64                       |  |

| 0 | 1        | 0 | 128                      |  |

| 0 | 1        | 1 | 256 (default)            |  |

| 1 | 0        | 0 | 512                      |  |

| 1 | 0        | 1 | 1024                     |  |

| 1 | 1        | 0 | 2048                     |  |

| 1 | 1 1 1    |   | 4096                     |  |

#### 4.6 Offset Error

This is the error induced by the ADC when the inputs are shorted together ( $V_{IN}=0V$ ). The specification incorporates both PGA and ADC offset contributions. This error varies with PGA and OSR settings. The offset is different on each channel and varies from chipto-chip. The offset is specified in  $\mu V$ . The offset error can be digitally compensated independently on each channel through the OFFCAL registers with a 24-bit Calibration Word.

The offset on the MCP3911 has a low temperature coefficient (see **Section 2.0**, **Typical Performance Curves** for more information, see Figure 2-33).

#### 4.7 Gain Error

This is the error induced by the ADC on the slope of the transfer function. It is the deviation expressed in percentage (%) compared to the ideal transfer function defined by Equation 5-3. The specification incorporates both PGA and ADC gain error contributions, but not the  $V_{\mbox{\scriptsize REF}}$  contribution (it is measured with an external  $V_{\mbox{\scriptsize REF}}$ ).

This error varies with PGA and OSR settings. The gain error can be digitally compensated independently on each channel through the GAINCAL registers with a 24-bit Calibration Word.

The gain error on the MCP3911 has a low temperature coefficient. For more information, see Figure 2-34.

#### 4.8 Integral Nonlinearity Error

Integral nonlinearity error is the maximum deviation of an ADC transition point from the corresponding point of an ideal transfer function, with the offset and gain errors removed or with the end points equal to zero.

It is the maximum remaining error after the calibration of offset and gain errors for a DC input signal.

#### 4.9 Signal-to-Noise Ratio (SNR)

For the MCP3911 ADCs, the Signal-to-Noise Ratio is a ratio of the output fundamental signal power to the noise power (not including the harmonics of the signal), when the input is a sine wave at a predetermined frequency. It is measured in dB. Usually, only the maximum Signal-to-Noise Ratio is specified. The SNR figure depends mainly on the OSR and DITHER settings of the device.

#### **EQUATION 4-3: SIGNAL-TO-NOISE RATIO**

$$SNR(dB) = 10log\left(\frac{SignalPower}{NoisePower}\right)$$

# 4.10 Signal-to-Noise Ratio and Distortion (SINAD)

The most important figure of merit for the analog performance of the ADCs present on the MCP3911 is the Signal-to-Noise Ratio and Distortion (SINAD) specification.

Signal-to-Noise and Distortion Ratio is similar to Signal-to-Noise Ratio, with the exception that you must include the harmonics power in the noise power calculation. The SINAD specification depends mainly on the OSR and DITHER settings.

#### **EQUATION 4-4: SINAD EQUATION**

$$SINAD(dB) = 10log\left(\frac{SignalPower}{Noise + HarmonicsPower}\right)$$

The calculated combination of SNR and THD per the following formula also yields SINAD:

# EQUATION 4-5: SINAD, THD AND SNR RELATIONSHIP

$$SINAD(dB) = 10log \left[ 10^{\left(\frac{SNR}{10}\right)} + 10^{\left(\frac{-THD}{10}\right)} \right]$$

#### 4.11 Total Harmonic Distortion (THD)

The Total Harmonic Distortion is the ratio of the output harmonics power to the fundamental signal power for a sine wave input and is defined by Equation 4-6.

#### **EQUATION 4-6:**

$$THD(dB) = 10log(\frac{HarmonicsPower}{FundamentalPower})$$

The THD calculation includes the first 35 harmonics for the MCP3911 specifications. The THD is usually only measured with respect to the first ten harmonics. THD is sometimes expressed in percentage (%). Equation 4-7 converts the THD in percentage (%):

#### **EQUATION 4-7:**

$$THD(\%) = 100 \times 10^{\frac{THD(dB)}{20}}$$

This specification depends mainly on the DITHER setting.

# 4.12 Spurious-Free Dynamic Range (SFDR)

The ratio between the output power of the fundamental and the highest spur in the frequency spectrum. The spur frequency is not necessarily a harmonic of the fundamental, even though that is usually the case. This figure represents the dynamic range of the ADC when a full-scale signal is used at the input. This specification depends mainly on the DITHER setting.

#### **EQUATION 4-8:**

$$SFDR(dB) = 10log\left(\frac{FundamentalPower}{HighestSpurPower}\right)$$

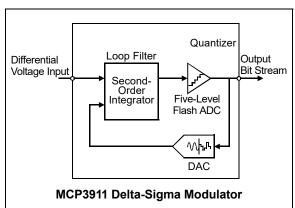

# 4.13 MCP3911 Delta-Sigma Architecture

The MCP3911 incorporates two Delta-Sigma ADCs with a multibit architecture. A Delta-Sigma ADC is an oversampling converter that incorporates a built-in modulator, which is digitizing the quantity of charge integrated by the modulator loop (see Figure 5-1). The quantizer is the block that is performing the Analog-to-Digital conversion. The quantizer is typically one bit or a simple comparator which helps to maintain the linearity performance of the ADC (the DAC structure in this case is inherently linear).

Multibit quantizers help lower the quantization error (the error fed back in the loop can be very large with 1-bit quantizers) without changing the order of the modulator or the OSR, which leads to better SNR figures. However, typically, the linearity of such architectures is more difficult to achieve since the DAC is complicated and its linearity limits the THD of such ADCs.

The MCP3911's five-level quantizer is a Flash ADC composed of four comparators, arranged with equally spaced thresholds and a thermometer coding. The MCP3911 also includes proprietary five-level DAC architecture that is inherently linear for improved THD figures.

#### 4.14 Idle Tones

A Delta-Sigma converter is an integrating converter. It also has a finite quantization step Least Significant Byte (LSB) which can be detected by its quantizer. A DC input voltage that is below the quantization step should only provide an all zeros result, since the input is not large enough to be detected. As an integrating device, any Delta-Sigma shows Idle tones in this case. This means that the output will have spurs in the frequency content that are depending on the ratio between quantization step voltage and the input voltage. These spurs are the result of the integrated sub-quantization step inputs that eventually cross the quantization steps after a long enough integration. This induces an AC frequency at the output of the ADC and can be shown in the ADC output spectrum.

These Idle tones are residues that are inherent to the quantization process and the fact that the converter is integrating at all times without being reset. They are residues of the finite resolution of the conversion process. They are very difficult to attenuate and they are heavily signal-dependent. They can degrade both SFDR and THD of the converter, even for DC inputs. They can be localized in the baseband of the converter and thus difficult to filter from the actual input signal.

For power metering applications, Idle tones can be very disturbing because energy can be detected even at the 50 or 60 Hz frequency, depending on the DC offset of the ADCs, while no power is really present at the inputs. The only practical way to suppress or attenuate Idle tones phenomenon is to apply dithering to the ADC. The Idle tone amplitudes are a function of the order of the modulator, the OSR and the number of levels in the quantizer of the modulator. A higher order, a higher OSR or a higher number of levels for the quantizer attenuate the Idle tones amplitude.

#### 4.15 Dithering

To suppress or attenuate the Idle tones present in any Delta-Sigma ADCs, dithering can be applied to the ADC. Dithering is the process of adding an error to the ADC feedback loop to "decorrelate" the outputs and "break" the Idle tone behavior. Usually, a random or pseudorandom generator adds an analog or digital error to the feedback loop of the Delta-Sigma ADC to ensure that no tonal behavior can happen at its outputs. This error is filtered by the feedback loop and typically has a zero average value, so that the converter static transfer function is not disturbed by the dithering process. However, the dithering process slightly increases the noise floor (it adds noise to the part) while reducing its tonal behavior, and thus improving SFDR and THD (see Figure 2-14 and Figure 2-18). The dithering process scrambles the Idle tones into baseband white noise and ensures that dynamic specs (SNR, SINAD, THD, SFDR) are less signal-dependent. The MCP3911 incorporates a proprietary dithering algorithm on both ADCs to remove Idle tones and improve THD, which is crucial for power metering applications.

#### 4.16 Crosstalk

The crosstalk is defined as the perturbation caused by one ADC channel on the other ADC channel. It is a measurement of the isolation between the two ADCs present in the chip.

This measurement is a two-step procedure:

- Measure one ADC input with no perturbation on the other ADC (ADC inputs shorted).

- Measure the same ADC input with a perturbation sine wave signal on the other ADC at a certain predefined frequency.

The crosstalk is then the ratio between the output power of the ADC when the perturbation is present and when it is not divided by the power of the perturbation signal.

A lower crosstalk value implies more independence and isolation between the two channels.

The measurement of this signal is performed under the default conditions at MCLK = 4 MHz:

- GAIN = 1

- PRESCALE = 1

- OSR = 256

- MCLK = 4 MHz

#### Step 1

- CH0+ = CH0- = A<sub>GND</sub>

- CH1+ = CH1- = A<sub>GND</sub>

#### Step 2

- CH0+ = CH0- = A<sub>GND</sub>

- CH1+ CH1- = 1.2 V<sub>P-P</sub> at 50/60 Hz (full-scale sine wave)

The crosstalk is then calculated with the following formula:

#### **EQUATION 4-9:**

$$CTalk(dB) = 10log\left(\frac{\Delta CH0Power}{\Delta CH1Power}\right)$$

#### 4.17 **PSRR**

This is the ratio between a change in the power supply voltage and the ADC output codes. It measures the influence of the power supply voltage on the ADC outputs.

The PSRR specification can be DC (the power supply is taking multiple DC values) or AC (the power supply is a sine wave at a certain frequency with a certain Common-mode). In AC, the amplitude of the sine wave is representing the change in the power supply. It is defined in Equation 4-10:

#### **EQUATION 4-10:**

$$PSRR(dB) = 20log\left(\frac{\Delta V_{OUT}}{\Delta A V_{DD}}\right)$$

Where  $V_{OUT}$  is the equivalent input voltage that the output code translates to the ADC transfer function. In the MCP3911 specification, AV<sub>DD</sub> varies from 2.7V to 3.6V. For AC PSRR, a 50/60 Hz sine wave is chosen, centered around 3.3V with a maximum 300 mV amplitude. The PSRR specification is measured with AV<sub>DD</sub> = DV<sub>DD</sub>.

#### 4.18 CMRR

This is the ratio between a change in the Common-mode input voltage and the ADC output codes. It measures the influence of the Common-mode input voltage on the ADC outputs.

The CMRR specification can be DC (the Common-mode input voltage is taking multiple DC values) or AC (the Common-mode input voltage is a sine wave at a certain frequency with a certain Common-mode). In AC, the amplitude of the sine wave is representing the change in the power supply. It is defined in Equation 4-11:

#### **EQUATION 4-11:**

$$CMRR(dB) = 20log\left(\frac{\Delta V_{OUT}}{\Delta V_{CM}}\right)$$

Where  $V_{CM}$  = (CHn+ + CHn-)/2 is the Common-mode input voltage and  $V_{OUT}$  is the equivalent input voltage that the output code translates to using the ADC transfer function. In the MCP3911 specification,  $V_{CM}$  varies from -1V to +1V.

#### 4.19 ADC Reset Mode

ADC Reset mode (also called Soft Reset mode) can only be entered through setting the RESET[1:0] bits in the Configuration register high. This mode is defined as the condition where the converters are active, but their output is forced to '0'.

The registers are not affected in this Reset mode and retain their state, except the data registers of the corresponding channel, which are reset to '0'.

The ADCs can immediately output meaningful codes after leaving the Reset mode (and after the SINC filter settling time). This mode is both entered and exited through the setting of bits in the Configuration register.

Each converter can be placed in Soft Reset mode independently. The Configuration registers are not modified by the Soft Reset mode.

A data ready pulse is not generated by any ADC while in Reset mode.

Reset mode also affects the modulator output block (i.e., the MDAT pin corresponding to the channel in Reset). If enabled, it provides a bit stream corresponding to a zero output (a series of '0011' bits continuously repeated).

When an ADC exits the ADC Reset mode, any phase delay present before Reset was entered is still present. If one ADC is not in Reset mode, the ADC leaving the Reset mode automatically resynchronizes the phase delay relative to the other ADC channel, per the Phase Delay register block, and gives data ready pulses accordingly.

If an ADC is placed in Reset mode while the other is converting, it is not shutting down the internal clock. When going back out of Reset, it is automatically resynchronized with the clock that did not stop during Reset.

If both ADCs are in Soft Reset, the clock is no longer distributed to the digital core for low-power operation. Once any of the ADCs is back to normal operation, the clock is automatically distributed again.

However, when the two channels are in Soft Reset, the input structure is still clocking if MCLK is applied to properly bias the inputs so that no leakage current is observed. If MCLK is not applied, large analog input leakage currents can be observed for highly negative input voltages (typically below -0.6V, referred to A<sub>GND</sub>).

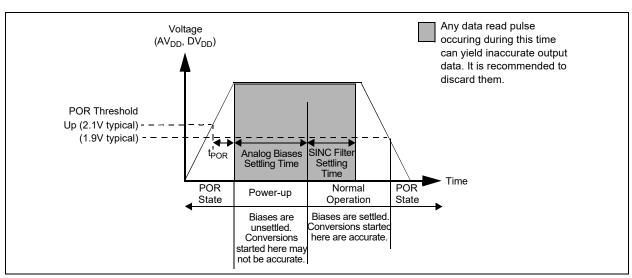

### 4.20 Hard Reset Mode (RESET = D<sub>GND</sub>)

This mode is only available during a POR or when the RESET pin is pulled low. The RESET pin low state places the device in a Hard Reset mode.

In this mode, all internal registers are reset to their default state.