## Product Change Notification / SYST-09WTKU988

# Date:

11-Nov-2021

# **Product Category:**

32-bit Microcontrollers

## **PCN Type:**

**Document Change**

## **Notification Subject:**

ERRATA - PIC32MM0256GPM064 Family Silicon Errata and Data Sheet Clarification

## Affected CPNs:

SYST-09WTKU988\_Affected\_CPN\_11112021.pdf SYST-09WTKU988\_Affected\_CPN\_11112021.csv

# **Notification Text:**

SYST-09WTKU988

Microchip has released a new Product Documents for the PIC32MM0256GPM064 Family Silicon Errata and Data Sheet Clarification of devices. If you are using one of these devices please read the document located at PIC32MM0256GPM064 Family Silicon Errata and Data Sheet Clarification.

Notification Status: Final

Description of Change: 27. Module: Comparator

Impacts to Data Sheet: None

Reason for Change: To Improve Productivity

Change Implementation Status: Complete

Date Document Changes Effective: 11 Nov 2021

NOTE: Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

# Attachments:

PIC32MM0256GPM064 Family Silicon Errata and Data Sheet Clarification

Please contact your local Microchip sales office with questions or concerns regarding this notification.

## Terms and Conditions:

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our PCN home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the PCN FAQ section.

If you wish to <u>change your PCN profile</u>, <u>including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections. Affected Catalog Part Numbers (CPN)

PIC32MM0064GPM028-E/M6 PIC32MM0064GPM028-E/ML PIC32MM0064GPM028-E/SS PIC32MM0064GPM028-I/M6 PIC32MM0064GPM028-I/ML PIC32MM0064GPM028-I/SS PIC32MM0064GPM028T-I/M6 PIC32MM0064GPM028T-I/ML PIC32MM0064GPM028T-I/SS PIC32MM0064GPM036-E/M2 PIC32MM0064GPM036-E/MV PIC32MM0064GPM036-I/M2 PIC32MM0064GPM036-I/MV PIC32MM0064GPM036T-I/M2 PIC32MM0064GPM036T-I/MV PIC32MM0064GPM048-E/M4 PIC32MM0064GPM048-E/PT PIC32MM0064GPM048-I/M4 PIC32MM0064GPM048-I/PT PIC32MM0064GPM048T-I/M4 PIC32MM0064GPM048T-I/PT PIC32MM0064GPM064-E/MR PIC32MM0064GPM064-E/PT PIC32MM0064GPM064-E/PTVAO PIC32MM0064GPM064-I/MR PIC32MM0064GPM064-I/PT PIC32MM0064GPM064T-I/MR PIC32MM0064GPM064T-I/PT PIC32MM0128GPM028-E/M6 PIC32MM0128GPM028-E/ML PIC32MM0128GPM028-E/SS PIC32MM0128GPM028-I/M6 PIC32MM0128GPM028-I/ML PIC32MM0128GPM028-I/SS PIC32MM0128GPM028T-I/M6 PIC32MM0128GPM028T-I/ML PIC32MM0128GPM028T-I/SS PIC32MM0128GPM036-E/M2 PIC32MM0128GPM036-E/MV PIC32MM0128GPM036-I/M2 PIC32MM0128GPM036-I/MV PIC32MM0128GPM036T-I/M2 PIC32MM0128GPM036T-I/MV PIC32MM0128GPM048-E/M4 PIC32MM0128GPM048-E/PT PIC32MM0128GPM048-I/M4

PIC32MM0128GPM048-I/PT PIC32MM0128GPM048T-I/M4 PIC32MM0128GPM048T-I/PT PIC32MM0128GPM064-E/MR PIC32MM0128GPM064-E/MRVAO PIC32MM0128GPM064-E/PT PIC32MM0128GPM064-I/MR PIC32MM0128GPM064-I/PT PIC32MM0128GPM064T-I/MR PIC32MM0128GPM064T-I/PT PIC32MM0256GPM028-E/M6 PIC32MM0256GPM028-E/ML PIC32MM0256GPM028-E/SS PIC32MM0256GPM028-E/SSVAO PIC32MM0256GPM028-I/M6 PIC32MM0256GPM028-I/ML PIC32MM0256GPM028-I/MLVAO PIC32MM0256GPM028-I/SS PIC32MM0256GPM028T-I/M6 PIC32MM0256GPM028T-I/ML PIC32MM0256GPM028T-I/ML026 PIC32MM0256GPM028T-I/ML028 PIC32MM0256GPM028T-I/MLVAO PIC32MM0256GPM028T-I/SS PIC32MM0256GPM036-E/M2 PIC32MM0256GPM036-E/MV PIC32MM0256GPM036-I/M2 PIC32MM0256GPM036-I/MV PIC32MM0256GPM036T-I/M2 PIC32MM0256GPM036T-I/MV PIC32MM0256GPM036T-I/MVC36 PIC32MM0256GPM048-E/M4 PIC32MM0256GPM048-E/PT PIC32MM0256GPM048-I/M4 PIC32MM0256GPM048-I/PT PIC32MM0256GPM048T-I/M4 PIC32MM0256GPM048T-I/M4C48 PIC32MM0256GPM048T-I/M4D48 PIC32MM0256GPM048T-I/PT PIC32MM0256GPM048T-I/PT027 PIC32MM0256GPM048T-I/PT029 PIC32MM0256GPM048T-I/PT030 PIC32MM0256GPM048T-I/PT033 PIC32MM0256GPM064-E/MR PIC32MM0256GPM064-E/PT PIC32MM0256GPM064-I/MR PIC32MM0256GPM064-I/PT PIC32MM0256GPM064-I/PTV01 PIC32MM0256GPM064T-E/MR035

PIC32MM0256GPM064T-E/MR036 PIC32MM0256GPM064T-I/MR PIC32MM0256GPM064T-I/MR035 PIC32MM0256GPM064T-I/MR036 PIC32MM0256GPM064T-I/PT023 PIC32MM0256GPM064T-I/PT025 PIC32MM0256GPM064T-I/PT034 PIC32MM0256GPM064T-I/PTC21 PIC32MM0256GPM064T-I/PTV01

# PIC32MM0256GPM064 FAMILY

# PIC32MM0256GPM064 Family Silicon Errata and Data Sheet Clarification

The PIC32MM0256GPM064 family devices that you have received conform functionally to the current Device Data Sheet (DS60001387**D**), except for the anomalies described in this document.

The silicon issues discussed in the following pages are for silicon revisions with the Device and Revision IDs listed in Table 1. The silicon issues are summarized in Table 2.

The errata described in this document will be addressed in future revisions of the PIC32MM0256GPM064 silicon.

Note: This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated in the last column of Table 2 apply to the current silicon revision (A4).

Data Sheet clarifications and corrections start on page 10, following the discussion of silicon issues.

The silicon revision level can be identified using the current version of MPLAB<sup>®</sup> IDE and Microchip's programmers, debuggers and emulation tools, which are available at the Microchip corporate website (www.microchip.com).

For example, to identify the silicon revision level using MPLAB IDE in conjunction with a hardware debugger:

- 1. Using the appropriate interface, connect the device to the hardware debugger.

- 2. Open an MPLAB IDE project.

- 3. Configure the MPLAB IDE project for the appropriate device and hardware debugger.

- 4. Based on the version of MPLAB IDE you are using, do one of the following:

- a) For MPLAB IDE 8, select <u>Programmer ></u> <u>Reconnect</u>.

- b) For MPLAB X IDE, select <u>Window > Dashboard</u> and click the **Refresh Debug Tool** Status icon ( ).

- 5. Depending on the development tool used, the part number *and* Device Revision ID value appear in the **Output** window.

- **Note:** If you are unable to extract the silicon revision level, please contact your local Microchip sales office for assistance.

The DEVREV values for the various PIC32MM0256GPM064 silicon revisions are shown in Table 1.

| Part Number       | Device | Revision ID for<br>Silicon Revision <sup>(2)</sup> |          |       | Part Number | Device<br>ID <sup>(1)</sup> |        |     | on ID for<br>Revision <sup>(2)</sup> |     |     |

|-------------------|--------|----------------------------------------------------|----------|-------|-------------|-----------------------------|--------|-----|--------------------------------------|-----|-----|

|                   | עו (   | A1                                                 | A2 A3 A4 |       | יישו        | A1                          | A2     | A3  | A4                                   |     |     |

| PIC32MM0064GPM028 | 0x7708 |                                                    |          |       |             | PIC32MM0064GPM048           | 0x772C |     |                                      |     |     |

| PIC32MM0128GPM028 | 0x7710 |                                                    |          |       |             | PIC32MM0128GPM048           | 0x7734 |     | 0.01                                 |     |     |

| PIC32MM0256GPM028 | 0x7718 | 016                                                | 0.0 h    | 0.2 h | 0.41        | PIC32MM0256GPM048           | 0x773C | 016 |                                      |     |     |

| PIC32MM0064GPM036 | 0x770A | 01h                                                | 02h      | 03h   | 04h         | PIC32MM0064GPM064           | 0x770E | 01h | 02h                                  | 03h | 04h |

| PIC32MM0128GPM036 | 0x7712 | 1                                                  |          |       |             | PIC32MM0128GPM064           | 0x7716 | 1   |                                      |     |     |

| PIC32MM0256GPM036 | 0x771A |                                                    |          |       |             | PIC32MM0256GPM064           | 0x771E |     |                                      |     |     |

#### TABLE 1: SILICON DEVREV VALUES

**Note 1:** The Device IDs (DEVID and DEVREV) are located at the last two implemented addresses of configuration memory space. They are shown in hexadecimal in the format "DEVID DEVREV".

2: Refer to the "PIC32MM Families Flash Programming Specification" (DS60001364) for detailed information on Device and Revision IDs for your specific device.

# PIC32MM0256GPM064

#### TABLE 2: SILICON ISSUE SUMMARY

| Module                                  | Feature                                                                    | Item   | Issue Summary                                                                                                                                                              |    | Affe<br>Revis |            |    |

|-----------------------------------------|----------------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------------|------------|----|

|                                         |                                                                            | Number | -                                                                                                                                                                          | A1 | A2            | <b>A</b> 3 | A4 |

| 1. Module:ADC                           | 12-Bit Conversion                                                          | 1.     | The ADC may miss one or more of the following codes in 12-bit mode: 1023, 2046, 2047, 3070 and 3071.                                                                       | х  | Х             | х          | Х  |

| 2. Module:ADC                           | Format Options                                                             | 2.     | 32-bit signed format option is the same as the 16-bit signed format option.                                                                                                | Х  | Х             | Х          | Х  |

| 3. Module:UART                          | Receive Buffer<br>Overflow Disable                                         | 3.     | Overflow disable feature controlled by the OVFDIS bit is not functional.                                                                                                   | Х  |               |            |    |

| 4. Module:MCCP                          | OCM3A Output                                                               | 4.     | The OCM3A output for MCCP3 is not functional.                                                                                                                              | Х  | х             | Х          | Х  |

| 5. Module:Primary<br>Oscillator         | Primary Oscillator<br>Start-up Timer (OST)                                 | 5.     | The Primary Oscillator Start-up Timer (OST)<br>may indicate the oscillator is ready for use<br>and set the POSCRDY (CLKSTAT[2]) bit<br>too early.                          | x  | Х             | X          | Х  |

| 6. Module:Reset                         | Reset                                                                      | 6.     | Current consumption in Reset is high.                                                                                                                                      | Х  | Х             | Х          | Х  |

| 7. Module:Timer1                        | External Clock Mode                                                        | 7.     | Timer1 does not overflow in External Clock mode when PR1 = $1$ and the prescaler is 1:1.                                                                                   | Х  | Х             | Х          | Х  |

| 8. Module:Timer1                        | using External Clock mode and a<br>1:1 prescaler.                          |        | х                                                                                                                                                                          | Х  | Х             | х          |    |

| 9. Module:I <sup>2</sup> C Cli-<br>ent  | a NACK from the Host. Writes to I2CxTRN are not ignored in this condition. |        | х                                                                                                                                                                          | Х  | Х             | X          |    |

| 10. Module:I <sup>2</sup> C Cli-<br>ent | I <sup>2</sup> C Client                                                    | 10.    | Client reports a Bus Collision (BLC) for every transaction when SBCDE is enabled.                                                                                          | Х  | Х             | Х          | Х  |

| 11. Module:I <sup>2</sup> C Client      | I <sup>2</sup> C Client                                                    | 11.    | When BOEN = 0, RBF = 0 and I2COV = 1, a NACK is generated but the address is not received.                                                                                 | х  | Х             | Х          | Х  |

| 12. Module:I <sup>2</sup> C Client      | I <sup>2</sup> C Client                                                    | 12.    | The Client may ACK subsequent data after it has gone Idle after a NACK.                                                                                                    | Х  | Х             | Х          | Х  |

| 13. Module:I <sup>2</sup> C Client      | I <sup>2</sup> C Client                                                    | 13.    | The Client will not Acknowledge reserved<br>addresses in the '111_10xx' range,<br>regardless of the STRICT setting.                                                        | х  | Х             | Х          | х  |

| 14. Module:Power                        | Retention Sleep                                                            | 14.    | When the device wakes up from Retention<br>Sleep mode, a device Reset may occur. The<br>BOR, POR and EXTR bits in the RCON<br>register are set erroneously for this Reset. | х  |               |            |    |

| 15. Module:Pro-<br>gramming             | Programming                                                                | 15.    | The JTAG TDO (RC9) pin toggles during<br>programming when using the PGEC1/<br>PGED1 or PGEC2/PGED2 pairs.                                                                  | х  |               |            |    |

| 16. Module:Oscilla-<br>tor              | Secondary Oscillator<br>(SOSC)                                             | 16.    | Enabling POSC in XT or HS mode may inhibit SOSC operation.                                                                                                                 | Х  |               |            |    |

| 17. Module:ADC                          | ADC Performance                                                            | 17.    | Enabling POSC in XT or HS mode may degrade ADC performance.                                                                                                                | Х  |               |            |    |

| 18. Module:Power                        | BOR                                                                        | 18.    | BOR: The main BOR may not function.                                                                                                                                        | Х  | Х             |            |    |

| 19. Module:I/O                          | Schmitt Trigger<br>Inputs                                                  | 19.    | Schmitt Trigger inputs may have glitches with slow signal rise/fall times.                                                                                                 | х  | Х             |            |    |

| 20. Module:SPI                          | SRMT Bit                                                                   | 20.    | In SPI Client mode, the SRMT bit may be set if the FIFO or Shift register is not empty.                                                                                    | Х  | Х             | Х          | Х  |

| Module                          | Feature                     | ltem<br>Number | Issue Summary                                                                                |           | Affe<br>Revis |            |            |

|---------------------------------|-----------------------------|----------------|----------------------------------------------------------------------------------------------|-----------|---------------|------------|------------|

|                                 |                             | Number         |                                                                                              | <b>A1</b> | A2            | <b>A</b> 3 | <b>A</b> 4 |

| 21. Module:ICSP™<br>Programming | Programming                 | 21.            | Programming in Retention Sleep.                                                              | Х         | Х             |            |            |

| 22. Module:ICSP<br>Programming  | Programming                 | 22.            | Self-programming after a POR or MCLR<br>Reset.                                               | Х         | Х             |            |            |

| 23. Module:MCCP                 | Single Edge<br>Compare Mode | 23.            | The Single Edge Compare mode does<br>not work when the Timebase Prescaler is<br>not 1:1.     | Х         | Х             |            |            |

| 24. Module:Reset                | Configuration<br>Mismatch   | 24.            | The CMR bit in RCON may be erroneously set after a POR, BOR or when exiting Retention Sleep. | Х         | Х             |            |            |

| 25. Module:ADC                  | Current                     | 25.            | ADC draws additional current when enabled.                                                   | Х         | Х             | Х          |            |

| 26. Module:UART                 | UART                        | 26.            | The Stop bit is short by one baud clock.                                                     | Х         | Х             | Х          |            |

| 27.<br>Module:Comparato<br>r    | CEVT Bit                    | 27.            | The CMnCON.CEVT bit is not implemented.                                                      | Х         | Х             | Х          | Х          |

## TABLE 2: SILICON ISSUE SUMMARY (CONTINUED)

#### Silicon Errata Issues

**Note:** This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated by the shaded column in the following tables apply to the current silicon revision (**A4**).

#### 1. Module: ADC

The ADC may miss one or more of the following codes in 12-bit mode: 1023, 2046, 2047, 3070 and 3071.

#### Work around

There is no work around in 12-bit mode. If all codes are desired in the application, use 10-Bit Operating mode.

#### Affected Silicon Revisions

| A1 | A2 | A3 | A4 |      |  |

|----|----|----|----|------|--|

| Х  | Х  | Х  | Х  | <br> |  |

#### 2. Module: ADC

The 32-bit signed format option is the same as the 16-bit signed format option.

#### Work around

Use software to correct the output format. Signextend the ADC module's 16-bit signed integer output to a 32-bit signed integer. Using the MPLAB<sup>®</sup> XC32 C compiler, this can be accomplished by casting the ADC1BUFx SFR contents to a volatile short type, followed by a cast to a volatile int type.

#### Affected Silicon Revisions

| Α | 1 | A2 | A3 | <b>A</b> 4 |  |  |

|---|---|----|----|------------|--|--|

| > | ( | Х  | Х  | Х          |  |  |

#### 3. Module: UART

The overflow disable feature controlled by the OVFDIS bit is not functional.

#### Work around

None.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  |    |    |            |  |  |

#### 4. Module: MCCP

The OCM3A output for MCCP3 is not functional.

#### Work around

Select the OCM3B, OCM3C, OCM3D output, or use MCCP1 OCM1A or MCCP2 OCM2A output.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  | Х  | Х          |  |  |

#### 5. Module: Primary Oscillator

The Primary Oscillator Start-up Timer (OST) may indicate the oscillator is ready for use and set the POSCRDY (CLKSTAT[2]) bit too early. Clocking the device before the oscillator is ready may result in incorrect execution and exceptions.

#### Work around

Make sure that the Primary Oscillator clock is ready before using it by following these steps:

- Running on non-POSC source, request the POSC clock using a peripheral such as REFO.

- 2. Provide a delay to stabilize POSC.

- 3. Switch to the POSC source.

Example 1 shows a work around for the device power-on and Example 2 shows the work around when the device wakes from Sleep.

# PIC32MM0256GPM064

#### EXAMPLE 1: USING POSC AT POWER-ON

```

// Oscillator Selection bits (Fast RC oscillator (FRC))

#pragma config FNOSC = FRCDIV

// Clock Switching Enabled (Failsafe Clock Monitor can be enabled or disabled)

#pragma config FCKSM = CSECMD

_ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _ _

void main()

// configure REFO to request POSC

REFO1CONbits.ROSEL = 2;

// POSC = 2

REFOICONDICS....

REFOICONDICS.OE = 0;

// disable output

REFO1CONbits.ON = 1;

// enable module

// wait for POSC stable clock

// this delay may vary depending on different application conditions

// such as voltage, temperature, layout, XT or HS mode and components

{ // delay for 9 ms

unsigned int start = builtin mfc0( CP0 COUNT, CP0 COUNT SELECT);

while(( builtin mfc0( CP0 COUNT, CP0 COUNT SELECT)) - start < (unsigned int)(0.009*8000000/2));

// unlock OSCCON

SYSKEY = 0;

SYSKEY = 0xAA996655;

SYSKEY = 0x556699AA;

// switch to POSC = 2

OSCCONCLR = OSCCON NOSC MASK | OSCCON CLKLOCK MASK | OSCCON OSWEN MASK;

OSCCONSET = (2<< OSCCON NOSC POSITION) | OSCCON_OSWEN_MASK;

while(OSCCONbits.OSWEN == 1); // wait for switch

```

#### EXAMPLE 2: USING POSC WHEN AWAKENED FROM SLEEP

```

// Clock Switching Enabled (Failsafe Clock Monitor can be enabled or disabled)

#pragma config FCKSM = CSECMD

// unlock OSCCON

SYSKEY = 0;

SYSKEY = 0xAA996655;

SYSKEY = 0 \times 556699 AA;

// switch to FRC = 0 before entering to sleep

OSCCONCLR = _OSCCON_NOSC_MASK | _OSCCON_CLKLOCK MASK | _OSCCON OSWEN MASK;

OSCCONSET = (0<<_OSCCON_NOSC_POSITION) | _OSCCON_OSWEN_MASK;

while(OSCCONbits.OSWEN == 1);

// wait for switch

// enter sleep mode

asm

volatile("wait");

// configure REFO to request POSC

REFO1CONbits.ROSEL = 2;

// POSC = 2

REFO1CONbits.OE = 0;

// disable output

REFO1CONbits.ON = 1;

// enable module

// wait for POSC stable clock

// this delay may vary depending on different application conditions

// such as voltage, temperature, layout, XT or HS mode and components

{ // delay for 9 ms

unsigned int start = builtin mfc0( CPO COUNT, CPO COUNT SELECT);

while(( builtin mfc0( CP0 COUNT, CP0 COUNT SELECT)) - start < (unsigned int)(0.009*8000000/2));

1

// switch to POSC = 2

OSCCONCLR = _OSCCON_NOSC_MASK | OSCCON_CLKLOCK_MASK | OSCCON_OSWEN_MASK;

OSCCONSET = (2<< OSCCON NOSC POSITION) | OSCCON OSWEN MASK;

while (OSCCONbits.OSWEN == 1);

// wait for switch

```

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  | Х  | Х          |  |  |

#### 6. Module: Reset

Current consumption in Master Clear Reset is high.

#### Work around

Do not use MCLR to hold device in Reset to save power.

#### Affected Silicon Revisions

| A1 | A2 | A3 | A4 |  |  |

|----|----|----|----|--|--|

| Х  | Х  | Х  | Х  |  |  |

#### 7. Module: Timer1

Timer1 does not overflow in External Clock mode when PR1 = 1 and the prescaler is 1:1.

#### Work around

Use a PR1 value greater than one.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  | Х  | Х          |  |  |

#### 8. Module: Timer1

The first increment value is not visible when using External Clock mode and a 1:1 prescaler.

#### Work around

None.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  | Х  | Х          |  |  |

### 9. Module: I<sup>2</sup>C Client

The  $I^2C$  line does not return to Idle after receiving a NACK from the Host. Writes to I2CxTRN are not ignored in this condition.

#### Work around

Do not write to the I2CxTRN register after a NACK has been received.

#### Affected Silicon Revisions

| A1 | A2 | A3 | A4 |  |  |

|----|----|----|----|--|--|

| Х  | Х  | Х  | Х  |  |  |

### 10. Module: I<sup>2</sup>C Client

Client reports a Bus Collision (BLC) for every transaction when SBCDE is enabled.

#### Work around

Do not enable SBCDE.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  | Х  | Х          |  |  |

## 11. Module: I<sup>2</sup>C Client

When BOEN = 0, RBF = 0, and I2COV = 1 a NACK is generated, but the address is not received.

#### Work around

Service the receive buffer to prevent an overflow.

#### Affected Silicon Revisions

| A1 | A2 | A3 | A4 |  |  |

|----|----|----|----|--|--|

| Х  | Х  | Х  | Х  |  |  |

#### 12. Module: I<sup>2</sup>C Client

The Client may ACK subsequent data after it has gone Idle after a NACK.

#### Work around

The Host should not send data following a NACK without generating a Start condition

#### Affected Silicon Revisions

| A1 | A2 | A3 | A4 |  |  |

|----|----|----|----|--|--|

| Х  | Х  | Х  | Х  |  |  |

#### 13. Module: I<sup>2</sup>C Client

The Client will not Acknowledge reserved addresses in the '111\_10xx' range, regardless of the STRICT bit setting.

#### Work around

None.

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  | Х  | Х          |  |  |

#### 14. Module: Power

When the device wakes up from Retention Sleep mode, a device Reset may occur. The BOR, POR and EXTR bits in RCON register are set erroneously for this Reset.

#### Work around

To provide a consistent behavior when the device wakes up from the Retention Sleep mode, the software sequence should be performed following the SLEEP instruction. In this case, a Reset will always be generated when the device wakes up from Retention Sleep.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  |    |    |            |  |  |

#### 15. Module: Programming

The JTAG TDO (RC9) pin toggles during programming when using the PGEC1/PGED1 or PGEC2/PGED2 pairs.

#### Work around

Do not connect external circuitry to the TDO pin that cannot tolerate toggling when programming using the PGEC1/PGED1 or PGEC2/PGED2 pins.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  |    |    |            |  |  |

#### 16. Module: Oscillator

Enabling POSC in XT or HS mode may inhibit SOSC operation.

#### Work around

If SOSC operation is required, use FRC or FRCPLL instead of POSC.

#### Affected Silicon Revisions

| 4 | A1 | A2 | A3 | A4 |  |  |

|---|----|----|----|----|--|--|

|   | Х  |    |    |    |  |  |

#### 17. Module: ADC

Enabling POSC in XT or HS mode may degrade ADC performance in 10-bit and 12-bit mode.

#### Work around

If ADC operation that meets the data sheet specification is required, use FRC or FRCPLL instead of POSC.

#### Affected Silicon Revisions

| <b>A</b> 1 | A2 | A3 | A4 |  |  |

|------------|----|----|----|--|--|

| Х          |    |    |    |  |  |

#### 18. Module: Power

The main BOR may not occur when the operating voltage drops below the BOR trip voltage.

#### Work around

Ensure the device operating voltage does not violate the specified values.

Use an external supervisor circuit to reset the device if the operating voltage can be outside the specified values.

#### Affected Silicon Revisions

| A1 | A2 | A3 | A4 |  |  |

|----|----|----|----|--|--|

| Х  | Х  |    |    |  |  |

#### 19. Module: I/O

If the input signal rise or fall time is more than 500 nS, the I/O Schmitt Trigger output may have glitches.

#### Work around

The rise/fall time of the input signal must be less than 500 nS.

| A1 | A2 | A3 | A4 |  |  |

|----|----|----|----|--|--|

| Х  | Х  |    |    |  |  |

#### 20. Module: SPI

In SPI Client mode, the SRMT bit may be set if the FIFO or Shift register is not empty.

#### Work around

The following work arounds can be implemented in the application to detect when the FIFO and Shift register are empty:

- 1. Check the SPITBF bit before checking the SRMT bit. If the SPITBF flag is cleared and the SRMT flag is set, then all data were transmitted. Example 3 demonstrates the SPITBF and SRMT bits polling.

- Read the SRMT bit twice, back-to-back. If the SRMT bit is set two reads in a row, then the FIFO and Shift register are empty. Example 4 demonstrates the SRMT bit polling using double read.

#### EXAMPLE 3: EMPTY STATUS DETECTION USING SPITBF AND SRMT BITS POLLING

// Both flags must indicate empty status.

while(SPI1STATLbits.SPITBF);

while(!SPI1STATLbits.SRMT);

#### EXAMPLE 4: EMPTY STATUS DETECTION USING SRMT BIT POLLING WITH BACK-TO-BACK READS

| // If | SRMI  | 'bit   | is s | set  | two  | reads | in | а | row |

|-------|-------|--------|------|------|------|-------|----|---|-----|

| th    | en it | set    | cori | rect | cly. |       |    |   |     |

| asm   | vola  | tile(' | \n\  |      |      |       |    |   |     |

| la    | \$t0, | SPI15  | TAT  | ; \  |      |       |    |   |     |

| loop: | ; \   |        |      |      |      |       |    |   |     |

| lw    | \$t1, | 0(\$t( | );\  |      |      |       |    |   |     |

| lw    | \$t2, | 0(\$t( | );\  |      |      |       |    |   |     |

| and   | \$t1, | \$t1,  | \$t2 | ; \  |      |       |    |   |     |

| andi  | \$t1, | \$t2,  | 0x8  | 0;\  |      |       |    |   |     |

| beqz  | \$t1, | loop;  | ");  |      |      |       |    |   |     |

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  | Х  | Х          |  |  |

#### 21. Module: ICSP<sup>™</sup> Programming

After a POR or  $\overline{\text{MCLR}}$  Reset, the device may fail to program if Retention Sleep is invoked within 40 ms.

#### Work around

Provide a delay in firmware to ensure the device does not enter Retention Sleep within 40 ms of a POR or MCLR Reset.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  |    |            |  |  |

#### 22. Module: ICSP Programming

After a POR or  $\overline{\text{MCLR}}$  Reset, the device may fail to program using ICSP if user firmware performs self-programming within 40 ms.

#### Work around

Provide a delay in firmware to ensure the device does not perform self-programming within 40 ms of a POR or MCLR Reset.

#### Affected Silicon Revisions

| A1 | A2 | A3 | A4 |  |  |

|----|----|----|----|--|--|

| Х  | Х  |    |    |  |  |

#### 23. Module: MCCP

The Single Edge Compare mode does not work when the Timebase Prescaler is not 1:1.

#### Work around

Use 1:1 Prescaler value.

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  |    |            |  |  |

#### 24. Module: Reset

The CMR bit in RCON may be erroneously set after a POR, BOR, or when exiting Retention Sleep.

#### Work around

Clear the CMR bit following a POR, BOR, or exit from Retention Sleep.

#### Affected Silicon Revisions

| A1 | A2 | A3 | A4 |  |  |

|----|----|----|----|--|--|

| Х  | Х  |    |    |  |  |

#### 25. Module: ADC

On some devices, the current draw may increase by up to 12 mA when the ADC is enabled. This current draw is not affected by the device Power Save modes or ADC configuration. This additional current does not affect the ADC or device performance.

#### Work around

Disable the ADC when it is not converting or not used in the application.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  | Х  |            |  |  |

#### 26. Module: UART

The Stop bit is short by one baud clock. In BRGH = 0 mode, the Stop bit is short by 1/16 bit time. In BRGH = 1 mode, the Stop bit is short by 1/4 bit time. When two Stop bits are enabled, the total Stop bit time is short by 1/16 or 1/4 bit time based on the BRGH mode.

#### Work around

Use a timer driven interrupt to write data to the UART Transmit Shift register, one byte at a time. The timer period must be greater than the sum of the number of bits in the serial data, the Start bit and the Stop bit(s). The difference in time between interrupt timer period and the sum of bit time creates the line Idle time needed to extend the Stop bit.

For example, at 9600 baud, eight data bits, one Stop bit: 10 \* 104.17  $\mu$ s = 1041.7  $\mu$ s. The time between writes to the UART TX buffer must be greater than 1041.7  $\mu$ s

- 2.a If only transmission is required, use two Stop bits. This will be interpreted by a UART configured for one Stop bit as one Stop bit and a 15/16 bit time line Idle.

- 2.b If transmit and receive are required, use two UARTs. Configure one for transmit (as described in #1 above); configure the other UART for receive with one Stop bit.

#### Affected Silicon Revisions

| A1 | A2 | A3 | <b>A</b> 4 |  |  |

|----|----|----|------------|--|--|

| Х  | Х  | Х  |            |  |  |

#### 27. Module: Comparator

The Comparator Event bit, CMnCON.CEVT (n = 0,1,2), is not implemented.

#### Work around

Comparator event status is available in the CMSTAT.C*n*EVT bits (n = 0,1,2). Enabling the next comparator event by zeroing the CEVT bit is not required.

| A1 | A2 | A3 | A4 |  |  |

|----|----|----|----|--|--|

| Х  | Х  | Х  | Х  |  |  |

### **Data Sheet Clarifications**

The following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (DS60001387**D**):

| Note: | Corrections are shown in <b>bold</b> . Where |

|-------|----------------------------------------------|

|       | possible, the original bold text formatting  |

|       | has been removed for clarity.                |

#### 1. Module: Electrical Characteristics

In **TABLE 29-1: THERMAL OPERATING CONDITIONS**, the maximum value for the PIC32MM0XXXGPM0XX Operating Junction Temperature Range (TJ) has changed from +125°C to 140°C.

#### 2. Module: Pin Diagrams: 48-Pin UQFN, TQFP

Note 3 is applicable for the 48-pin UQFN package only. The Thermal pad is not available on the 48-pin TQFP Package.

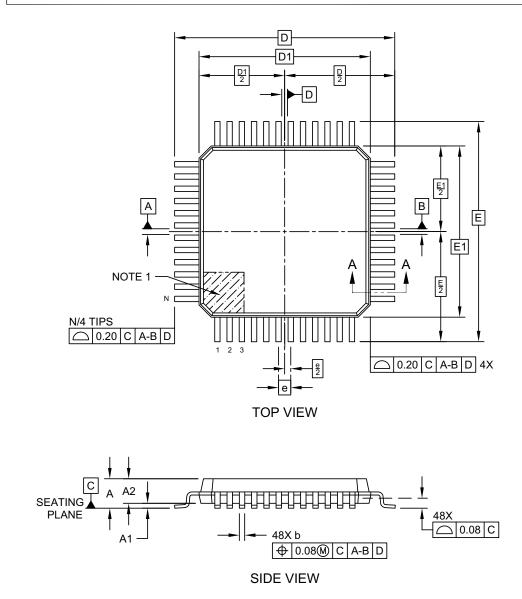

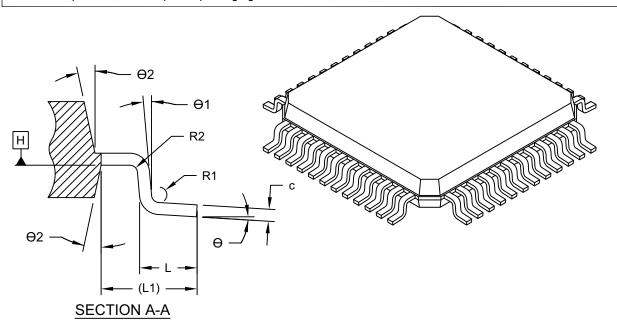

#### 3. Module: Package Details/Drawing: 48-Pin TQFP

The following figure shows the updated package drawing for the 48-Pin TQFP Device:

#### 48-Lead Plastic Thin Quad Flatpack (Y8X) - 7x7x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-300-Y8X Rev D Sheet 1 of 2

## 48-Lead Plastic Thin Quad Flatpack (Y8X) - 7x7x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units         | MILLIMETERS |          |      |  |

|--------------------------|---------------|-------------|----------|------|--|

| Dime                     | ension Limits | MIN         | NOM      | MAX  |  |

| Number of Terminals      | N             | N 48        |          |      |  |

| Pitch                    | е             |             | 0.50 BSC |      |  |

| Overall Height           | А             | -           | -        | 1.20 |  |

| Standoff                 | A1            | 0.05        | -        | 0.15 |  |

| Molded Package Thickness | A2            | 0.95        | 1.00     | 1.05 |  |

| Overall Length           | D             | 9.00 BSC    |          |      |  |

| Molded Package Length    | D1            | 7.00 BSC    |          |      |  |

| Overall Width            | E             | 9.00 BSC    |          |      |  |

| Molded Package Width     | E1            | 7.00 BSC    |          |      |  |

| Terminal Width           | b             | 0.17        | 0.22     | 0.27 |  |

| Terminal Thickness       | С             | 0.09        | -        | 0.16 |  |

| Terminal Length          | L             | 0.45        | 0.60     | 0.75 |  |

| Footprint                | L1            |             | 1.00 REF |      |  |

| Lead Bend Radius         | R1            | 0.08        | -        | -    |  |

| Lead Bend Radius         | R2            | 0.08        | -        | 0.20 |  |

| Foot Angle               | θ             | 0°          | 3.5°     | 7°   |  |

| Lead Angle               | θ1            | 0°          | -        | -    |  |

| Mold Draft Angle         | θ2            | 11°         | 12°      | 13°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-300-Y8X Rev D Sheet 2 of 2

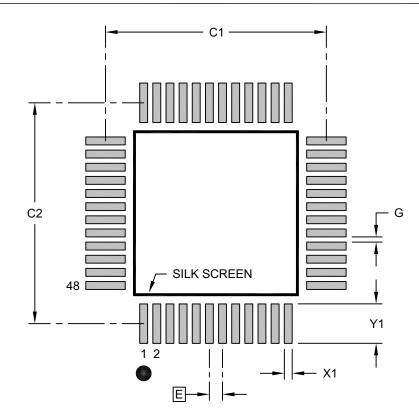

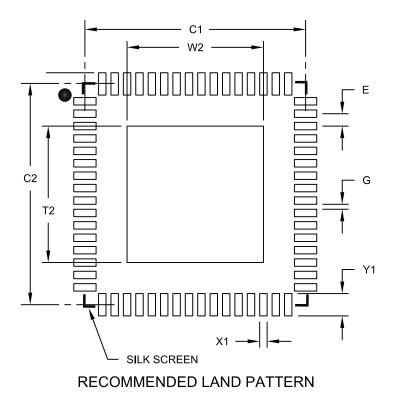

## 48-Lead Plastic Thin Quad Flatpack (Y8X) - 7x7x1.0 mm Body [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | Units |          |      |      |

|--------------------------|-------|----------|------|------|

| Dimension                | MIN   | NOM      | MAX  |      |

| Contact Pitch            | E     | 0.50 BSC |      |      |

| Contact Pad Spacing      | C1    |          | 8.40 |      |

| Contact Pad Spacing      | C2    |          | 8.40 |      |

| Contact Pad Width (X48)  | X1    |          |      | 0.30 |

| Contact Pad Length (X48) | Y1    |          |      | 1.50 |

| Distance Between Pads    | G     | 0.20     |      |      |

Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2300-Y8X Rev D

#### 4. Module: Pin Diagrams: 64-Pin QFN, TQFP

Note 3 is applicable for the 64-pin QFN package only. The Thermal pad is not available on the 64-Pin TQFP package.

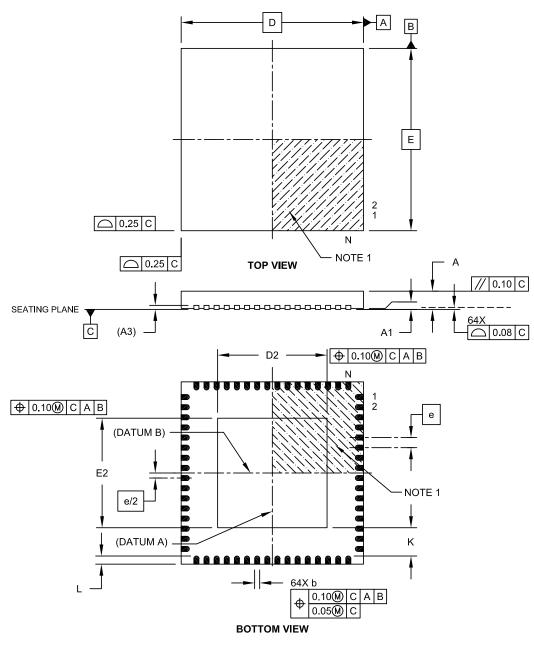

#### 5. Module: Package Details/Drawing: 64-Pin QFN

The following figure shows the updated package drawing for the 64-Pin QFN device.

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

|                        | Units            | N        | <b>ILLIMETER</b> | S    |

|------------------------|------------------|----------|------------------|------|

| Dimension              | Dimension Limits |          |                  | MAX  |

| Number of Pins         | N                |          | 64               |      |

| Pitch                  | е                |          | 0.50 BSC         |      |

| Overall Height         | A                | 0.80     | 0.90             | 1.00 |

| Standoff               | A1               | 0.00     | 0.02             | 0.05 |

| Contact Thickness      | A3               | 0.20 REF |                  |      |

| Overall Width          | E                |          | 9.00 BSC         |      |

| Exposed Pad Width      | E2               | 5.30     | 5.40             | 5.50 |

| Overall Length         | D                |          | 9.00 BSC         |      |

| Exposed Pad Length     | D2               | 5.30     | 5.40             | 5.50 |

| Contact Width          | b                | 0.20     | 0.25             | 0.30 |

| Contact Length         | L                | 0.30     | 0.40             | 0.50 |

| Contact-to-Exposed Pad | К                | 0.20     | -                | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 5.40x5.40mm Exposed Pad

|                            | Units |      |          |      |  |

|----------------------------|-------|------|----------|------|--|

| Dimension                  | MIN   | NOM  | MAX      |      |  |

| Contact Pitch              | E     |      | 0.50 BSC |      |  |

| Optional Center Pad Width  | W2    |      |          | 5.50 |  |

| Optional Center Pad Length | T2    |      |          | 5.50 |  |

| Contact Pad Spacing        | C1    |      | 8.90     |      |  |

| Contact Pad Spacing        | C2    |      | 8.90     |      |  |

| Contact Pad Width (X64)    | X1    |      |          | 0.30 |  |

| Contact Pad Length (X64)   | Y1    |      |          | 0.85 |  |

| Distance Between Pads      | G     | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2154A

# PIC32MM0256GPM064

## APPENDIX A: DOCUMENT REVISION HISTORY

Rev A Document (3/2017)

Initial release of this document; issued for revision A1.

Rev B Document (5/2017)

Added silicon revision A2.

Updated Table 1 and Table 2.

Added new silicon issues 18 (18. Module:Power), 19 (19. Module:I/O), 20 (20. Module:SPI) and 21 (21. Module:ICSP™ Programming).

Rev C Document (6/2017)

Updated Table 2.

Added new silicon issues 22 (22. Module:ICSP Programming).

Added new data sheet clarification 1 (Electrical Characteristics).

Rev D Document (7/2018)

Added silicon revision A3.

Added new silicon issues 23 (23. Module:MCCP) and 24 (24. Module:Reset).

Removed data sheet clarification 1 (Electrical Characteristics) since this issue was corrected in the latest data sheet revision DS60001387**C**.

Rev E Document (1/2019)

Added silicon issue 25 (25. Module:ADC).

Rev F Document (4/2020)

Added silicon revision A4.

Added silicon issue 26 (26. Module:UART).

Rev G Document (10/2020)

Added data sheet clarification 1 (1. Module:Electrical Characteristics).

Rev H Document (01/2021)

Numerous typographical changes were made throughout the document.

The following Data Sheet clarifications were added:

- 2. Module: Pin Diagrams: 48-Pin UQFN, TQFP

- 3. Module:Package Details/Drawing: 48-Pin TQFP

- 4. Module: Pin Diagrams: 64-Pin QFN, TQFP

- 5. Module:Package Details/Drawing: 64-Pin QFN

Updated the following errata modules with a new verbiage: replaced the term "Slave" with "Client" and "Master" with "Host".

- 9. Module: I<sup>2</sup>C Client

- 10. Module: I<sup>2</sup>C Client

- 11. Module: I<sup>2</sup>C Client

- 12. Module: I<sup>2</sup>C Client

- 13. Module: I<sup>2</sup>C Client

- 20. Module:SPI

Rev J Document (11/2021)

The following errata was added in this revision:

· 27. Module:Comparator

# PIC32MM0256GPM064

NOTES:

#### Note the following details of the code protection feature on Microchip products:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner, within operating specifications, and under normal conditions.

- Microchip values and aggressively protects its intellectual property rights. Attempts to breach the code protection features of Microchip product is strictly prohibited and may violate the Digital Millennium Copyright Act.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable". Code protection is constantly evolving. Microchip is committed to

continuously improving the code protection features of our products.

This publication and the information herein may be used only with Microchip products, including to design, test, and integrate Microchip products with your application. Use of this information in any other manner violates these terms. Information regarding device applications is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. Contact your local Microchip sales office for additional support or, obtain additional support at https:// www.microchip.com/en-us/support/design-help/client-supportservices.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WAR-RANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE, OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL, OR CONSE-QUENTIAL LOSS, DAMAGE, COST, OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION.

Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### Trademarks

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, CryptoMemory, CryptoRF, dsPIC, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, Flashtec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, TrueTime, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, GridTime, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, Knob-on-Display, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, NVM Express, NVMe, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SmartHLS, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, Symmcom, and Trusted Time are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

$\ensuremath{\textcircled{\sc 0}}$  2017-2021, Microchip Technology Incorporated and its subsidiaries.

All Rights Reserved.

ISBN: 978-1-5224-9270-2

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# Worldwide Sales and Service

#### AMERICAS

**Corporate Office** 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston** Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Dallas Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000 China - Chengdu

Tel: 86-28-8665-5511 China - Chongqing Tel: 86-23-8980-9588

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang Tel: 86-24-2334-2829

China - Shenzhen Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

China - Wuhan Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138

Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631 India - Pune

Tel: 91-20-4121-0141 Japan - Osaka

Tel: 81-6-6152-7160 Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301 Korea - Seoul

Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei

Tel: 84-28-5448-2100

Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

EUROPE

Austria - Wels

Tel: 43-7242-2244-39

Tel: 45-4485-5910

Fax: 45-4485-2829

Tel: 358-9-4520-820

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching

Tel: 49-2129-3766400

Germany - Heilbronn

Germany - Karlsruhe

Tel: 49-7131-72400

Tel: 49-721-625370

Germany - Munich

Tel: 49-89-627-144-0

Fax: 49-89-627-144-44

Germany - Rosenheim

Tel: 49-8031-354-560

Israel - Ra'anana

Tel: 49-8931-9700

Germany - Haan

Finland - Espoo

France - Paris

Fax: 43-7242-2244-393

Denmark - Copenhagen

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh

China - Zhuhai