### **Product Change Notification / SYST-25LGPN222**

| ח | 2 | ŧ | Δ | • |

|---|---|---|---|---|

| u | а | L | ᆫ |   |

26-Mar-2021

### **Product Category:**

8-bit Microcontrollers

### **PCN Type:**

Document Change

### **Notification Subject:**

ERRATA - PIC16(L)F15324/44 Family Silicon Errata and Data Sheet Clarification Errata Document Revision

### **Affected CPNs:**

SYST-25LGPN222\_Affected\_CPN\_03262021.pdf SYST-25LGPN222 Affected CPN 03262021.csv

### **Notification Text:**

SYST-25LGPN222

Microchip has released a new Product Documents for the PIC16(L)F15324/44 Family Silicon Errata and Data Sheet Clarification of devices. If you are using one of these devices please read the document located at PIC16(L)F15324/44 Family Silicon Errata and Data Sheet Clarification.

Notification Status: Final

Description of Change: 1) Updated Table 2 and 37-1 and Section 1.3 Minimum VDD Specifications. Other minor

corrections.

Impacts to Data Sheet: None

Reason for Change: To Improve Productivity

Change Implementation Status: Complete

Date Document Changes Effective: 26 Mar 2021

NOTE: Please be advised that this is a change to the document only the product has not been changed. Markings to Distinguish Revised from Unrevised Devices: N/A Attachments: PIC16(L)F15324/44 Family Silicon Errata and Data Sheet Clarification Please contact your local Microchip sales office with questions or concerns regarding this notification. **Terms and Conditions:** If you wish to receive Microchip PCNs via email please register for our PCN email service at our PCN home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the PCN FAQ section. If you wish to change your PCN profile, including opt out, please go to the PCN home page select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

### Affected Catalog Part Numbers (CPN)

PIC16F15325-E/JQ

PIC16F15325-E/JQVAO

PIC16F15325-E/P

PIC16F15325-E/SL

PIC16F15325-E/SLVAO

PIC16F15325-E/ST

PIC16F15325-I/JQ

PIC16F15325-I/P

PIC16F15325-I/SL

PIC16F15325-I/SLVAO

PIC16F15325-I/ST

PIC16F15325T-E/7NVAO

PIC16F15325T-E/JQ

PIC16F15325T-E/JQVAO

PIC16F15325T-E/SLVAO

PIC16F15325T-E/STVAO

PIC16F15325T-I/JQ

PIC16F15325T-I/SL

PIC16F15325T-I/ST

PIC16F15345-E/GZ

PIC16F15345-E/GZVAO

PIC16F15345-E/P

PIC16F15345-E/SO

PIC16F15345-E/SS

PIC16F15345-I/GZ

PIC16F15345-I/P

PIC16F15345-I/SO

PIC16F15345-I/SS

PIC16F15345-I/SSVAO

PIC16F15345T-E/6NV05

PIC16F15345T-E/6NVAO

PIC16F15345T-E/GZVAO

PIC16F15345T-E/MLVAO

PIC16F15345T-E/SSVAO

PIC16F15345T-I/GZ

PIC16F15345T-I/SO

PIC16F15345T-I/SS

PIC16F15345T-I/SSV06

PIC16F15345T-I/SSVAO

PIC16LF15325-E/JQ

PIC16LF15325-E/P

PIC16LF15325-E/SL

PIC16LF15325-E/ST

PIC16LF15325-I/JQ

PIC16LF15325-I/P

PIC16LF15325-I/SL

Date: Friday, March 26, 2021

# SYST-25YQMY847 - ERRATA - PIC16(L)F15325/45 Family Silicon Errata and Data Sheet Clarification Errata Document Revision PIC16LF15325-I/ST PIC16LF15325/SD02 PIC16LF15325T-E/JQV02 PIC16LF15325T-E/JQVAO PIC16LF15325T-E/STV03

PIC16LF15325T-I/JQ

PIC16LF15325T-I/SL

PIC16LF15325T-I/ST

PIC16LF15345-E/6NVAO

PIC16LF15325T-E/STVAO

PIC16LF15345-E/GZ

PIC16LF15345-E/P

PIC16LF15345-E/SO

PIC16LF15345-E/SS

PIC16LF15345-I/GZ

PIC16LF15345-I/P

PIC16LF15345-I/SO

PIC16LF15345-I/SS

PIC16LF15345-I/SSVAO

PIC16LF15345T-E/6NVAO

PIC16LF15345T-E/GZVAO

PIC16LF15345T-E/SS

PIC16LF15345T-I/GZ

PIC16LF15345T-I/SO

PIC16LF15345T-I/SS

PIC16LF15345T-I/SSV04

PIC16LF15345T-I/SSVAO

Date: Friday, March 26, 2021

# PIC16(L)F15325/45

### PIC16(L)F15325/45 Family Silicon Errata and Data Sheet Clarification

The PIC16(L)F15325/45 family devices that you have received conform functionally to the current Device Data Sheet (DS40001865**D**), except for the anomalies described in this document.

The silicon issues discussed in the following pages are for silicon revisions with the Device and Revision IDs listed in Table 1. The silicon issues are summarized in Table 2.

The errata described in this document will be addressed in future revisions of the PIC16(L)F15325/45 silicon.

Note: This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated in the last column of Table 2 apply to the current silicon revision (A2).

Data Sheet clarifications and corrections start on page 6, following the discussion of silicon issues.

The silicon revision level can be identified using the current version of MPLAB<sup>®</sup> X IDE and Microchip's programmers, debuggers, and emulation tools, which are available at the Microchip corporate website (www.microchip.com).

For example, to identify the silicon revision level using MPLAB X IDE in conjunction with a hardware debugger:

- Using the appropriate interface, connect the device to the hardware debugger.

- 2. Open an MPLAB X IDE project.

- Configure the MPLAB X IDE project for the appropriate device and hardware debugger.

- For MPLAB X IDE, select <u>Window > Dashboard</u> and click the Refresh Debug Tool Status icon

- Depending on the development tool used, the part number and Device Revision ID value appear in the Output window.

Note: If you are unable to extract the silicon revision level, please contact your local Microchip sales office for assistance.

The DEVREV values for the various PIC16(L)F15325/45 silicon revisions are shown in Table 1.

TABLE 1: SILICON DEVREY VALUES

| Don't Musels or | Device ID <sup>(1)</sup> | Revision ID for Silicon Revision <sup>(2)</sup> |       |  |  |

|-----------------|--------------------------|-------------------------------------------------|-------|--|--|

| Part Number     | Device ID(-)             | A1                                              | A2    |  |  |

| PIC16F15325     | 30C6h                    | 2001h                                           | 2002h |  |  |

| PIC16LF15325    | 30C7h                    | 2001h                                           | 2002h |  |  |

| PIC16F15345     | 30C8h                    | 2001h                                           | 2002h |  |  |

| PIC16LF15345    | 30C9h                    | 2001h                                           | 2002h |  |  |

- Note 1: The Device IDs (DEVID and DEVREV) are located at addresses 8006h and 8005h, respectively. They are shown in hexadecimal in the format "DEVID DEVREV".

- Refer to the "PIC16(L)F153XX Memory Programming Specification" (DS40001838) for detailed information on Device and Revision IDs for your specific device.

TABLE 2: SILICON ISSUE SUMMARY

| Module                                  | Feature                                                                  | Item<br>Number | Issue Summary                                                                                                                                                                                                                                                               |    | cted<br>ions <sup>(1)</sup> |

|-----------------------------------------|--------------------------------------------------------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------|

|                                         |                                                                          | Number         | ,                                                                                                                                                                                                                                                                           | A1 | A2                          |

| Analog-to-Digital<br>Converter (ADC)    | ADC Positive<br>Voltage Reference                                        | 1.1            | Using FVR as the positive voltage reference to the ADC can cause missing codes in the conversion result.                                                                                                                                                                    | х  | X                           |

| Development Support                     | Data Breakpoints                                                         | 2.1            | Data breakpoints are not available on Banks 59 through 63.                                                                                                                                                                                                                  | X  |                             |

| Windowed Watchdog                       | Watchdog Timer<br>Clock Source                                           | 3.1            | WWDT does not work with SOSC as the clock source.                                                                                                                                                                                                                           | X  |                             |

| Timer (WWDT)                            | Window Operation in DOZE Mode                                            | 3.2            | Window feature of the WWDT does not operate correctly in DOZE mode.                                                                                                                                                                                                         | X  | X                           |

| VO Deste                                | SMBus Mode                                                               | 4.1            | SMBus levels are not functional on RB4 and RB6 PORT pins.                                                                                                                                                                                                                   | Х  |                             |

| I/O Ports                               | Slew Rate Control                                                        | 4.2            | Slew Rate Control feature does not exist on RB4 and RB6 PORT pins.                                                                                                                                                                                                          |    |                             |

|                                         | SMBus VIL                                                                | 5.1            | The maximum VIL level changes when VDD is below 4.0V.                                                                                                                                                                                                                       |    |                             |

| Electrical                              | Fixed Voltage<br>Reference (FVR)<br>Accuracy                             | 5.2            | FVR output tolerance may be higher than specified at temperatures below -20°C.                                                                                                                                                                                              |    | X                           |

| Specifications                          | Minimum VDD<br>Specification for<br>LF Devices                           | 5.3            | VDDMIN specifications are changed for LF devices only.                                                                                                                                                                                                                      | х  | X                           |

|                                         | ADC Offset Error                                                         | 5.4            | ADC Offset Error specification changed.                                                                                                                                                                                                                                     | X  | X                           |

| Host Synchronous<br>Serial Port (MSSP)  | SPI Client Mode                                                          | 6.1            | SSPBUF transmit shift register may be corrupted under certain conditions.                                                                                                                                                                                                   | Х  | X                           |

| Nonvolatile Memory<br>(NVM)             | WRERR Bit<br>Operation                                                   | 7.1            | When performing an NVM high-voltage operation, if a Reset is issued in the middle of the operation, the WRERR bit is set. Then, if the user clears the WRERR bit and a Reset occurs again, this sets the WRERR bit because the internal latch has not been cleared earlier. |    | х                           |

| Digital-to-Analog<br>(DAC)              | Debug Mode                                                               | 8.1            | FVR as the positive voltage source is not functional in Debug mode.                                                                                                                                                                                                         |    | X                           |

| Reference Clock<br>Output Module (CLKR) | rence Clock CLKP Output 9.1 First output pulse of Reference Clock Output |                |                                                                                                                                                                                                                                                                             |    | X                           |

Note 1: Only those issues indicated in the last column apply to the current silicon revision.

### Silicon Errata Issues

Note:

This document summarizes all silicon errata issues from all revisions of silicon, previous as well as current. Only the issues indicated by the shaded column in the following tables apply to the current silicon revision (A2).

## 1. Module: Analog-to-Digital Converter (ADC)

### 1.1 ADC Positive Voltage Reference

Using the FVR as the positive voltage reference to the ADC can cause an increase in missing codes.

### Work around

- Increase the bit conversion time, known as TAD, to 8 us.

- Use V<sub>DD</sub> as the positive voltage reference to the ADC.

### **Affected Silicon Revisions**

| A1 | A2 |  |  |  |

|----|----|--|--|--|

| X  | X  |  |  |  |

### 2. Module: Development Support

### 2.1 Data Breakpoints

Data breakpoints are not available on Banks 59 through 63. Any breakpoints that are placed in Banks 59 through 63 will fail to be recognized.

### Work around

None.

### Affected Silicon Revisions

|   | A1 | A2 |  |  |  |

|---|----|----|--|--|--|

| I | X  |    |  |  |  |

# 3. Module: Windowed Watchdog Timer (WWDT)

### 3.1 WWDT Clock Source Selection

When the WDTCS [2:0] bits of the WDTCON1 register are set to 'b010', selecting the Secondary Oscillator SOSC 32 kHz, as the clock source, the WWDT does not operate.

### Work around

Use the LFINTOSC or MFINTOSC clock sources for the WWDT.

### Affected Silicon Revisions

| A1 | A2 |  |  |  |

|----|----|--|--|--|

| X  |    |  |  |  |

### 3.2 Window Feature of the WWDT Does Not Operate Correctly in DOZE Mode

When the Windowed mode of operation is enabled in DOZE mode, a window violation error is issued even though the window is open and has been armed. This condition occurs only when the window size is set to a value other than 100% open.

### Work around

- Use the Windowed mode of operation in any other mode than DOZE. If disabling the DOZE mode is not an option, use the WWDT module without the window being enabled.

- If the device is in DOZE mode, perform the arming process for the window in NORMAL mode, and return to the DOZE mode.

- If there is an ISR in the application code, the arming within the window can be done inside the ISR with the ROI bit of the CPUDOZE register being set.

### Affected Silicon Revisions

| A1 | A2 |  |   |  |  |

|----|----|--|---|--|--|

| Χ  | Χ  |  | j |  |  |

### 4. Module: I/O Ports

### 4.1 SMBus Mode

The SMBus signal levels are not available for the I<sup>2</sup>C functions of pins RB4 and RB6.

Standard ST and TTL levels are still available for these pins, which are configurable through the INLVLB register settings.

### Work around

Use the Peripheral Pin Select (PPS) feature and move the required I<sup>2</sup>C functions to PORTC where the SMBus levels are still available.

#### Affected Silicon Revisions

| A1 | A2 |  |  |  |

|----|----|--|--|--|

| Χ  |    |  |  |  |

### 4.2 Slew Rate Control

The Slew Rate Control feature is not available on pins RB4 and RB6.

### Work around

Use other available PORT pins when slew rate control is required.

### **Affected Silicon Revisions**

| A1 | A2 |  |  |  |

|----|----|--|--|--|

| X  |    |  |  |  |

### 5. Module: Electrical Specifications

### 5.1 SMBus VIL Level

When the VDD voltage level supplied to the device is 4.0V and above, the maximum SMBus voltage level for the VIL parameter is 0.8V. When VDD drops below 4.0V, the maximum SMBus voltage level for VIL drops to 0.7V.

#### Work around

None.

#### Affected Silicon Revisions

| A1 | A2 |  |  |  |

|----|----|--|--|--|

| X  |    |  |  |  |

### 5.2 Fixed Voltage Reference (FVR) Accuracy

At temperatures below -20°C, the output voltage for the FVR may be greater than the level specified in the data sheet. This will apply to all three gain amplifier settings (1X, 2X, 4X). The affected parameter numbers found in the data sheet are: FVR01 (1X gain setting), FVR02 (2X gain setting), and FVR03 (4X gain setting).

### Work around

None.

#### Affected Silicon Revisions

| A1 | A2 |  | 95 |  |  |

|----|----|--|----|--|--|

| X  | X  |  |    |  |  |

### 5.3 Minimum VDD Specifications for LF Devices

VDDMIN at -40°C and +25°C = 2.3V. (See TABLE 37-1: Supply Voltage on the following page for reference.)

### Work around

None.

### Affected Silicon Revisions

|    | A1 | A2 |     |  |  |

|----|----|----|-----|--|--|

| 20 | X  | X  | 2 X |  |  |

#### 5.4 ADC Offset Error

The table containing the Offset Error specification (AD04:EOFF) for the Analog-to-Digital Converter is modified. The updated value for Offset Error specification is +/- 3.0 LSb.

### Work around

None.

### Affected Silicon Revisions

| 20 | A1 | A2 |  |  |  |

|----|----|----|--|--|--|

|    | X  | X  |  |  |  |

# 6. Module: Host Synchronous Serial Port (MSSP)

### 6.1 SSPBUF May Become Corrupted

When operating in SPI Client mode, if the incoming SCK clock signal arrives during any of the conditions below, the SSPBUF transmit shift register may become corrupted. The transmitted client byte cannot be ensured to be correct, and the state of the WCOL bit may or may not indicate a write collision.

These conditions include:

- · A write to an SFR

- · A write to RAM following an SFR read

- · A write to RAM prior to an SFR read

### Work around

### Method 1 (Interrupt Based Using SS):

- Connect the SS line to both the SS input and either an INT or IOC input pin.

- Enable INT or IOC interrupts (interrupt on falling edge if available, otherwise check that SS == 0 when the interrupt occurs).

- 3. Load SSPBUF with the data to be transmitted.

- Continue program execution.

- When the Interrupt Service Routine (ISR) is invoked, do either of the following:

- Add a delay that ensures the first SCK clock will be complete, or

- Poll SSPSTAT.BF (while(BF == 0)) and wait for the transmission/reception to complete.

Once either of these is complete, it is safe to return to program execution.

### Method 2 (Bit Polling Based Using SS):

- 1. Load SSPBUF with the data to be transmitted.

- Poll the SS line and wait for the SS to go active (while(!PORTx.nSS == 0)).

- When SS is active (SS == 0), do either of the following:

- Add a delay that ensures the first SCK clock will be complete, or

- Poll SSPSTAT.BF (while(BF == 0)) and wait for the transmission/reception to complete.

Once one of these two methods is complete, it is safe to return to program execution.

### Method 3 (SS Not Available):

- Load SSPBUF with the data to be transmitted.

- Poll SSPSTAT.BF (while(BF == 0)), and wait for the transmission/reception to complete.

### Affected Silicon Revisions

| A1 | A2 | . 93 |  |  |  |

|----|----|------|--|--|--|

| X  | Х  |      |  |  |  |

### 7. Module: Nonvolatile Memory (NVM)

### 7.1 WRERR Bit Operation

When a Reset is issued while an NVM high-voltage operation is in progress, the WRERR bit in the NVMCON1 register is set as expected. After clearing the WRERR bit, if a Reset reoccurs, the WRERR bit is set again regardless of whether an NVM operation is in progress or not. A successful write operation will clear the WRERR condition.

### Work around

None.

### Affected Silicon Revisions

| A1 | A2 |  |  |  |

|----|----|--|--|--|

| X  | X  |  |  |  |

- 8. Module: Digital-to-Analog (DAC)

- 8.1 FVR as the Positive Voltage Source Is Not Functional in Debug Mode

When using the DAC module while in Debug mode, and selecting the FVR as the positive voltage source, DAC1PSS = 10, the DAC is not functional and unexpected results can be seen on the output.

### Work around

None.

### Affected Silicon Revisions

| A1 | A2 |  |  |  |

|----|----|--|--|--|

| X  | X  |  |  |  |

# 9. Module: Reference Clock Output Module (CLKR)

### 9.1 First Output Pulse of Reference Clock Output Module Is Incorrect When CLKREN Is Enabled

If CLKREN bit is set by the user, the number of input clock cycles taken to generate the reference clock output might vary by one cycle due to a race condition. This condition occurs only if LCx\_out or NCOx\_out are the inputs (CLKRCLK bits) to the CLKR module.

### Work around

Ignore the first output pulse of the CLKR output signal.

### Affected Silicon Revisions

| A1 | A2 | 4: | 23 3 |  |     |  |

|----|----|----|------|--|-----|--|

| X  | Х  |    |      |  | 6 ) |  |

### TABLE 37-1: SUPPLY VOLTAGE

| PIC16LF1      | Stand | Standard Operating Conditions (Unless Otherwise Stated) |                   |       |                   |        |                                                                                          |  |  |

|---------------|-------|---------------------------------------------------------|-------------------|-------|-------------------|--------|------------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Sym.  | Characteristic                                          | Min.              | Typ.† | Max.              | Units  | Conditions                                                                               |  |  |

| D002          | VDD   |                                                         | 1.8<br>2.3<br>2.5 |       | 3.6<br>3.6<br>3.6 | V<br>V | Fosc ≤ 16 MHz, +25°C ≤ Ta ≤ +125°C<br>Fosc ≤ 16 MHz, -40°C ≤ Ta ≤ +25°C<br>Fosc > 16 MHz |  |  |

### **Data Sheet Clarifications**

The following typographic corrections and clarifications are to be noted for the latest version of the device data sheet (DS40001865**D**):

Note: Corrections are shown in **bold**. Where possible, the original bold text formatting has been removed for clarity.

# 1. Module: Table 36.3 Instruction Set Literal Operations

| LITERAL OPERATIONS |   |                             |   |    |      |      |      |          |  |

|--------------------|---|-----------------------------|---|----|------|------|------|----------|--|

| ADDLW              | k | Add literal and W           | 1 | 11 | 1110 | kkkk | kkkk | C, DC, Z |  |

| ANDLW              | k | AND literal with W          | 1 | 11 | 1001 | kkkk | kkkk | Z        |  |

| IORLW              | k | Inclusive OR literal with W | 1 | 11 | 1000 | kkkk | kkkk | Z        |  |

| MOVLB              | k | Move literal to BSR         | 1 | 00 | 0001 | 01kk | kkkk |          |  |

| MOVLP              | k | Move literal to PCLATH      | 1 | 11 | 0001 | 1kkk | kkkk |          |  |

| MOVLW              | k | Move literal to W           | 1 | 11 | 0000 | kkkk | kkkk |          |  |

| SUBLW              | k | Subtract W from literal     | 1 | 11 | 1100 | kkkk | kkkk | C, DC, Z |  |

| XORLW              | k | Exclusive OR literal with W | 1 | 11 | 1010 | kkkk | kkkk | Z        |  |

### 2. Module: Electrical Specifications

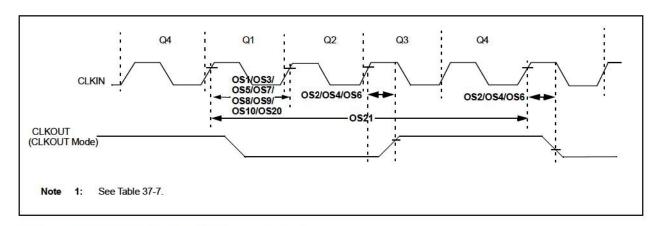

### 2.1 Figure 37-5: Clock Timing

Figure 37-5 incorrectly shows the location of parameters OS1, OS2, OS3, OS4, OS5, OS6, OS7, OS8, OS9, OS10, OS20 and OS21. The correct location for the above-mentioned parameters is depicted in the following figure.

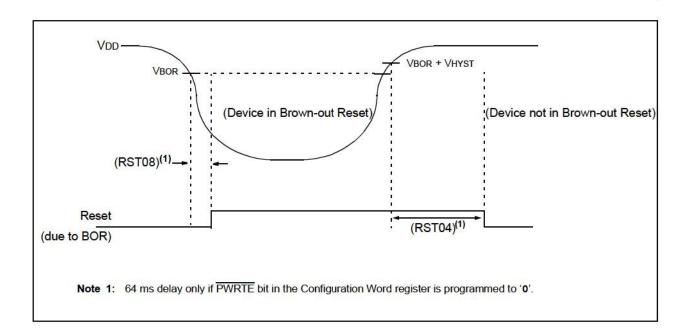

# 2.2 Figure 37-9: Brown-Out Reset Timing and Characteristics

Note 1 in Figure 37-9 is incorrect. The correct note along with the figure is depicted below.

# PIC16(L)F15325/45

# APPENDIX A: DOCUMENT REVISION HISTORY

### **Rev D Document (03/2021)**

Updated Table 2 and 37-1 and Section 5.3 Minimum VDD Specifications. Other minor corrections.

### **Data Sheet Clarifications:**

Added Module 2: Electrical Specifications.

### Rev C Document (11/2020)

Updated Table 2 and Section 5.3 Minimum VDD Specification for LF Devices; Added Table 3 and Section 5.4 ADC Offset Error.

### **Rev B Document (07/2019)**

Updated Table 2, Section 3. Module: Windowed Watchdog Timer (WWDT), Section 5. Module: Electrical Specifications; Added Section 6. Module: Host Synchronous Serial Port (MISSP), Section 8.1 Digital-to-Analog, and Section 9.1 Reference Clock Output Module.

### **Data Sheet Clarifications:**

Added Module 1: Table 36.3 Instruction Set.

### **Rev A Document (12/2016)**

Initial release of this document.

### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are

committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection

feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or

other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUEN-TIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2016-2021, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-7784-6

### Worldwide Sales and Service

### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi. MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

China - Beijing Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

China - Chongqing Tel: 86-23-8980-9588

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

China - Shenyang

Tel: 86-24-2334-2829 China - Shenzhen

Tel: 86-755-8864-2200 China - Suzhou

Tel: 86-186-6233-1526

China - Wuhan Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen Tel: 86-592-2388138

China - Zhuhai Tel: 86-756-3210040

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

Japan - Osaka Tel: 81-6-6152-7160

Japan - Tokyo Tel: 81-3-6880-3770

Korea - Daegu Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

Singapore Tel: 65-6334-8870

Taiwan - Hsin Chu Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

Taiwan - Taipei Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen Tel: 45-4485-5910 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

Germany - Haan Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

Germany - Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

Spain - Madrid Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820