Cypress Semiconductor Corporation, 198 Champion Court, San Jose, CA 95134. Tel: (408) 943-2600

### PRODUCT CHANGE NOTIFICATION

Subject: Qualification of Fab 25 as an Additional Wafer Fab Site and Marketing Part Number

Change for Select Automotive MCU Products

To: FUTURE ELECTRONICS

FUTURE ELE

pcn.system2@future.ca

Change Type: Major

#### **Description of Change:**

Cypress announces the qualification of Fab 25 (5204 East Ben White Boulevard, Austin, TX 78741, USA) as an additional wafer fab site for select automotive MCU products. The current products are fabricated at ON Semiconductor Aizu Co., Ltd. Cypress also announces that the part number is changing from a MB prefix to a CY prefix, including a marking change of "F-logo" or "Spansion logo" removal. These changes include parts of Group 3 (GR3-C) in APCN173705C.

| Changes        | Current                               | New         |

|----------------|---------------------------------------|-------------|

| Wafer Fab Site | ON Semiconductor Aizu Co., Ltd, Japan | Fab 25, USA |

| Part Number    | MB***                                 | CY***       |

| Logo Marking   | F-logo or Spansion logo               | No logo     |

#### **Benefit of Change:**

Qualification of alternate manufacturing sites are part of the ongoing flexible manufacturing initiative announced by Cypress. The goal of the flexible manufacturing initiative is to provide the means for Cypress to continue to meet delivery commitments through dynamic, changing market conditions.

#### Part Numbers Affected: 12

See the attached 'Affected Parts List' file for a list of all part numbers affected by this change. Note that any new parts that are introduced after the publication of this PCN will include all changes outlined in this PCN.

#### **Qualification Status:**

These products have been qualified through a series of tests documented in the Qualification Test Plans summarized in the table below. These qualification reports can be found as attachments to

this PCN or by visiting <u>www.cypress.com</u> and typing the QTP number in the keyword search window.

| QTP Number | Qualification                                                 |

|------------|---------------------------------------------------------------|

| 172504     | Microcontrollers with Flash, 180nmTechnology (CU80F), Fab 25  |

| 184406     | ATJ(former JD) Usuki Fab 25 Qual Report                       |

| 002-29698  | AECQ100 Qual Report - Fab25 180nm Technology (CU80F) Product, |

|            | Grade-1 -40 to 125℃, Grade-2 -40 to 105℃                      |

#### Sample Status:

Qualification samples may not be built ahead of time for all part numbers affected by this change. Please review the attached 'Affected Parts List' file for a list of affected part numbers with their associated Fab25 sample ordering part numbers. Sample ordering part numbers are subject to lead times. If you require qualification samples, please contact your local Cypress sales representative as soon as possible, preferably within 30 days of the date of this PCN, to place any sample orders.

#### **Approximate Implementation Date:**

The MB part numbers listed in attached file will be supported according to the Last Time Buy (LTB) and Last Time Ship (LTS) dates provided. The new Cypress marketing part number part will be open for order entry after the inventory on the MB part is depleted. Your Cypress Sales Representative will be in touch with you during the LTB phase to manage the backlog transition from MB marketing part number to CY marketing part number, depending on inventory depletion levels.

#### **Anticipated Impact:**

Products fabricated at the new site are completely compatible with existing products from form, fit, functional, parametric and quality performance perspectives.

Cypress also recommends that customers take this opportunity to review these changes against current application notes, system design considerations and customer environment conditions to assess impact (if any) to their application.

#### Method of Identification:

Cypress maintains traceability of product to wafer level, including wafer fabrication location, through the lot number marked on the package.

#### **Response Required:**

No response is required.

For additional information regarding this change, contact your local sales representative or contact the PCN Administrator at <a href="mailto:pcn\_adm@cypress.com">pcn\_adm@cypress.com</a>.

Sincerely,

Cypress PCN Administration

# **Cypress Semiconductor Corporation**

CUSTOMER CHARACTERIZATION REPORT FOR CY96340 Series products Cypress FAB25

Design Engineering Vice President Yasuaki Dokko

yasuaki.dokko@cypress.com

Product Engineering Sr Director

Hidetaka Suzuki

hidetaka.suzuki@cypress.com

Product Engineer

Yasuhiro Kurogouchi

yasuhiro.kurogouchi@cypress.com

Applications Engineer

Kazuo Umeno

kazuo.umeno@cypress.com

Marketing Engineering Sr Manager

Toshiya Nishi

toshiya.nishi@cypress.com

www.cypress.com

198 Champion Ct. San Jose, CA 95134 USA

> Tel: (408) 943 2600 Fax: (408) 943 4730

# **CUSTOMER CHARACTERIZATION REPORT FOR CY96340 Series products Cypress FAB25**

# 1.0 Table of Contents

| 1.0 | Table of Contents                                                                                                        | 2              |

|-----|--------------------------------------------------------------------------------------------------------------------------|----------------|

| 2.0 | Introduction                                                                                                             | 3              |

|     | 2.1 General Description 2.2 Pin Assignment 2.3 Datasheet 2.4 Application Notes 2.5 White Papers 2.6 Qualification Report | .4-5<br>6<br>6 |

| 3.0 | Characterization Hardware and Setup                                                                                      | 6              |

|     | 3.1 DC Characterization Board                                                                                            | 6<br>6         |

| 4.0 | DC Characterization                                                                                                      | 7              |

|     | 4.1 DC Characterization Summary                                                                                          | . 7-9          |

| 5.0 | AC Characterization                                                                                                      | 10             |

|     | 5.1 AC Characterization Summary                                                                                          | 10             |

| Doc | ument History Page                                                                                                       | 11             |

# 2.0 Introduction

# 2.1 General Description

CY96340 series is based on Cypress advanced 16FX architecture (16-bit with instruction pipeline for RISC-like performance).

The CPU uses the same instruction set as the established 16LX series - thus allowing for easy migration of 16LX Software to the new 16FX products. 16FX improvements compared to the previous generation include significantly improved performance — even at the same operation frequency, reduced power consumption and faster start-up time.

For highest processing speed at optimized power consumption an internal PLL can be selected to supply the CPU with up to 56MHz operation frequency from an external 4MHz resonator. The result is a minimum instruction cycle time of 17.8ns going together with excellent EMI behavior. An on-chip clock modulation circuit significantly reduces emission peaks in the frequency spectrum. The emitted power is minimized by the on-chip voltage regulator that reduces the internal CPU voltage. A flexible clock tree allows to select suitable operation frequencies for peripheral resources independent of the CPU speed.

# 2.2 Pin Assignment

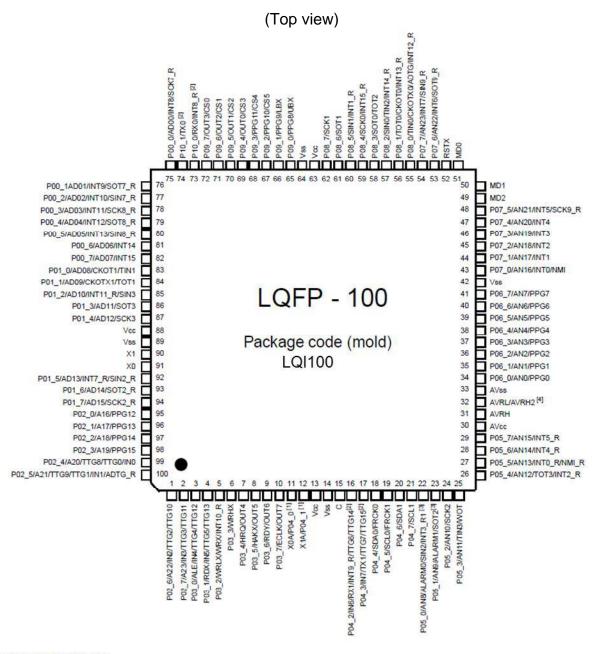

# CY96340 Series (LQI100)

[1]:MB96(F)34xyWy: X0A, X1A MB96(F)34xySy: P04\_0, P04\_1

[2]: TX0, RX0, TX1, RX1 are not available on MB96(F)34xAyy or MB96(F)34xCyy TX1, RX1 are not available on MB96F345Dyy or MB96F345Fyy

[3]: ALARMO, ALARM1 are not available on MB96F345Dyy or MB96F345Fyy

[4]: AVRH2 is not available on MB96F345Dyy or MB96F345Fyy

(LQI100)

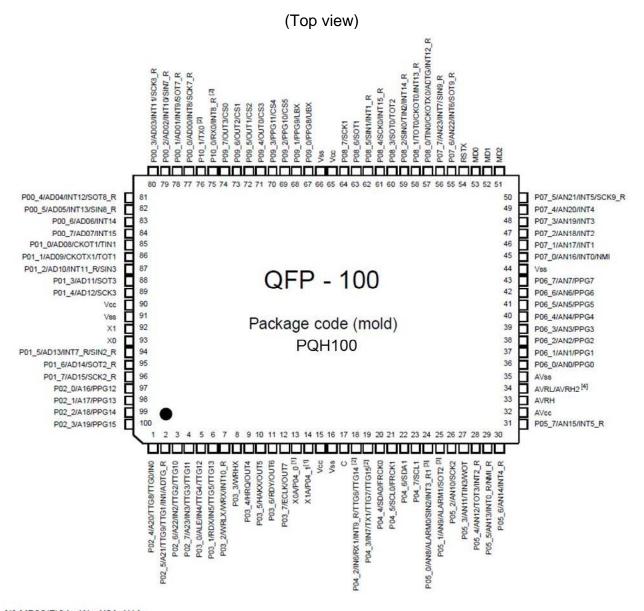

### CY96340 Series (PQH100)

- [1]: MB96(F)34xyWy: X0A, X1A MB96(F)34xySy: P04\_0, P04\_1

- [2]: TX0, RX0, TX1, RX1 are not available on MB96(F)34xAyy or MB96(F)34xCyy TX1, RX1 are not available on MB96F345Dyy or MB96F345Fyy

- [3]: ALARM0, ALARM1 are not available on MB96F345Dyy or MB96F345Fyy

- [4]: AVRH2 is not available on MB96F345Dyy or MB96F345Fyy

(PQH100)

#### 2.3 Datasheet

The datasheet is available from the Cypress Website: <a href="CY96340 Series">CY96340 Series</a>

### 2.4 Application Notes

The application notes are available from the Cypress Website: CY96340 Series

### 2.5 White Papers

CY96340 Series products have no associated White Papers at this time.

# 2.6 Qualification Report

CY96340 Series products are qualified under QTP172504 and QTP173908. The qualification reports are available from the Cypress Website at:

QTP# 172504: Microcontrollers with Flash 180nm Technology (CU80F), Cypress FAB25

QTP# 173908: QTP of JD Usuki standard material LQFP package using Fab25 wafer

# 3.0 Characterization Hardware and Setup

#### 3.1 DC Characterization Board

All critical DC parameters were measured on an engineering samples, with the performance board for specified ATE Tester.

### 3.2 DC Measurement System and Hardware

#### **Temperature Forcing System**

The Thermonics T-2500E Precision Temperature Forcing System was used to force ambient temperature.

#### **ATE Tester**

The Advantest T6573 was used to power the device and measure DC parameters.

#### 3.3 AC Characterization Board

All critical AC parameters were measured on an engineering samples, with the performance board for specified ATE Tester.

### 3.4 AC Measurement System and Hardware

#### **Temperature Forcing System**

The Thermonics T-2500E Precision Temperature Forcing System was used to force ambient temperature.

#### **ATE Tester**

The Advantest T6573 was used to power the device and measure AC parameters.

### 3.5 Characterization Conditions and Parameters

Characterization was done on the following conditions as listed in <u>Table.1</u>. Units were built using standard production manufacturing and chosen randomly unless specified.

Table 1. Characterization Conditions and Parameters

| Parameter | Device                 | Fab Lot | Assy Lot | # of<br>Devices | Voltage Range<br>(V) | Temperature Range (°C) |

|-----------|------------------------|---------|----------|-----------------|----------------------|------------------------|

| DC/AC     | CY96F346RWAPMC-GS-UJE2 | J7423L0 | 1824N04  | 31              | 3.0V-6.0V            | -40, 25, 125           |

(CY96F346 guarantee from T<sub>A</sub>=-40 C to 125 C.)

### 4.0 DC Characterization

# 4.1 DC Characterization Summary

|                       |                  |                |                                                                         | Doto                  | sheet |                          | Meas                     | sured                    |                          |      |

|-----------------------|------------------|----------------|-------------------------------------------------------------------------|-----------------------|-------|--------------------------|--------------------------|--------------------------|--------------------------|------|

| Parameter             | Symbol           | Pin            | Conditions                                                              | Datas                 | Sneet | Curre                    | nt Fab                   | Fal                      | b25                      | Unit |

|                       |                  | Name           |                                                                         | Min                   | Max   | Min                      | Max                      | Min                      | Max                      |      |

|                       | V <sub>OH2</sub> | Normal outputs | $3.0V \le V_{CC} \le 4.5V$<br>$I_{OH} = -1.6mA$                         | V <sub>CC</sub> - 0.5 | -     | V <sub>CC</sub><br>-0.38 | V <sub>CC</sub><br>-0.27 | V <sub>CC</sub><br>-0.41 | V <sub>CC</sub><br>-0.28 | V    |

| Output H<br>voltage   | V <sub>OH5</sub> | Normal outputs | $4.5V \le V_{CC} \le 5.5V$ $I_{OH} = -5mA$                              | V <sub>CC</sub> - 0.5 | -     | V <sub>CC</sub><br>-0.40 | V <sub>CC</sub><br>-0.28 | V <sub>CC</sub><br>-0.48 | V <sub>cc</sub><br>-0.31 | V    |

|                       | V <sub>OH3</sub> | 3mA<br>outputs | $4.5V \le V_{CC} \le 5.5V$ $I_{OH} = -3mA$                              | V <sub>CC</sub> - 0.5 | -     | V <sub>CC</sub><br>-0.38 | V <sub>cc</sub><br>-0.27 | V <sub>cc</sub><br>-0.39 | V <sub>cc</sub><br>-0.27 | ٧    |

|                       | V <sub>OL2</sub> | Normal outputs | $3.0V \le V_{CC} \le 4.5V$<br>$I_{OL} = +1.6mA$                         | -                     | 0.4   | 0.13                     | 0.21                     | 0.11                     | 0.19                     | V    |

| Output L<br>voltage   | $V_{OL5}$        | Normal outputs | $4.5V \le V_{CC} \le 5.5V$ $I_{OL} = +5mA$                              | -                     | 0.4   | 0.16                     | 0.26                     | 0.16                     | 0.29                     | V    |

|                       | V <sub>OL3</sub> | 3mA<br>outputs | $3.0V \le V_{CC} \le 5.5V$ $I_{OL} = +3mA$                              | -                     | 0.4   | 0.12                     | 0.19                     | 0.11                     | 0.18                     | V    |

| Input leak<br>current | I <sub>IL</sub>  | Pnn_m          | $V_{SS} < V_I < V_{CC}$<br>$AV_{SS}$ , $AVRL < V_I < AV_{CC}$ ,<br>AVRH | -1                    | 1     | -0.02                    | 0.02                     | -0.04                    | 0.18                     | μΑ   |

| Pull-up<br>resistance | R <sub>UP</sub>  | Pnn_m,<br>RSTX | V <sub>CC</sub> = 5.5 V                                                 | 25                    | 100   | 33.1                     | 52.4                     | 31.4                     | 51.9                     | kΩ   |

|                   |                                                | Pin             |                                                                                                     |        |     |        |      | Measured                                             |       |      |      |     |     |     |     |    |

|-------------------|------------------------------------------------|-----------------|-----------------------------------------------------------------------------------------------------|--------|-----|--------|------|------------------------------------------------------|-------|------|------|-----|-----|-----|-----|----|

| Parameter         | er Symbol Name Conditions (at T <sub>A</sub> ) |                 |                                                                                                     | sheet  |     | nt Fab |      | b25                                                  | Unit  |      |      |     |     |     |     |    |

|                   |                                                |                 |                                                                                                     |        | Min | Max    | Min  | Max                                                  | Min   | Max  |      |     |     |     |     |    |

|                   |                                                |                 | PLL Run mode with CLKS1/2 = 48MHz, CLKB = CLKP1/2 = 24MHz (CLKRC and CLKSC                          | +25°C  | -   | 44     | 33.8 | 35.4                                                 | 36.0  | 38.2 | mA   |     |     |     |     |    |

|                   |                                                |                 | stopped. Core voltage at 1.9V)                                                                      | +125°C | -   | 47     | 35.6 | 36.8                                                 | 38.6  | 40.8 | mA   |     |     |     |     |    |

|                   | I <sub>CCPLL</sub>                             | $V_{CC}$        | PLL Run mode with CLKS1/2 = CLKB = CLKP1= 56MHz, CLKP2                                              | +25°C  | -   | 57     | 43.2 | 45.6                                                 | 45.4  | 48.6 | mA   |     |     |     |     |    |

|                   | ICOPLL                                         | • 66            | = 28MHz (CLKRC and CLKSC stopped. Core voltage at 1.9V)                                             | +125°C | -   | 60     | 44.8 | 46.6                                                 | 48.2  | 51.0 | mA   |     |     |     |     |    |

|                   |                                                |                 | PLL Run mode with CLKS1/2 = 72MHz, CLKB = CLKP1 = 36MHz, CLKP2 = 18MHz (CLKRC and                   | +25°C  | -   | 50     | 37.8 | 39.6                                                 | 39.8  | 42.6 | mA   |     |     |     |     |    |

| Power supply      |                                                |                 | CLKSC stopped. Core voltage at 1.9V)                                                                | +125°C | -   | 53     | 39.4 | 41.0                                                 | 42.8  | 45.4 | mA   |     |     |     |     |    |

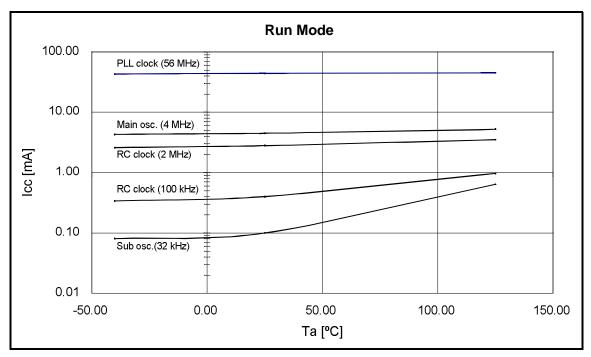

| current in<br>Run | I <sub>CCMAIN</sub>                            | V <sub>CC</sub> | Main Run mode with CLKS1/2 = CLKB = CLKP1/2 = 4MHz                                                  | +25°C  | -   | 5.5    | 4.2  | 4.4                                                  | 4.4   | 4.7  | mA   |     |     |     |     |    |

| modes             | ICCMAIN                                        | VCC             | (CLKPLL, CLKSC and CLKRC stopped)                                                                   | +125°C | -   | 8.5    | 4.9  | 5.1                                                  | 5.8   | 6.8  | mA   |     |     |     |     |    |

|                   | I <sub>CCRCH</sub>                             | V <sub>CC</sub> | RC Run mode with CLKS1/2 = CLKB = CLKP1/2 = 2MHz                                                    | +25°C  | -   | 4      | 2.5  | 2.6                                                  | 2.6   | 2.9  | mA   |     |     |     |     |    |

|                   | TOOKOT                                         | - 00            | (CLKMC, CLKPLL and CLKSC stopped)                                                                   | +125°C | -   | 6.5    | 3.2  | 3.4                                                  | 4.0   | 4.8  | mA   |     |     |     |     |    |

|                   | I <sub>CCRCL</sub>                             | V <sub>cc</sub> | RC Run mode with CLKS1/2 = CLKB = CLKP1/2 = 100kHz, SMCR:LPMS = 1 (CLKMC, CLKPLL and CLKSC stopped. | +25°C  | -   | 0.25   | 0.13 | 0.14                                                 | 0.15  | 0.18 | mA   |     |     |     |     |    |

|                   | ICCRCL                                         | v cc            | Voltage regulator in low power mode, no Flash programming/erasing allowed)                          | +125°C | -   | 3.2    | 0.82 | 0.90                                                 | 1.18  | 1.33 | mA   |     |     |     |     |    |

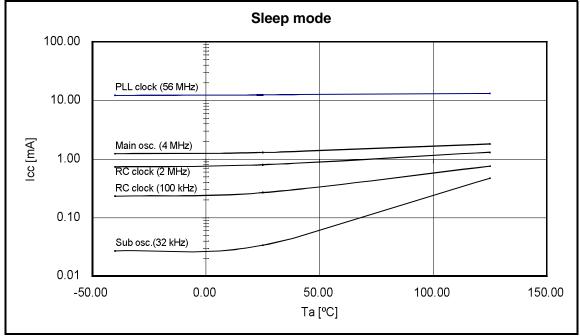

|                   |                                                |                 |                                                                                                     |        |     |        |      | PLL Sleep mode with CLKS1/2 = 48MHz, CLKP1/2 = 24MHz | +25°C | -    | 10.5 | 6.6 | 6.9 | 7.0 | 7.4 | mA |

|                   |                                                |                 | (CLKRC and CLKSC stopped.<br>Core voltage at 1.9V)                                                  | +125°C | -   | 13     | 7.4  | 7.7                                                  | 8.5   | 9.7  | mA   |     |     |     |     |    |

|                   | I <sub>CCSPLL</sub>                            | V <sub>cc</sub> | PLL Sleep mode with CLKS1/2 = CLKP1= 56MHz, CLKP2 = 28MHz                                           | +25°C  | -   | 15.5   | 11.0 | 11.5                                                 | 11.6  | 12.3 | mA   |     |     |     |     |    |

|                   | 000. 22                                        |                 | (CLKRC and CLKSC stopped.<br>Core voltage at 1.9V)                                                  | +125°C | -   | 18     | 12.0 | 12.4                                                 | 13.4  | 14.6 | mA   |     |     |     |     |    |

|                   |                                                |                 | PLL Sleep mode with CLKS1/2 = 72MHz, CLKP1 = 36MHz, CLKP2                                           | +25°C  | -   | 12     | 8.4  | 8.8                                                  | 8.8   | 9.4  | mA   |     |     |     |     |    |

| Power supply      |                                                |                 | = 18MHz (CLKRC and CLKSC stopped. Core voltage at 1.9V)                                             | +125°C | -   | 14.5   | 9.3  | 9.6                                                  | 10.5  | 11.7 | mA   |     |     |     |     |    |

| Sleep             | I <sub>CCSMAIN</sub>                           | V <sub>CC</sub> | Main Sleep mode with CLKS1/2 = CLKP1/2 = 4MHz (CLKPLL,                                              | +25°C  | -   | 1.8    | 1.06 | 1.11                                                 | 1.13  | 1.20 | mA   |     |     |     |     |    |

| modes             |                                                |                 | CLKSC and CLKRC stopped)                                                                            | +125°C | -   | 4.5    | 2.16 | 2.24                                                 | 2.28  | 2.66 | mA   |     |     |     |     |    |

|                   | I <sub>CCSRCH</sub>                            | V <sub>cc</sub> | RC Sleep mode with CLKS1/2 = CLKP1/2 = 2MHz (CLKMC,                                                 | +25°C  | -   | 1.4    | 0.73 | 0.77                                                 | 0.78  | 0.83 | mA   |     |     |     |     |    |

|                   |                                                |                 | CLKPLL and CLKSC stopped)                                                                           | +125°C | -   | 4      | 1.74 | 1.79                                                 | 1.94  | 2.32 | mA   |     |     |     |     |    |

|                   |                                                |                 | RC Sleep mode with CLKS1/2 = CLKP1/2 = 100kHz,<br>SMCR:LPMSS = 1 (CLKMC,                            | +25°C  | -   | 0.15   | 0.03 | 0.04                                                 | 0.05  | 0.07 | mA   |     |     |     |     |    |

|                   | I <sub>CCSRCL</sub> V <sub>CC</sub>            |                 | CLKPLL and CLKSC stopped. Voltage regulator in low power mode)                                      | +125°C | -   | 3      | 0.74 | 0.82                                                 | 1.08  | 1.19 | mA   |     |     |     |     |    |

|                              |                      |                  |                                                                                 |        | Doto | sheet |       |        | ured |      |      |

|------------------------------|----------------------|------------------|---------------------------------------------------------------------------------|--------|------|-------|-------|--------|------|------|------|

| Parameter                    | Symbol               | Pin<br>Name      | Conditions (at T <sub>A</sub> )                                                 |        | Data | sneet | Curre | nt Fab | Fal  | o25  | Unit |

|                              |                      | Ivallie          |                                                                                 |        | Min  | Max   | Min   | Max    | Min  | Max  |      |

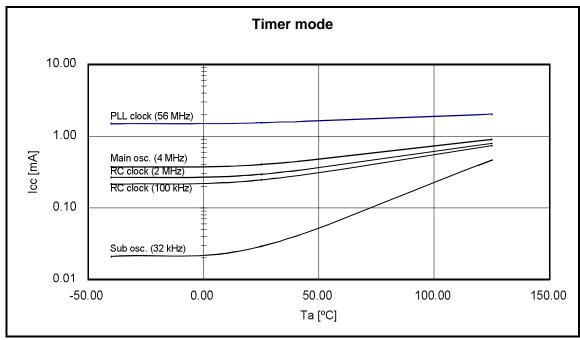

|                              | I <sub>CCTPLL</sub>  | V <sub>CC</sub>  | PLL Timer mode with CLKMC =  4MHz, CLKPLL = 48MHz (CLKRC                        | +25°C  | -    | 2     | 1.37  | 1.44   | 1.50 | 1.65 | mA   |

|                              |                      |                  | and CLKSC stopped. Core voltage at 1.9V)                                        | +125°C | -    | 5     | 2.6   | 2.7    | 2.7  | 3.1  | mA   |

|                              | I <sub>CCTMAIN</sub> | V <sub>cc</sub>  | Main Timer mode with CLKMC = 4MHz, SMCR:LPMSS = 1 (CLKPLL, CLKRC and CLKSC      | +25°C  | -    | 0.15  | 0.05  | 0.06   | 0.07 | 0.09 | mA   |

| Power supply                 | ICC1 MAIN            | V CC             | stopped. Voltage regulator in low power mode)                                   | +125°C | -    | 2.9   | 0.79  | 0.86   | 1.14 | 1.28 | mA   |

| current in<br>Timer<br>modes | Ісствен              | V <sub>CC</sub>  | RC Timer mode with CLKRC = 2MHz, SMCR:LPMSS = 1 (CLKMC, CLKPLL and CLKSC        | +25°C  | -    | 0.15  | 0.06  | 0.07   | 0.08 | 0.09 | mA   |

| modes                        | ICCIRCH              | • 60             | stopped. Voltage regulator in low power mode)                                   | +125°C | -    | 2.9   | 0.79  | 0.87   | 1.15 | 1.29 | mA   |

|                              | I <sub>CCTRCL</sub>  | V <sub>cc</sub>  | RC Timer mode with CLKRC = 100kHz, SMCR:LPMSS = 1 (CLKMC, CLKPLL and CLKSC      | +25°C  | -    | 0.1   | 0.02  | 0.03   | 0.03 | 0.04 | mA   |

|                              | ICCIRCL              | • 60             | stopped. Voltage regulator in low power mode)                                   | +125°C | -    | 2.85  | 0.73  | 0.81   | 1.09 | 1.24 | mA   |

|                              |                      |                  | VRCR:LPMB[2:0] = 110B                                                           | +25°C  | -    | 0.08  | 0.01  | 0.02   | 0.02 | 0.03 | mA   |

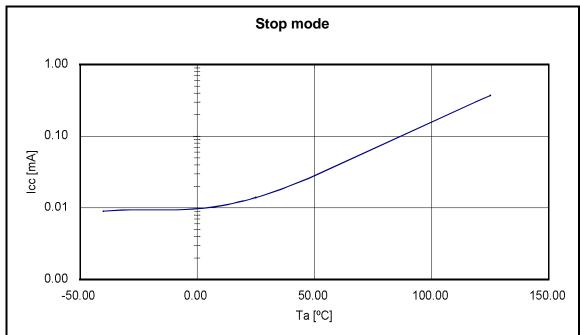

| Power supply                 | I <sub>CCH</sub>     | V <sub>cc</sub>  | (Core voltage at 1.8V)                                                          | +125°C | -    | 2.8   | 0.73  | 0.81   | 1.09 | 1.23 | mA   |

| current in<br>Stop Mode      | ICCH                 | ▼ CC             | VRCR:LPMB[2:0] = 000B                                                           | +25°C  | -    | 0.06  | 0.01  | 0.02   | 0.02 | 0.03 | mA   |

|                              |                      |                  | (Core voltage at 1.2V)                                                          | +125°C | -    | 2.3   | 0.64  | 0.70   | 0.92 | 1.02 | mA   |

| Analog input<br>leakage      | I <sub>AIN</sub>     | Ann              | AV <sub>CC</sub> = 5.5 V,                                                       | +25°C  | -1   | +1    | 0.00  | 0.01   | 0.00 | 0.02 | μΑ   |

| current                      | IAIN                 | 7 1111           | AV <sub>SS</sub> , AVRL < VI < AV <sub>CC</sub> , AVRH                          | +125°C | -3   | +3    | 0.17  | 0.23   | 0.30 | 0.38 | μΑ   |

| Power supply                 | I <sub>A</sub>       | AV <sub>CC</sub> | V <sub>CC</sub> = AV <sub>CC</sub> = AVRH = 5.5 V<br>A/D Converter active       |        | -    | 5     | 1.94  | 2.64   | 2.02 | 2.88 | mA   |

| current                      | I <sub>AH</sub>      | AV <sub>cc</sub> | V <sub>CC</sub> = AV <sub>CC</sub> = AVRH = 5.5 V<br>A/D Converter not operated |        | -    | 5     | 0.02  | 0.23   | 0.02 | 0.28 | μΑ   |

| Reference                    | I <sub>R</sub>       | AVRH/<br>AVRL    | V <sub>CC</sub> = AV <sub>CC</sub> = AVRH = 5.5 V<br>A/D Converter active       |        | -    | 1     | 0.66  | 0.72   | 0.58 | 0.73 | mA   |

| voltage<br>current           | I <sub>RH</sub>      | AVRH/<br>AVRL    | V <sub>CC</sub> = AV <sub>CC</sub> = AVRH = 5.5 V<br>A/D Converter not operated |        | -    | 5     | 0.02  | 0.12   | 0.02 | 0.16 | μΑ   |

# 5.0 AC Characterization

# 5.1 AC Characterization Summary

#### A/D Converter

|                                       | Pi-              |      |                                   | Data                | sheet               |                      |                      | sured                |                      |      |

|---------------------------------------|------------------|------|-----------------------------------|---------------------|---------------------|----------------------|----------------------|----------------------|----------------------|------|

| Parameter                             | Symbol           | Pin  | Conditions                        | Data                | Datasticci          |                      | nt Fab               | Fal                  | o25                  | Unit |

|                                       |                  | Name |                                   | Min                 | Max                 | Min                  | Max                  | Min                  | Max                  |      |

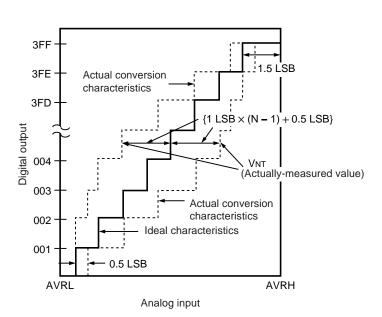

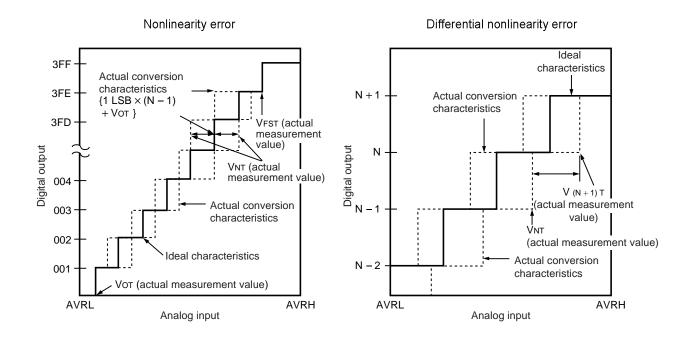

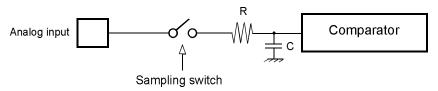

| Nonlinearity error                    | -                | ANn  | $V_{CC} = AV_{CC} = AVRH = 3.0 V$ | -2.5                | +2.5                | -0.77                | 0.41                 | -0.86                | 0.50                 | LSB  |

| Differential<br>nonlinearity<br>error | -                | ANn  | $V_{CC} = AV_{CC} = AVRH = 3.0 V$ | -1.9                | +1.9                | -0.55                | 0.62                 | -0.63                | 0.63                 | LSB  |

| Zero reading voltage                  | V <sub>OT</sub>  | ANn  | $V_{CC} = AV_{CC} = AVRH = 3.0 V$ | AVRL<br>-1.5<br>LSB | AVRL<br>+2.5<br>LSB | AVRL<br>+0.25<br>LSB | AVRL<br>+0.66<br>LSB | AVRL<br>+0.37<br>LSB | AVRL<br>+0.88<br>LSB | V    |

| Full scale<br>reading<br>voltage      | V <sub>FST</sub> | ANn  | $V_{CC} = AV_{CC} = AVRH = 3.0 V$ | AVRH<br>-3.5<br>LSB | AVRH<br>+0.5<br>LSB | AVRH<br>-1.88<br>LSB | AVRH<br>-1.00<br>LSB | AVRH<br>-1.75<br>LSB | AVRH<br>-1.38<br>LSB | V    |

# **Document History Page**

| Rev. | ECN No. | Orig. of Change | Description of Change        |

|------|---------|-----------------|------------------------------|

| **   | 6269831 | YAKU            | New Characterization Report. |

### Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

#### **Products**

PSoC psoc.cypress.com Clocks & Buffers clocks.cypress.com Wireless wireless.cypress.com Memories memory.cypress.com Image Sensors image.cypress.com

#### **PSoC Solutions**

General psoc.cypress.com/solutions Low Power/Low Voltage psoc.cypress.com/low-power Precision Analog psoc.cypress.com/precision-analog LCD Drive psoc.cypress.com/lcd-drive CAN 2.0b psoc.cypress.com/can USB psoc.cypress.com/usb

© Cypress Semiconductor Corporation, 2018. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry eCYodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

All products and company names mentioned in this document may be the trademarks of their respective holders.

# F<sup>2</sup>MC-16FX, CY96340 Series, 16-bit Proprietary Microcontroller Datasheet

CY96340 series is based on Cypress advanced 16FX architecture (16-bit with instruction pipeline for RISC-like performance). The CPU uses the same instruction set as the established 16LX series - thus allowing for easy migration of 16LX Software to the new 16FX products. 16FX improvements compared to the previous generation include significantly improved performance - even at the same operation frequency, reduced power consumption and faster start-up time.

For highest processing speed at optimized power consumption an internal PLL can be selected to supply the CPU with up to 56MHz operation frequency from an external 4MHz resonator. The result is a minimum instruction cycle time of 17.8ns going together with excellent EMI behavior. An on-chip clock modulation circuit significantly reduces emission peaks in the frequency spectrum. The emitted power is minimized by the on-chip voltage regulator that reduces the internal CPU voltage. A flexible clock tree allows to select suitable operation frequencies for peripheral resources independent of the CPU speed.

#### **Features**

#### **Technology**

■ 0.18µm CMOS

#### **CPU**

- F<sup>2</sup>MC-16FX CPU

- Up to 56 MHz internal, 17.8 ns instruction cycle time

- Optimized instruction set for controller applications (bit, byte, word and long-word data types; 23 different addressing modes; barrel shift; variety of pointers)

- 8-byte instruction execution queue

- Signed multiply (16-bit × 16-bit) and divide (32-bit/16-bit) instructions available

#### System clock

- On-chip PLL clock multiplier (x1 x25, x1 when PLL stop)

- 3 MHz 16 MHz external crystal oscillator clock (maximum frequency when using ceramic resonator depends on Q-factor).

- Up to 56 MHz external clock for devices with fast clock input feature

- 32-100 kHz subsystem quartz clock

- 100kHz/2MHz internal RC clock for quick and safe startup, oscillator stop detection, watchdog

- Clock source selectable from main- and subclock oscillator (part number suffix "W") and on-chip RC oscillator, independently for CPU and 2 clock domains of peripherals.

- Low Power Consumption 13 operating modes: (different Run, Sleep, Timer modes, Stop mode)

- Clock modulator

#### On-chip voltage regulator

Internal voltage regulator supports reduced internal MCU voltage, offering low EMI and low power consumption figures

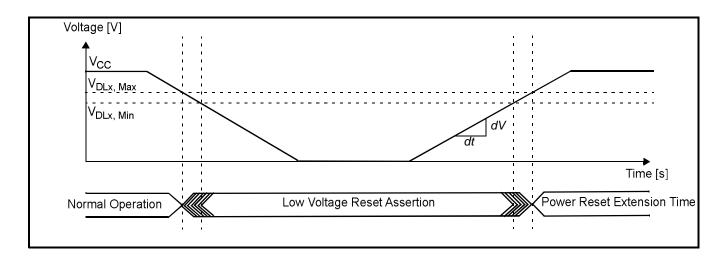

#### Low voltage reset

■ Reset is generated when supply voltage is below minimum

#### **Code Security**

■ Protects ROM content from unintended read-out

#### **Memory Patch Function**

■ Replaces ROM content

■ Can also be used to implement embedded debug support

#### DMA

Automatic transfer function independent of CPU, can be assigned freely to resources

#### Interrupts

- Fast Interrupt processing

- 8 programmable priority levels

- Non-Maskable Interrupt (NMI)

#### **Timers**

- Three independent clock timers (23-bit RC clock timer, 23-bit Main clock timer, 17-bit Sub clock timer)

- Watchdog Timer

#### CAN

- Supports CAN protocol version 2.0 part A and B

- ISO16845 certified

- Bit rates up to 1 Mbit/s

- 32 message objects

- Each message object has its own identifier mask

- Programmable FIFO mode (concatenation of message objects)

- Maskable interrupt

- Disabled Automatic Retransmission mode for Time Triggered CAN applications

- Programmable loop-back mode for self-test operation

#### USART

- Full duplex USARTs (SCI/LIN)

- Wide range of baud rate settings using a dedicated reload timer

- Special synchronous options for adapting to different synchronous serial protocols

- LIN functionality working either as master or slave LIN device

### I<sup>2</sup>C

- Up to 400 kbps

- Master and Slave functionality, 8-bit and 10-bit addressing

**Cypress Semiconductor Corporation**Document Number: 002-04579 Rev. \*B

#### A/D converter

- SAR-type

- 10-bit resolution

- Signals interrupt on conversion end, single conversion mode, continuous conversion mode, stop conversion mode, activation by software, external trigger or reload timer

#### A/D Converter Reference Voltage switch

■ 2 independent positive A/D converter reference voltages available

#### **Reload Timers**

- 16-bit wide

- Prescaler with 1/2<sup>1</sup>, 1/2<sup>2</sup>, 1/2<sup>3</sup>, 1/2<sup>4</sup>, 1/2<sup>5</sup>, 1/2<sup>6</sup> of peripheral clock frequency

- Event count function

#### Free Running Timers

■ Signals an interrupt on overflow, supports timer clear upon match with Output Compare (0, 4), Prescaler with 1, 1/2¹, 1/2², 1/2³, 1/2⁴, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2⁵, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°, 1/2°,

#### **Input Capture Units**

- 16-bit wide

- Signals an interrupt upon external event

- Rising edge, falling edge or rising & falling edge sensitive

#### **Output Compare Units**

- 16-bit wide

- Signals an interrupt when a match with 16-bit I/O Timer occurs

- A pair of compare registers can be used to generate an output signal.

#### **Programmable Pulse Generator**

- 16-bit down counter, cycle and duty setting registers

- Interrupt at trigger, counter borrow and/or duty match

- PWM operation and one-shot operation

- Internal prescaler allows 1, 1/4, 1/16, 1/64 of peripheral clock as counter clock and Reload timer overflow as clock input

- Can be triggered by software or reload timer

#### **Real Time Clock**

- Can be clocked either from sub oscillator (devices with part number suffix "W"), main oscillator or from the RC oscillator

- Facility to correct oscillation deviation of Sub clock or RC oscillator clock (clock calibration)

- Read/write accessible second/minute/hour registers

- Can signal interrupts every half second/second/minute/hour/day

- Internal clock divider and prescaler provide exact 1s clock

#### **External Interrupts**

- Edge sensitive or level sensitive

- Interrupt mask and pending bit per channel

- Each available CAN channel RX has an external interrupt for wake-up

- Selected USART channels SIN have an external interrupt for wake-up

#### Non Maskable Interrupt

■ Disabled after reset

- Once enabled, can not be disabled other than by reset.

- Level high or level low sensitive

- Pin shared with external interrupt 0.

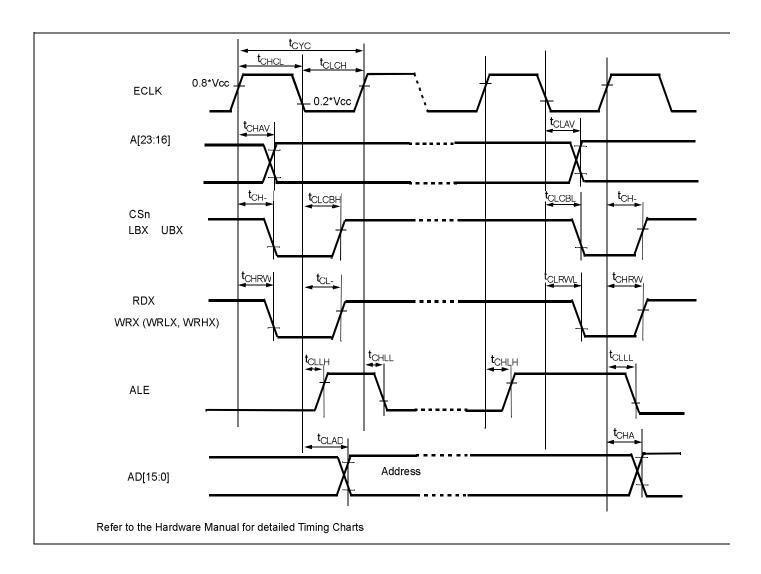

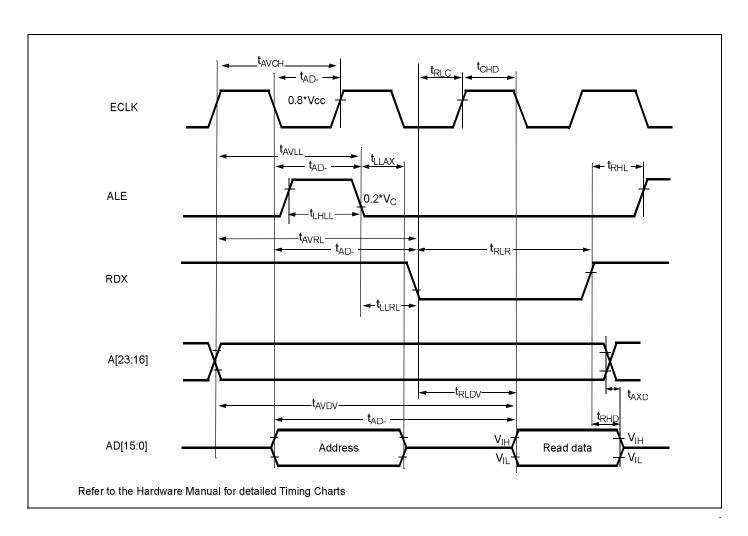

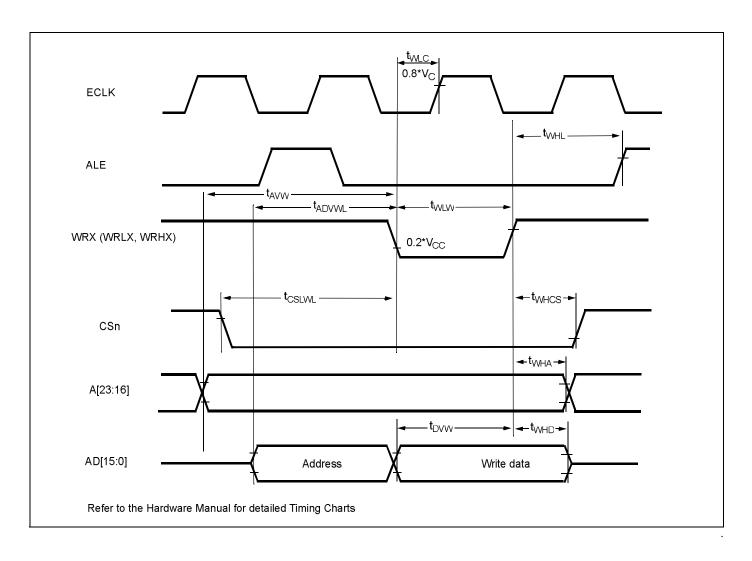

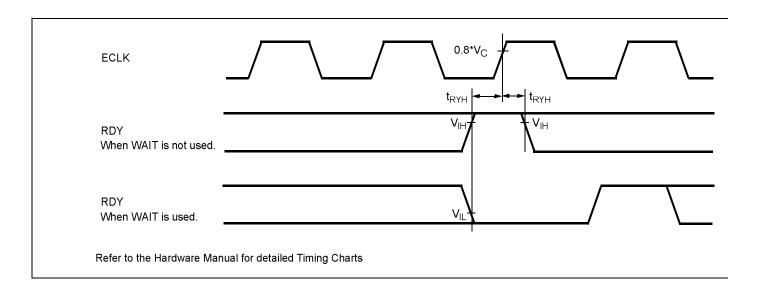

#### **External bus interface**

- 8-bit or 16-bit bidirectional data

- Up to 24-bit addresses

- 6 chip select signals

- Multiplexed address/data lines

- Wait state request

- External bus master possible

- Timing programmable

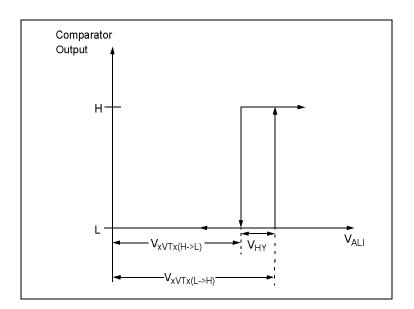

#### Alarm comparator

- Monitors an external voltage and generates an interrupt in case of a voltage lower or higher than the defined thresholds

- Threshold voltages defined externally or generated internally

- Status is readable, interrupts can be masked separately

#### I/O Ports

- Virtually all external pins can be used as general purpose I/O

- All push-pull outputs (except when used as I2C SDA/SCL line)

- Bit-wise programmable as input/output or peripheral signal

- Bit-wise programmable input enable

- Bit-wise programmable input levels: Automotive / CMOS-Schmitt trigger / TTL (TTL levels not supported by all devices)

- Bit-wise programmable pull-up resistor

- Bit-wise programmable output driving strength for EMI optimization

#### **Packages**

■ 100-pin plastic QFP and LQFP

#### Flash Memory

- Supports automatic programming, Embedded Algorithm

- Write/Erase/Erase-Suspend/Resume commands

- A flag indicating completion of the algorithm

- Number of erase cycles: 10,000 times

- Data retention time: 20 years

- Erase can be performed on each sector individually

- Sector protection

- Flash Security feature to protect the content of the Flash

- Low voltage detection during Flash erase

#### **Contents**

| Product Lineup                                             | 4   |

|------------------------------------------------------------|-----|

| Block Diagram                                              | 6   |

| Pin Assignments                                            | 7   |

| Pin Function Description                                   | 9   |

| Pin Circuit Type                                           | 11  |

| I/O Circuit Type                                           | 12  |

| Memory Map                                                 | 15  |

| User ROM Memory Map For Flash Devices                      | 17  |

| User ROM Memory Map for Mask ROM Devices                   | 20  |

| Serial Programming Communication Interface                 | 21  |

| I/O Map                                                    | 22  |

| Interrupt Vector Table                                     | 49  |

| Handling Devices                                           | 53  |

| Latch-up prevention                                        | 53  |

| Unused pins handling                                       | 53  |

| External clock usage                                       | 53  |

| Unused sub clock signal                                    | 54  |

| Notes on PLL clock mode operation                          | 54  |

| Power supply pins (VCC/VSS)                                | 54  |

| Crystal oscillator and ceramic resonator circuit           | 55  |

| Turn on sequence of power supply to A/D converter a inputs |     |

| Pin handling when not using the A/D converter              | 55  |

| Notes on Power-on                                          | 55  |

| Stabilization of power supply voltage                      | 55  |

| Serial communication                                       | 55  |

| Handling of Data Flash                                     | 55  |

| Electrical Characteristics                                 | 56  |

| Absolute Maximum Ratings                                   | 56  |

| Recommended Operating Conditions                           | 58  |

| DC characteristics                                         | 59  |

| AC Characteristics                                         | 68  |

| Analog Digital Converter                                   | 86  |

| Alarm Comparator                                           | 90  |

| Low Voltage Detector Characteristics                       |     |

| Flash Memory Program/erase Characteristics                 | 94  |

| Example Characteristics                                    |     |

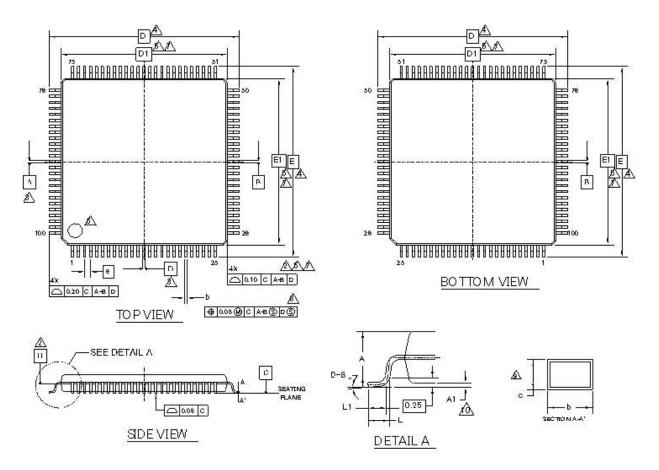

| Package Dimension CY96(F)34x LQFP 100P                     |     |

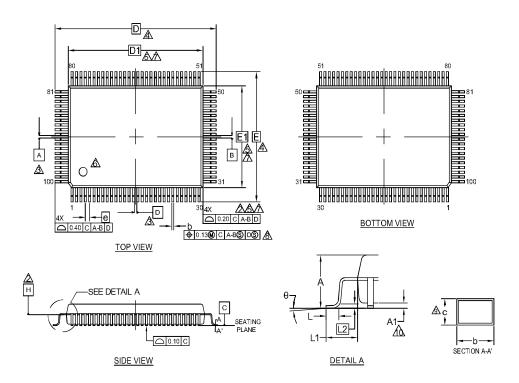

| Package Dimension CY96(F)34x QFP 100P                      |     |

| Ordering Information                                       |     |

| MCU with CAN Controller                                    |     |

| MCU without CAN Controller                                 |     |

| Major Changes                                              |     |

| Revision History                                           | 108 |

# 1. Product Lineup

| Features                                         | Features |                                           | CY96(F)34x                                                                    |  |  |  |

|--------------------------------------------------|----------|-------------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| Product type                                     |          | Evaluation sample                         | Flash product: CY96F34x Mask ROM product: CY9634x                             |  |  |  |

| Product options                                  |          |                                           |                                                                               |  |  |  |

| YS                                               |          |                                           | Low voltage reset persistently on / Single clock                              |  |  |  |

| RS                                               |          |                                           | Low voltage reset can be disabled / Single clock                              |  |  |  |

| YW                                               |          |                                           | Low voltage reset persistently on / Dual clock                                |  |  |  |

| RW                                               |          |                                           | Low voltage reset can be disabled / Dual clock                                |  |  |  |

| TS                                               |          |                                           | indep. 32KB Flash / Low voltage reset persistently on / Single clock          |  |  |  |

| HS                                               |          |                                           | indep. 32KB Flash / Low voltage reset can be disabled / Single clock          |  |  |  |

| TW                                               |          |                                           | indep. 32KB Flash / Low voltage reset persistently on / Dual clock            |  |  |  |

| HW                                               |          | NIA                                       | indep. 32KB Flash / Low voltage reset can be disabled / Dual clock            |  |  |  |

| FS                                               |          | NA NA                                     | 64KB Data Flash / Low voltage reset persistently on / Single clock            |  |  |  |

| DS                                               |          |                                           | 64KB Data Flash / Low voltage reset can be disabled / Single clock            |  |  |  |

| FW                                               |          |                                           | 64KB Data Flash / Low voltage reset persistently on / Dual clock              |  |  |  |

| DW                                               |          |                                           | 64KB Data Flash / Low voltage reset can be disabled / Dual clock              |  |  |  |

| AS                                               |          |                                           | No CAN / Low voltage reset can be disabled / Single clock devices             |  |  |  |

| CS                                               |          |                                           | No CAN / indep. 32KB Flash / Low voltage reset can be disabled / Single clock |  |  |  |

| AW                                               |          |                                           | No CAN / Low voltage reset can be disabled / Dual clock                       |  |  |  |

| cw                                               |          |                                           | No CAN / indep. 32KB Flash / Low voltage reset can be disabled / Dual clock   |  |  |  |

| Flash/ROM                                        | RAM      |                                           |                                                                               |  |  |  |

| 160KB                                            | 8KB      |                                           | CY96345Y, CY96345R                                                            |  |  |  |

| 224KB<br>[Flash A: 160KB, Data<br>Flash A: 64KB] | 8KB      |                                           | CY96F345F, CY96F345D                                                          |  |  |  |

| 288KB                                            | 16KB     | ROM/Flash memory<br>emulation by external | CY96F346Y, CY96346Y, CY96F346R, CY96F346A                                     |  |  |  |

| 416KB                                            | 16KB     | RAM, 92KB internal<br>RAM                 | CY96F347Y, CY96F347R, CY96F347A                                               |  |  |  |

| 544KB                                            | 24KB     |                                           | CY96F348Y, CY96F348R, CY96F348A                                               |  |  |  |

| 576KB<br>[Flash A: 544KB, Flash<br>B: 32KB]      | 24KB     |                                           | CY96F348T, CY96F348H, CY96F348C                                               |  |  |  |

| Package                                          |          | BGA416                                    | LQI100 PQH100                                                                 |  |  |  |

| DMA                                              |          | 16 channels                               | 6 channels                                                                    |  |  |  |

| USART                                            |          | 10 channels                               | 7 channels                                                                    |  |  |  |

| Features                               | CY96V300B                                                                                              | CY96(F)34x                                                             |  |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|

| l <sup>2</sup> C                       | 2 channels                                                                                             | 2 channels                                                             |  |  |  |

| A/D Converter                          | 40 channels                                                                                            | 24 channels                                                            |  |  |  |

| A/D Converter Reference Voltage switch | yes                                                                                                    | yes (except CY96F345Dyy or CY96F345Fyy)                                |  |  |  |

| 16-bit Reload Timer                    | 6 channels + 1<br>channel (for PPG)                                                                    | 4 channels + 1 channel (for PPG)                                       |  |  |  |

| 16-bit Free-Running Timer              | 4 channels                                                                                             | 2 channels                                                             |  |  |  |

| 16-bit Output Compare                  | 12 channels                                                                                            | 8 channels                                                             |  |  |  |

| 16-bit Input Capture                   | 12 channels                                                                                            | 8 channels                                                             |  |  |  |

| 16-bit Programmable Pulse<br>Generator | 20 channels                                                                                            | 16 channels                                                            |  |  |  |

| CAN Interface                          | CY96(F)34xAyy or CY96(F)34xCyy: no 5 channels CY96F345Dyy or CY96F345Fyy: 1 channel others: 2 channels |                                                                        |  |  |  |

| External Interrupts                    |                                                                                                        | 16 channels                                                            |  |  |  |

| Non-Maskable Interrupt                 |                                                                                                        | 1 channel                                                              |  |  |  |

| Real Time Clock                        |                                                                                                        | 1                                                                      |  |  |  |

| I/O Ports                              | 136                                                                                                    | 80 for part number with suffix "W", 82 for part number with suffix "S" |  |  |  |

| Alarm comparator                       | 2 channels                                                                                             | CY96F345Dyy or CY96F345Fyy: no<br>others: 2 channels                   |  |  |  |

| External bus interface                 | Yes Yes (multiplexed address/data)                                                                     |                                                                        |  |  |  |

| Chip select                            | 6 signals                                                                                              |                                                                        |  |  |  |

| Clock output function                  | 2 channels                                                                                             |                                                                        |  |  |  |

| Low voltage reset                      |                                                                                                        | Yes                                                                    |  |  |  |

| On-chip RC-oscillator                  |                                                                                                        | Yes                                                                    |  |  |  |

# 2. Block Diagram

AD00 ... AD15 CKOT0, CKOT1 A16 ... A23 ALE RDX CKOTX0, CKOTX1 X0, X1 WR(L)X, WRHX X0A, X1A<sup>[1]</sup> ◀ WR(L)X, WF HRQ HAKX RDY ECLK LBX, UBX CS0 ... CS5 **RSTX** MD0...MD2 NMI, NMI R Memory Patch Flash Memory B or Data Flash A <sup>[2</sup> External Bus 16FX Interrupt Flash Clock & Uńit Interface CPÚ Controller Memory A Mode Controller 16FX Core Bus (CLKB) Voltage DMA Peripheral Peripheral Watchdog **RAM** Boot ROM Regulator Controller Bus Bridge Bus Bridge Bus 2 (CLKP2) SDA0, SDA1 ◀▶ I2C 2 ch. SCL0, SCL1 CAN - TX0, TX1 <sup>[3]</sup> Peripheral Interface RX0. RX1<sup>[3]</sup> 2 ch AVRH AVRL/AVRH2 [5] 10-bit ADC 24 ch. ANO ... AN23 (CLKP1) ADTG, ADTG\_R TIN0 ... TIN3 -16-bit Reload Bus SIN0...SIN3, SIN2\_R, SIN7\_R...SIN9\_R SOT0...SOT3, SOT2\_R, SOT7\_R...SOT9\_R SCK0...SCK3, SCK2\_R, SCK7\_R...SCK9\_R Timer **USART** TOT0 ... TOT3 **◄** heral 7 ch. FRCK0 IN0 ... IN3 OUT0 ... OUT3 I/O Timer 0 Periph ICU 0/1/2/3 ALARMO<sup>[4]</sup> Alarm OCU 0/1/2/3 Comparator ALARM1 [4] 2 ch. FRCK1 -IN4 ... IN7 -OUT4 ... OUT7 -I/O Timer 1 ICU 4/5/6/7 16-bit PPG TTG0 ... TTG15 OCU 4/5/6/7 16 ch. PPG0 ... PPG15 RLT6 INT0 ... INT15 ---INTO R ... INT2 R-External INT4\_R, INT5\_R-Real Time WOT Interrupt Clock INT7\_R ... INT15\_R INT3 R1-[1]: X0A, X1A only available on CY96(F)34xyWy [2]: Flash B only available on CY96F34xCyy, CY96F34xHyy or CY96F34xTyy Data Flash A only available on CY96F34xDyy or CY96F34xFyy [3]: CAN interfaces are not available on CY96(F)34xAyy or CY96(F)34xCyy CAN1 is not available on CY96F345Dyy or CY96F345Fyy [4]: Alarm comparator is not available on CY96F345Dyy or CY96F345Fyy [5]: A/D converter reference voltage switch is not available on CY96F345Dyy or CY96F345Fyy

Figure 1. Block diagram of CY96(F)34x

# 3. Pin Assignments

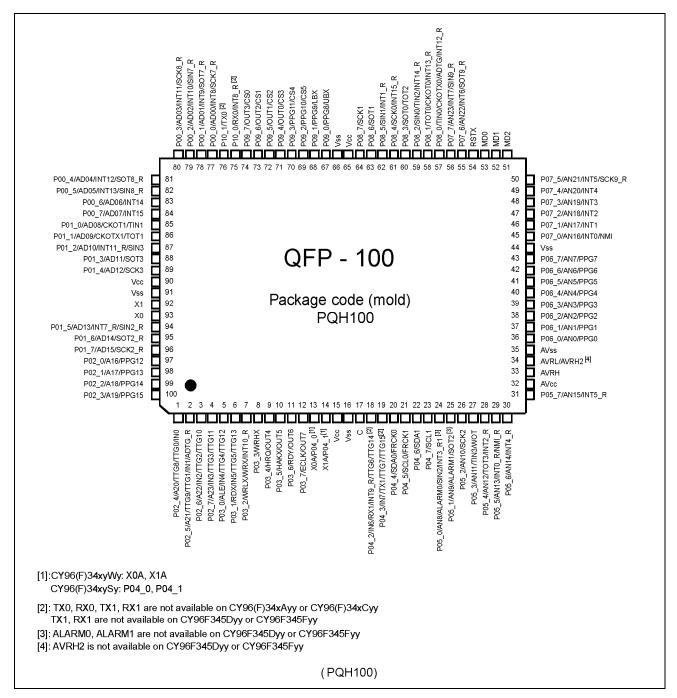

Figure 2. Pin assignment of CY96(F)34x (PQH100)

#### Remark:

CY96(F)34x products are pin-compatible to F<sup>2</sup>MC-16LX family CY90340 series.

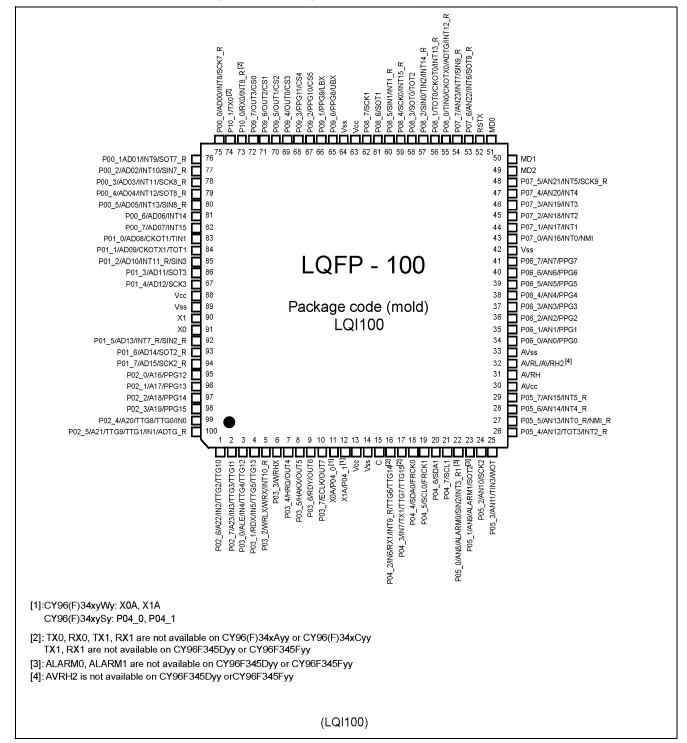

Figure 3. Pin assignment of CY96(F)34x (LQI100)

#### Remark:

CY96(F)34x products are pin-compatible to F<sup>2</sup>MC-16LX family CY90340 series.

# 4. Pin Function Description

**Table 1: Pin Function description**

| Pin name         | Feature               | Description                                                                    |  |  |

|------------------|-----------------------|--------------------------------------------------------------------------------|--|--|

| ADn              | External bus          | External bus interface (multiplexed mode) address output and data input/output |  |  |

| ADTG             | ADC                   | A/D converter trigger input                                                    |  |  |

| ADTG_R           | ADC                   | Relocated A/D converter trigger input                                          |  |  |

| ALARMn           | Alarm comparator      | Alarm Comparator n input                                                       |  |  |

| ALE              | External bus          | External bus Address Latch Enable output                                       |  |  |

| An               | External bus          | External bus address output                                                    |  |  |

| ANn              | ADC                   | A/D converter channel n input                                                  |  |  |

| AV <sub>CC</sub> | Supply                | Analog circuits power supply                                                   |  |  |

| AVRH             | ADC                   | A/D converter high reference voltage input                                     |  |  |

| AVRH2            | ADC                   | Alternative A/D converter high reference voltage input                         |  |  |

| AVRL             | ADC                   | A/D converter low reference voltage input                                      |  |  |

| AV <sub>SS</sub> | Supply                | Analog circuits power supply                                                   |  |  |

| С                | Voltage regulator     | Internally regulated power supply stabilization capacitor pin                  |  |  |

| CKOTn            | Clock output function | Clock Output function n output                                                 |  |  |

| CKOTXn           | Clock output function | Clock Output function n inverted output                                        |  |  |

| ECLK             | External bus          | External bus clock output                                                      |  |  |

| CSn              | External bus          | External bus chip select n output                                              |  |  |

| FRCKn            | Free Running Timer    | Free Running Timer n input                                                     |  |  |

| HAKX             | External bus          | External bus Hold Acknowledge                                                  |  |  |

| HRQ              | External bus          | External bus Hold Request                                                      |  |  |

| INn              | ICU                   | Input Capture Unit n input                                                     |  |  |

| INTn             | External Interrupt    | External Interrupt n input                                                     |  |  |

| INTn_R           | External Interrupt    | Relocated External Interrupt n input                                           |  |  |

| LBX              | External bus          | External Bus Interface Lower Byte select strobe output                         |  |  |

| MDn              | Core                  | Input pins for specifying the operating mode.                                  |  |  |

| NMI              | External Interrupt    | Non-Maskable Interrupt input                                                   |  |  |

| NMI_R            | External Interrupt    | Relocated Non-Maskable Interrupt input                                         |  |  |

| OUTn             | ocu                   | Output Compare Unit n waveform output                                          |  |  |

| Pxx_n            | GPIO                  | General purpose IO                                                             |  |  |

| PPGn             | PPG                   | Programmable Pulse Generator n output                                          |  |  |

| RDX              | External bus          | External bus interface read strobe output                                      |  |  |

**Table 1: Pin Function description**

| Pin name        | Feature      | Description                                                   |

|-----------------|--------------|---------------------------------------------------------------|

| RDY             | External bus | External bus interface external wait state request input      |

| RSTX            | Core         | Reset input                                                   |

| RXn             | CAN          | CAN interface n RX input                                      |

| SCKn            | USART        | USART n serial clock input/output                             |

| SCKn_R          | USART        | Relocated USART n serial clock input/output                   |

| SCLn            | I2C          | I <sup>2</sup> C interface n clock I/O input/output           |

| SDAn            | I2C          | I <sup>2</sup> C interface n serial data I/O input/output     |

| SINn            | USART        | USART n serial data input                                     |

| SINn_R          | USART        | Relocated USART n serial data input                           |

| SOTn            | USART        | USART n serial data output                                    |

| SOTn_R          | USART        | Relocated USART n serial data output                          |

| TINn            | Reload Timer | Reload Timer n event input                                    |

| TOTn            | Reload Timer | Reload Timer n output                                         |

| TTGn            | PPG          | Programmable Pulse Generator n trigger input                  |

| TXn             | CAN          | CAN interface n TX output                                     |

| UBX             | External bus | External Bus Interface Upper Byte select strobe output        |

| V <sub>CC</sub> | Supply       | Power supply                                                  |

| $V_{SS}$        | Supply       | Power supply                                                  |

| WOT             | RTC          | Real Timer clock output                                       |

| WRHX            | External bus | External bus High byte write strobe output                    |

| WRLX/WRX        | External bus | External bus Low byte / Word write strobe output              |

| X0              | Clock        | Oscillator input                                              |

| XOA             | Clock        | Subclock Oscillator input (only for devices with suffix "W")  |

| X1              | Clock        | Oscillator output                                             |

| X1A             | Clock        | Subclock Oscillator output (only for devices with suffix "W") |

# 5. Pin Circuit Type

Table 2: Pin circuit types

| LQI      | LQI100                         |           | H100                           |

|----------|--------------------------------|-----------|--------------------------------|

| Pin no.  | Circuit<br>type <sup>[1]</sup> | Pin no.   | Circuit<br>type <sup>[1]</sup> |

| 1-10     | Н                              | 1-12      | Н                              |

| 11,12    | B <sup>[2]</sup>               | 13, 14    | B [2]                          |

| 11,12    | H <sup>[3]</sup>               | 13, 14    | H <sup>[3]</sup>               |

| 13,14    | Supply                         | 15,16     | Supply                         |

| 15       | F                              | 17        | F                              |

| 16,17    | Н                              | 18,19     | Н                              |

| 18-21    | N                              | 20-23     | N                              |

| 22-29    | I                              | 24-31     | I                              |

| 30       | Supply                         | 32        | Supply                         |

| 31-32    | G                              | 33-34     | G                              |

| 33       | Supply                         | 35        | Supply                         |

| 34 to 41 | I                              | 36 to 43  | I                              |

| 42       | Supply                         | 44        | Supply                         |

| 43 to 48 | I                              | 45 to 50  | I                              |

| 49 to 51 | С                              | 51 to 53  | С                              |

| 52       | E                              | 54        | E                              |

| 53 to 54 | I                              | 55 to 56  | I                              |

| 55 to 62 | Н                              | 57 to 64  | Н                              |

| 63, 64   | Supply                         | 65, 66    | Supply                         |

| 65 to 87 | Н                              | 67 to 89  | Н                              |

| 88,89    | Supply                         | 90, 91    | Supply                         |

| 90, 91   | А                              | 92, 93    | A                              |

| 92-100   | Н                              | 94 to 100 | Н                              |

<sup>[1]:</sup> Please refer to " I/O Circuit Type" for details on the I/O circuit types [2]: Devices with suffix "W"  $\,$

<sup>[3]:</sup> Devices without suffix "W"

# 6. I/O Circuit Type

| Туре | Circuit                             | Remarks                                                                                                                                                                                                                                                                                                                                                       |

|------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

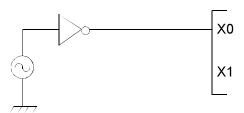

| A    | X1 O Xout  FCI or osc disable       | High-speed oscillation circuit:  Programmable between oscillation mode (external crystal or resonator connected to X0/X1 pins) and Fast external Clock Input (FCI) mode (external clock connected to X0 pin)  Programmable feedback resistor = approx. 2 * 0.5 MΩ. Feedback resistor is grounded in the center when the oscillator is disabled or in FCI mode |

| В    | X1A Xout  SRFBE  Osc disable        | Low-speed oscillation circuit:  ■ Programmable feedback resistor = approx. 2 * 5 MΩ. Feedback resistor is grounded in the center when the oscillator is disabled                                                                                                                                                                                              |

| С    | R<br>Hysteresis<br>inputs           | ■ Mask ROM and EVA device:CMOS Hysteresis input pin ■ Flash device:CMOS input pin                                                                                                                                                                                                                                                                             |

| Е    | Pull-up Resistor  Hysteresis inputs | ■ CMOS Hysteresis input pin ■ Pull-up resistor value: approx. 50 kΩ                                                                                                                                                                                                                                                                                           |

| Туре | Circuit                                                                                                                                                                                  | Remarks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

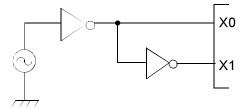

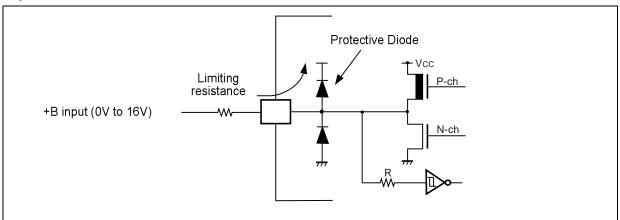

| F    |                                                                                                                                                                                          | ■ Power supply input protection circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| G    | ANE AVR                                                                                                                                                                                  | <ul> <li>A/D converter ref+ (AVRH/AVRH2) power supply input pin with protection circuit</li> <li>Flash devices do not have a protection circuit against VCC for pins AVRH/AVRH2</li> <li>Devices without AVRH reference switch do not have an analog switch for the AVRL pin</li> </ul>                                                                                                                                                                                                                             |

| Н    | Standby control for input shutdown TTL input | <ul> <li>■ CMOS level output (programmable I<sub>OL</sub> = 5mA, I<sub>OH</sub> = -5mA and I<sub>OL</sub> = 2mA, I<sub>OH</sub> = -2mA)</li> <li>■ 2 different CMOS hysteresis inputs with input shutdown function *</li> <li>■ Automotive input with input shutdown function *</li> <li>■ TTL input with input shutdown function *</li> <li>■ Programmable pull-up resistor: 50kΩ approx.</li> <li>*CY96F345Dyy or CY96F345Fyy: Only Automotive input and CMOS hysteresis input (0.7/0.3) are supported</li> </ul> |

| Туре | Circuit                                                                                                                                                                                  | Remarks                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I    | Pull-up control                                                                                                                                                                          | <ul> <li>■ CMOS level output (programmable I<sub>OL</sub> = 5mA, I<sub>OH</sub> = -5mA and I<sub>OL</sub> = 2mA, I<sub>OH</sub> = -2mA)</li> <li>■ 2 different CMOS hysteresis inputs with input shutdown function *</li> </ul>                                                                                                                                                            |